Beruflich Dokumente

Kultur Dokumente

Lecture 400 - Oversampling Adcs - Part Ii

Hochgeladen von

Vincy VargheseOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Lecture 400 - Oversampling Adcs - Part Ii

Hochgeladen von

Vincy VargheseCopyright:

Verfügbare Formate

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-1

CMOS Analog Circuit Design P.E. Allen - 2010

LECTURE 400 OVERSAMPLING ADCS PART II

LECTURE ORGANIZATION

Outline

Implementation of modulators

Decimation and filtering

Bandpass modulators

Digital-analog oversampling converters

Summary

CMOS Analog Circuit Design, 2

nd

Edition Reference

Pages 705-715

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-2

CMOS Analog Circuit Design P.E. Allen - 2010

IMPLEMENTATION OF MODULATORS

Modulators The Analog Part of the Oversampling ADC

Most of todays delta-sigma modulators use fully differential switched capacitor circuits.

Advantages are:

Doubles the signal swing and increases the dynamic range by 6dB

Common-mode signals that may couple to the signal through the supply lines and

substrate are canceled

Charge injected by the switches are canceled to a first-order

Example:

First integrator

dissipates the most

power and requires the

most accuracy.

Fig.10.9-24

YB

Y

-

+

0.5z

-1

1 - z

-1

-

+

0.5z

-1

1 - z

-1

+

+

X Y

Q

1

+

-

V

Ref

+

1d

1d

Y YB

2

V

Ref

+

V

Ref

-

V

Ref

-

2C

2C

C

C

1d

1d

Y YB

V

Ref

+

Y YB

V

Ref

-

1

V

Ref

+

V

Ref

-

Y YB

+

-

2

2C

2C

C

C

1

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-3

CMOS Analog Circuit Design P.E. Allen - 2010

1.5V, 1mW, 98db Analog-Digital Converter

a

1

z - 1

b

1

a

2

z - 1

b

2

a

3

z - 1

a

4

z - 1

1-bit

A/D

1-bit

D/A

E

y

4

Y

y

3

y

2

y

1

X

Fig. 10.10-06

where a

1

= 1/3, a

2

= 3/25, a

3

= 1/10, a

4

= 1/10, b

1

= 6/5, b

2

= 1 and = 1/6

Advantages:

The modulator combines the advantages of both DFB and DFF type modulators:

Only four op amps are required. The 1st integrators output swing is between V

REF

for large input signal amplitudes (0.6V

REF

), even if the integrator gain is large (0.5).

A local resonator is formed by the feedback around the last two integrators to further

suppress the quantization noise.

The modulator is fully pipelined for fast settling.

A.L. Coban and P.E. Allen, A 1.5V, 1mW Audio Modulator with 98dB Dynamic Range, Proc. of 1999 Int. Solid-State Circuits Conf., Feb.

1999, pp. 50-51.

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-4

CMOS Analog Circuit Design P.E. Allen - 2010

1.5V, 1mW, 98dB Analog-Digital Converter - Continued

Integrator power dissipation vs. integrator gain

DR = 98 dB

BW = 20 kHz

C

s

= 5 pF

0.5 m CMOS

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-5

CMOS Analog Circuit Design P.E. Allen - 2010

1.5V, 1mW, 98db Analog-Digital Converter - Continued

Modulator power dissipation vs. oversampling ratio

Suppy

Voltage (V)

DR = 98 dB

BW = 20 kHz

Integrator gain = 1/3

0.5m CMOS

OSR = 64

OSR = 32

OSR = 16

OSR = 8

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-6

CMOS Analog Circuit Design P.E. Allen - 2010

1.5V, 1mW, 98dB Analog-Digital Converter - Continued

Circuit Implementation:

Capacitor Values

Capacitor Integrator 1 Integrator 2 Integrator 3 Integrator 4

C

s

5.00pF 0.15pF 0.30pF 0.10pF

C

i

15.00pF 1.25pF 3.00pF 1.00pF

C

a

- - 0.05pF -

C

b1

- - - 0.12pF

C

b2

- - - 0.10pF

Fig.10.9-25

1

1d

2

2d

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-7

CMOS Analog Circuit Design P.E. Allen - 2010

1.5V, 1mW, 98dB Analog-Digital Converter - Continued

Microphotograph of the modulator.

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-8

CMOS Analog Circuit Design P.E. Allen - 2010

1.5V, 1mW, 98dB Analog-Digital Converter - Continued

Measured SNR and SNDR versus input level of the modulator.

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-9

CMOS Analog Circuit Design P.E. Allen - 2010

1.5V, 1mW, 98dB Analog-Digital Converter - Continued

Measured baseband spectrum for a -7.5dBr 1kHz input.

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-10

CMOS Analog Circuit Design P.E. Allen - 2010

1.5V, 1mW, 98dB Analog-Digital Converter - Continued

Measured baseband spectrum for a -80dBr 1kHz input.

-80 dBr, 1 kHz signal

VREF = 1.5 V (diff.)

2048-point FFT

frequency, (kHz)

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-11

CMOS Analog Circuit Design P.E. Allen - 2010

1.5V, 1mW, 98dB Analog-Digital Converter - Continued

Measured 4th-Order Modulator Characteristics:

Table 5.4

Measured fourth-order delta-sigma modulator characteristics

Technology : 0.5 m triple-metal single-poly n-well CMOS process

Supply voltage 1.5 V

Die area 1.02 mm x 0.52 mm

Supply current 660 A

analog part 630 A

digital part 30 A

Reference voltage 0.75V

Clock frequency 2.8224MHz

Oversampling ratio 64

Signal bandwidth 20kHz

Peak SNR 89 dB

Peak SNDR 87 dB

Peak S/D 101dB

HD @ -5dBv 2kHz input -105dBv

DR 98 dB

3

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-12

CMOS Analog Circuit Design P.E. Allen - 2010

DECIMATION AND FILTERING

Delta-Sigma ADC Block Diagram

The decimator and filter

are implemented digitally

and consume most of the

area and the power.

Function of the decimator

and filter are;

1.) To attenuate the

quantization noise above the baseband

2.) Bandlimit the input signal

3.) Suppress out-of-band spurious signals and circuit noise

Most of the ADC applications demand decimation filters with linear phase

characteristics leading to the use of finite impulse response (FIR) filters.

FIR filters:

For a specified ripple and attenuation,

Number of filter coefficients

f

s

f

t

where f

s

is the input rate to the filter (clock frequency of the quantizer) and f

t

is the

transition bandwidth.

Fig.10.9-07

Modulator

(Analog)

Decimator

(Digital)

Lowpass Filter

(Digital)

f

S f

D

<f

S

Analog

Input

x(t)

f

B

2f

B

Digital

PCM

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-13

CMOS Analog Circuit Design P.E. Allen - 2010

A Multi-Stage Decimation Filter

To reduce the number of stages, the decimation filters are implemented in several stages.

Typical multi-stage decimation filter:

Fig.10.9-26

L+1-th

order

f

s

f

s

/D 2f

N

f

N

First-half

band filter

Second-half

band filter

f

N

Droop

correction

1.) For modulators with (1-z

-1

)

L

noise shaping comb filters are very efficient.

Comb filters are suitable for reducing the sampling rate to four times the Nyquist

rate.

Designed to supress the quantization noise that would otherwise alias into the

signal band upon sampling at an intermediate rate of f

s1

.

2.) The remaining filtering is performed by in stages by FIR or IIR filters.

Supresses out-of-band components of the signal

3.) Droop correction - may be required depending upon the ADC specifications

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-14

CMOS Analog Circuit Design P.E. Allen - 2010

Comb Filters

A comb filter that computes a running average of the last D input samples is given as

y[n] =

1

D

i=0

D-1

x[n-i]

where D is the decimation factor given as

D =

f

s

f

s1

The corresponding z-domain expression is,

H

D

(z) =

i=1

D

z

-i

=

1

D

1-z

-D

1-z

-1

The frequency response is obtained by evaluating H

D

(z) for z = e

j2fT

s

,

H

D

(f) =

1

D

sinfDT

s

sinfT

s

e

-j2fT

s

/D

where T

s

is the input sampling period (=1/f

s

). Note that the phase response is linear.

For an L-th order modulator with a noise shaping function of (1-z

-1

)

L

, the required

number of comb filter stages is L+1. The magnitude of such a filter is,

|H

D

(f)| =

1

D

sinfDT

s

sinfT

s

K

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-15

CMOS Analog Circuit Design P.E. Allen - 2010

Magnitude Response of a Cascaded Comb Filter

K = 1,2 and 3

Fig.10.9-27

-100

-80

-60

-40

-20

0

Frequency

K = 1

K= 2

0 f

b

4 f

s

D

3 f

s

D

2 f

s

D

f

s

D

K = 3

|

H

D

(

f

)

|

d

B

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-16

CMOS Analog Circuit Design P.E. Allen - 2010

Implementation of a Cascaded Comb Filter

Implementation:

Fig.10.9-28

-

+

z

-1

-

+

z

-1

-

+

z

-1

f

s

/D

K = L +1 Integrators

Numerator Section

z

-1

+

-

z

-1

+

-

z

-1

+

-

X

Y

K = L +1 Differentiators

Denominator Section

Comments:

1.) The L+1 integrators operating at the sampling frequency, f

s

, realize the denominator

of H

D

(z).

2.) The L+1 differentiators operating at the output rate of f

s1

(= f

s

/D) realize the

numerator of H

D

(z).

3.) Placing the integrator delays in the feedforward path reduces the critical path from

L+1 adder delays to a single adder delay.

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-17

CMOS Analog Circuit Design P.E. Allen - 2010

Implementation of Digital Filters

Digital filter structures:

Fig.10.9-29

x(n) h(0)

y(n)

Input Output

z

-1

h(1)

z

-1

h(2)

z

-1

h(3)

z

-1

h(N-1)

x(n) h(0)

y(n)

Input Output

z

-1

h(1)

z

-1

h(2)

z

-1

h(3)

z

-1

h(N-1)

Direct-form structure

for an FIR digital filter.

Transposed direct-form

FIR filter structure.

S.R. Norsworthy, R. Schreier, and G.C. Temes, Delta-Sigma Data Converters-Theory, Design, and Simulation, IEEE Press, NY, Chapter 13, 1997.

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-18

CMOS Analog Circuit Design P.E. Allen - 2010

Digital Lowpass Filter

Example of a typical digital filter used in removal of the quantization noise at higher

frequencies

-110

-80

-50

-20

10

4000

Frequency (Hz)

M

a

g

n

i

t

u

d

e

(

d

B

)

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-19

CMOS Analog Circuit Design P.E. Allen - 2010

Illustration of the Delta-Sigma ADC in Time and Frequency Domain

MODULATOR

DECIMATOR

LOW-PASS

FILTER

analog

input

f

D

f

S

2

fB

digital

PCM

fB

Time Time

Frequency Frequency

Frequency

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-20

CMOS Analog Circuit Design P.E. Allen - 2010

BANDPASS DELTA-SIGMA MODULATORS

Bandpass Modulators

Block diagram of a bandpass modulator:

Components:

Resonator - a bandpass filter of order

2N, N= 1, 2,....

Coarse quantizer (1 bit or multi-bit)

The noise-shaping of the bandpass oversampled ADC has the following interesting

characteristics:

Center frequency = f

s

(2N-1)/4

Bandwidth = BW = f

s

/M

Illustration of the Frequency Spectrum

(N=1):

Application of the bandpass ADC is

for systems with narrowband signals (IF frequencies)

Fig.10.9-27A

-

+

Resonator A/D

D/A

x

u

v

y

Quantizer

f

S

Frequency 3f

s

4

f

s

4

f

s

BW BW

dB

Attenuation

0

Fig. 11-32

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-21

CMOS Analog Circuit Design P.E. Allen - 2010

A First-Order AX Bandpass Modulator

Bandpass Resonator:

V(z) = z

-1

[X(z) - z

-1

V(z)] = z

-1

X(z) - z

-2

V(z)

V(z) (1+z

-2

) = z

-1

X(z) -

V(z)

X(z)

=

z

-1

1+z

-2

Modulator:

Y(z) = Q(z) + [X(z) - Y(z)]

\

|

(

!

|

\

z

-1

1+z

-2

-

Y(z) =

\

|

(

!

|

\

1+z

-2

1+z

-1

-z

-2

Q(z) +

\

|

(

!

|

\

z

-1

1+z

-1

-z

-2

X(z)

NTF

Q

(z) =

\

|

(

!

|

\

1+z

-2

1+z

-1

-z

-2

The NTF

Q

(z) has two zeros on the jc axis.

z

-1

z

-1

X(z) V(z)

+

-

Fig. 10.9-27C

Fig.10.9-27B

-

+ z

-1 +

X(z)

Q(z)

Y(z)

1+z

-2

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-22

CMOS Analog Circuit Design P.E. Allen - 2010

Resonator Design

Resonators can be designed by applying a lowpass to bandpass transform as follows:

z

-1

X(z) V(z)

+

+

Fig. 10.9-27D

z

-2

X(z) V(z)

+

+

Replace z

-1

by -z

-2

1 - z

-1

z

-1

1 + z

-2

-z

-2

Result:

Simple way to design the resonator

Inherits the stability of a lowpass modulator

Center frequency located at f

s

/4

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-23

CMOS Analog Circuit Design P.E. Allen - 2010

Fourth-Order Bandpass Modulator

Block diagram:

X(z) Y(z)

+

-

Fig. 10.9-27E

1 + z

-2

z

-2

0.5

+

+

1 + z

-2

z

-2

0.5

Comments:

Designed by applying a lowpass to bandpass transform to a second-order lowpass

modulator

The stabilty and SNR characteristics are the same as those of a second-order lowpass

modulator

The z-domain output is given as,

Y(z) = z

-4

X(z) + (1+z

-2

)

2

Q(z)

The zeros are located at z = j which corresponds to notches at f

s

/4.

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-24

CMOS Analog Circuit Design P.E. Allen - 2010

Resonator Circuit Implementation

Block diagram of z

-2

/(1+z

-2

):

z

-1

z

-1

X(z) V(z)

+

+

Fig. 10.9-27F

Fully differential switch-capacitor implementation:

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-25

CMOS Analog Circuit Design P.E. Allen - 2010

Power Spectral Density of the Previous Fourth-Order Bandpass Modulator

Simulated result:

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-26

CMOS Analog Circuit Design P.E. Allen - 2010

DELTA-SIGMA DIGITAL-TO-ANALOG CONVERTERS

Principles

The principles of oversampling and noise shaping are also widely used in the

implementation of DACs.

Simplified block diagram of a delta-sigma DAC:

Digital

delta-sigma

modulator

Interpolat-

ion filter

Analog

lowpass

filter

DAC

N-bit

Mf

N

N-bit

f

N

1-bit

Mf

N

Mf

N

Input

Digital Section

Analog Section

Output

Fig10.9-29

Operation:

1.) A digital signal with N-bits with a data rate of f

N

is sampled at a higher rate of Mf

N

by

means of an interpolator.

2.) Interpolation is achieved by inserting 0s between each input word with a rate of

Mf

N

and then filtering with a lowpass filter.

3.) The MSB of the digital filter is applied to a DAC which is applied to an analog

lowpass filter to achieve the analog output.

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-27

CMOS Analog Circuit Design P.E. Allen - 2010

Block Diagram of a DAC

Analog

Output -

+

Interpol-

ation

Digital

Filter

Digital Code

Conversion

0100000000000000 =-1

1011111111111111 = 1

V

Ref

-V

Ref

Digital

Input

f

N

f

S

=Mf

N

f

S

f

S

f

S

Analog

Lowpass

Filter

MSB

DAC

f

S f

S

Fig10.9-31

y(k)

Operation:

1.) Interpolate a digital word at the conversion rate of the converter (f

N

) up to the sample

frequency, f

s

.

2.) The word length is then reduced to one bit with a digital sigma-delta modulator.

3.) The one bit PDM signal is converted to an analog signal by switching between two

reference voltages.

4.) The high-frequency quantization noise is removed with an analog lowpass filter

yielding the required analog output signal.

Sources of error:

Device mismatch (causes harmonic distortion rather than DNL or INL)

Component noise

Device nonlinearities

Clock jitter sensitivity

Inband quantization error from the - modulator

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-28

CMOS Analog Circuit Design P.E. Allen - 2010

Frequency Viewpoint of the DAC

Frequency spectra at different points of the delta-sigma ADC:

Frequency 0

Interpolation

filter output

Delta-sigma

modulator

output

Lowpass

filter

output

Input

Magnitude

Quantization noise after

filtering

-0.5f

N

0.5f

N

f

N

(M-1)f

N

Mf

N

Frequency

Mf

N

0 -0.5f

N

0.5f

N

Frequency

Mf

N

0 -0.5f

N

0.5f

N

Frequency

Mf

N

0 -0.5f

N

0.5f

N

Fig10.9-33

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-29

CMOS Analog Circuit Design P.E. Allen - 2010

A Third-Order, Modulator for a DAC

A digital equivalent of the third-order MASH modulator is shown below.

X

Y

X+Y

Latch

Over-

flow

X+Y

Latch

Over-

flow

X+Y

Latch

Over-

flow

z

-1

z

-1

+ +

+ +

Clk

Clk

Clk

8-state

Output

Digital

Inputs

070521-01

The m-bit accumulators consist of an m-bit adder and m-bit latches.

The 8-state digital output is converted to an analog through means of an analog filter.

Spectral outputs:

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-30

CMOS Analog Circuit Design P.E. Allen - 2010

1-BitDAC for the Digital-to-Analog Converter - The Analog Part

The MSB output from the digital filter is used to drive a 1-bit DAC.

Possible architectures:

-V

Ref

1

y(k)

2

y(k)

V

Ref

1

y(k)

C R

Analog

lowpass

filter

with -3dB

frequency

of 0.5f

N

Analog

Output

R

C

2

y(k)

Analog

lowpass

filter with

-3dB

frequency

of 0.5f

N

Analog

Output

I

Ref

-I

Ref

Voltage-driven DAC with a

passive lowpass filter stage.

Current-driven DAC with a

passive lowpass filter stage.

Fig10.9-32

A multi-bit output would consist of more parallel, controlled current sources and sinks.

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-31

CMOS Analog Circuit Design P.E. Allen - 2010

Switched-Capacitor DAC and Filter

Typically, the DAC and the first stage of the lowpass filter are implemented using

switched-capacitor techniques.

-V

Ref

1

y(k)

V

Ref

1

y(k)

2

+

-

1

C

1

C

2

R

To analog

lowpass

filter

Fig10.9-34

It is necessary to follow the switched-capacitor filter by a continuous time lowpass filter

to provide the necessary attenuation of the quantization noise.

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-32

CMOS Analog Circuit Design P.E. Allen - 2010

SUMMARY

Comparison of the Various Types of ADCs

A/D Converter Type Maximum

Practical Number

of Bits (1)

Speed

(Expressed in terms

of T a clock period)

Area Dependence

on the number of

bits, N, or other

ADC parameters

Dual Slope

12-14 bits

2(2

NT

)

Independent

Successive Approximation

with self-correction

12-15 bits NT N

1-Bit Pipeline 10 bits T (After NT delay ) N

Algorithmic 12 bits NT Independent

Flash 6 bits T

2

N

Two-step, flash 10-12 bits 2T

2

N/2

Mulitple-bit, M-pipe 12-14 bits MT

2

N/M

- Oversampled (1-bit, L

loops and M= oversampling

ratio = f

clock

/2f

b

) 15-17 bits MT L

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-33

CMOS Analog Circuit Design P.E. Allen - 2010

Comparison of Recent ADCs

Resolution versus conversion rate:

5

10

15

20

25

O

u

t

p

u

t

w

o

r

d

l

e

n

g

t

h

Conversion rate, (samples/sec.)

1 10

2 10

4

10

6

10

8

10

10

Figure 10.10-1

Flash

Pipelined

Algorithmic

Dual-slope

Delta-sigma

Successive approximation

Folding/Interpolating

Bandpass delta-sigma

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-34

CMOS Analog Circuit Design P.E. Allen - 2010

Comparison of Recent ADCs - Continued

Power dissipation versus conversion rate:

Figure 10.10-2

0.01

0.1

1

10

100

1000

1 100 10

4

10

6

10

8

10

10

P

o

w

e

r

D

i

s

s

i

p

a

t

i

o

n

(

m

W

)

Conversion Rate (Samples/second)

Flash

Pipelined

Delta-sigma

Successive approximation

Folding/Interpolating

Bandpass delta-sigma

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-35

CMOS Analog Circuit Design P.E. Allen - 2010

References for Previous Figures

[1] A 12-b, 60-MSample/s Cascaded Folding and Interpolating ADC. Vorenkamp, P., IEEE J-SC, vol. 32, no. 12, Dec 97 1876

1886

[2] A 15-b, 5-Msample/s Low-Spurious CMOS ADC. Kwak, S. -U., IEEE J-SC, vol. 32, no. 12, Dec 97 1866-1875

[3] Error Suppressing Encode Logic of FCDL in a 6-b Flash A/D Converter. Ono, K., IEEE J-SC, vol. 32, no.9, Sep 97 1460-

1464

[4] A Cascaded Sigma-Delta Pipeline A/D Converter with 1.25 MHz Signal Bandwidth and 89 dB SNR. Brooks, T. L., IEEE

J-SC, vol.32, no.12, Dec 97 1896-1906

[5] A 10-b, 100 MS/s CMOS A/D Converter. Kwang Young Kim, IEEE J-SC, vol. 32, no. 3, Mar 97 302-311

[6] A 1.95-V, 0.34-mW, 12-b Sigma-Delta Modulator Stabilized by Local Feedback Loops. Au, S., IEEE J-SC, vol. 32, no. 3,

Mar 97 321-328

[7] A 250-mW, 8-b, 52Msamples/s Parallel-Pipelined A/D Converter with Reduced Number of Amplifiers. Nagaraj, K., IEEE J

SC, vol. 32, no. 3, Mar 97 312-320

[8] A DSP-Based Hearing Instrument IC. Neuteboom, H., IEEE J-SC, vol. 32, no. 11, Nov 97 1790-1806

[9] An Embedded 240-mW 10-b 50MS/s CMOS ADC in 1-mm

2

. Bult, K., IEEE J-SC, vol. 32, no. 12, Dec 97 1887-1895

[10] Low-Voltage Double-Sampled Converters. Senderowicz, D., IEEE J-SC, vol. 32, no.12, Dec 97 1907-1919

[11] Quadrature Bandpass Modulation for Digital Radio. Jantzi, S. A., IEEE J-SC, vol. 32, no. 12, Dec 97 1935-1950

[12] A Two-Path Bandpass Modulator for Digital IF Extraction at 20 MHz. Ong, A. K., IEEE J-SC, vol. 32, no. 12, Dec 97

1920-1934

[13] A 240-Mbps, 1-W CMOS EPRML Read-Channel LSI Chip Using an Interleaved Subranging Pipeline A/D Converter.

Matsuura, T., IEEE J-SC, vol. 33, no. 11, Nov 98 1840-1850

[14] A 13-Bit, 1.4 MS/s Sigma-Delta Modulator for RF Baseband Channel Applications. Feldman, A. R., IEEE J-SC, vol. 33,

no. 10, Oct 98 1462-1469

[15] Design and Implementation of an Untrimmed MOSFET-Only 10-Bit A/D Converter with 79-dB THD. Hammerschmied,

C. M., IEEE J-SC, vol. 33, no. 8, Aug 98 1148-1157

[16] A 15-b Resolution 2-MHz Nyquist Rate ADC in a 1-m CMOS Technology. Marques, A. M., IEEE J-SC, vol. 33, no.

7, Jul 98 1065-1075

[17] A 950-MHz IF Second-Order Integrated LC Bandpass Delta-Sigma Modulator. Gao, W., IEEE J-SC, vol. 33, no. 5, May

98 723-732

[18] A 200-MSPS 6-Bit Flash ADC in 0.6m CMOS. Dalton, D., IEEE Transactions on Circuits and Systems II: Analog and

Digital Signal Processing, vol. 45, no. 11, Nov 98 1433-1444

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-36

CMOS Analog Circuit Design P.E. Allen - 2010

References - Continued

[19] A 5-V Single-Chip Delta-Sigma Audio A/D Converter with 111 dB Dynamic Range. Fujimori, I., IEEE J-SC, vol. 32, no.

3, Mar 97 329-336

[20] A 256 x 256 CMOS Imaging Array with Wide Dynamic Range Pixels and Column-Parallel Digital Output. Decker, S.,

IEEE J-SC, vol. 33, no.12, Dec 98 2081-2091

[21] A 400 Msample/s, 6-b CMOS Folding and Interpolating ADC. Flynn, M., IEEE J-SC, vol. 33, no.12, Dec 98 1932-1938

[22] An Analog Background Calibration Technique for Time-Interleaved Analog-to-Digital Converters. Dyer, K. C., IEEE J-SC,

vol. 33, no.12, Dec 98 1912-1919

[23] A CMOS 6-b, 400-Msample/s ADC with Error Correction. Tsukamoto, S., IEEE J-SC, vol. 33, no.12, Dec 98 1939-1947

[24] A Continuously Calibrated 12-b, 10-MS/s, 3.3-V ADC. Ingino, J. M., IEEE J-SC, vol. 33, no.12, Dec 98 1920-1931

[25] A Delta-Sigma PLL for 14b, 50 ksamples/s Frequency-to-Digital Conversion of a 10 MHz FM Signal. Galton, I., IEEE J-

SC, vol. 33, no.12, Dec 98 2042-2053

[26] A Digital Background Calibration Technique for Time-Interleaved Analog-to-Digital Converters. Fu, D., IEEE J-SC, vol. 33

no.12, Dec 98 1904-1911

[27] An IEEE 1451 Standard Transducer Interface Chip with 12-b ADC, Two 12-b DACs, 10-kB Flash EEPROM, and 8-b

Microcontroller. Cummins, T., IEEE J-SC, vol. 33, no.12, Dec 98 2112-2120

[28] A Single-Ended 12-bit 20 Msample/s Self-Calibrating Pipeline A/D Converter. Opris, I. E., IEEE J-SC, vol. 33, no.12, Dec

98 1898-1903

[29] A 900-mV Low-Power A/D Converter with 77-dB Dynamic Range. Peluso, V., IEEE J-SC, vol. 33, no.12, Dec 98

1887-1897

[30] Third-Order Modulator Using Second-Order Noise-Shaping Dynamic Element Matching. Yasuda, A., IEEE J-SC, vol.

33, no.12, Dec 98 1879-1886

[31] R, G, B Acquisition Interface with Line-Locked Clock Generator for Flat Panel Display. Marie, H., IEEE J-SC, vol. 33,

no.7, Jul 98 1009-1013

[32] A 25 MS/s 8-b - 10 MS/s 10-b CMOS Data Acquisition IC for Digital Storage Oscilloscopes. Kusayanagi, N., IEEE J-SC,

vol. 33, no.3, Mar 98 492-496

[33] A Multimode Digital Detector Readout for Solid-State Medical Imaging Detectors. Boles, C. D., IEEE J-SC, vol. 33, no.5,

May 98 733-742

[34] CMOS Charge-Transfer Preamplifier for Offset-Fluctuation Cancellation in Low Power A/D Converters. Kotani, K., IEEE J-

SC, vol. 33, no.5, May 98 762-769

[35] Design Techniques for a Low-Power Low-Cost CMOS A/D Converter. Chang, Dong-Young, IEEE J-SC, vol. 33, no.8,

Aug 98 1244-1248

Lecture 400 Oversampling ADCs Part II (3/29/10) Page 400-37

CMOS Analog Circuit Design P.E. Allen - 2010

CONCLUDING THOUGHTS

What is analog circuit design?

The complex process of creating circuit solutions using analog circuit techniques.

What is the analog integrated circuit design process?

The even more complex process of combining analog design with IC technology

which includes electrical, physical and test design.

What are the key principles, concepts and techniques for analog IC design?

Key principles Fundamental laws

Key concepts Important relationships and

ideas

How can the analog IC designer enhance

creativity and solve new problems in todays

industrial environment?

Learn the key principles, concepts and techniques of

analog circuit design

Learn from mistakes

Learn the technology

Always try to understand the concept and operation

of the circuit, never rely on a computer or someone else for this understanding

Technology changes but principles, concepts and

techniques remain the same.

Key techniques Tools that allow

simplification or insight

Das könnte Ihnen auch gefallen

- Digital Signal Processing: Instant AccessVon EverandDigital Signal Processing: Instant AccessBewertung: 3.5 von 5 Sternen3.5/5 (2)

- Maximizing GSPS ADC SFDR PerformanceDokument38 SeitenMaximizing GSPS ADC SFDR PerformanceSrinagesh V MandapakaNoch keine Bewertungen

- Annex RAN.01.04 Link Budget (4T4R)Dokument27 SeitenAnnex RAN.01.04 Link Budget (4T4R)Sami DohaNoch keine Bewertungen

- P I C D A A U S I 8 2 4 A D: Erformance Mprovements IN Lass Udio Mplifiers Sing X Udio RiversDokument12 SeitenP I C D A A U S I 8 2 4 A D: Erformance Mprovements IN Lass Udio Mplifiers Sing X Udio RiversluizcpimentaNoch keine Bewertungen

- High-Performance D/A-Converters: Application to Digital TransceiversVon EverandHigh-Performance D/A-Converters: Application to Digital TransceiversNoch keine Bewertungen

- Netzer DS 247 128 SpecsheetDokument8 SeitenNetzer DS 247 128 SpecsheetElectromateNoch keine Bewertungen

- OFDM Versus Single Carrier With Cyclic Prefix: A System-Based Comparison For Binary ModulationDokument4 SeitenOFDM Versus Single Carrier With Cyclic Prefix: A System-Based Comparison For Binary ModulationKieu HuongNoch keine Bewertungen

- D-Band Frequency Tripler For Passive Imaging - Final 13th JulyDokument4 SeitenD-Band Frequency Tripler For Passive Imaging - Final 13th JulyTapas SarkarNoch keine Bewertungen

- PWR Bal CalDokument36 SeitenPWR Bal Calarijeetdguy3051Noch keine Bewertungen

- Vlsi Design & TechnolgyDokument60 SeitenVlsi Design & TechnolgyDimple GalaNoch keine Bewertungen

- Band-Pass Filtered, Inverting - 40 DB Attenuator, 10 HZ - 100 KHZ, 0.1 DB ErrorDokument20 SeitenBand-Pass Filtered, Inverting - 40 DB Attenuator, 10 HZ - 100 KHZ, 0.1 DB ErrorSalman ZafarNoch keine Bewertungen

- F0283111611-Ijsce Paper - SubirDokument5 SeitenF0283111611-Ijsce Paper - SubirSubir MaityNoch keine Bewertungen

- Epoch-Modeling and Simulation of An AllDokument40 SeitenEpoch-Modeling and Simulation of An Allraducu2009Noch keine Bewertungen

- Low Power Nine-Bit Sigma-Delta ADC Design Using TSMC 0.18micron TechnologyDokument5 SeitenLow Power Nine-Bit Sigma-Delta ADC Design Using TSMC 0.18micron Technologyeditor_ijtel100% (1)

- Circuit Note: High Performance, 12-Bit, 500 MSPS Wideband Receiver With Antialiasing FilterDokument6 SeitenCircuit Note: High Performance, 12-Bit, 500 MSPS Wideband Receiver With Antialiasing Filtersanjay_drdo237Noch keine Bewertungen

- Dynamic Testing of Highspeed Adcs Part 2Dokument17 SeitenDynamic Testing of Highspeed Adcs Part 2ketkyhuNoch keine Bewertungen

- UCC28070Dokument27 SeitenUCC28070gubiliNoch keine Bewertungen

- Survey System Design and EnggDokument123 SeitenSurvey System Design and Enggvisakh21Noch keine Bewertungen

- PCB Layout DesignDokument74 SeitenPCB Layout DesignMallappa Patil100% (1)

- A Three-Stage Operational Transconductance Amplifier For Delta Sigma ModulatorDokument6 SeitenA Three-Stage Operational Transconductance Amplifier For Delta Sigma ModulatorZuriel EduardoNoch keine Bewertungen

- Applied Sciences: Fully Di Current-Feedback Instrumentation Amplifier With R-2R Dac O Bridge SensorsDokument9 SeitenApplied Sciences: Fully Di Current-Feedback Instrumentation Amplifier With R-2R Dac O Bridge Sensorspraba821Noch keine Bewertungen

- David Farrell Dane Sprister Matthew TaylorDokument55 SeitenDavid Farrell Dane Sprister Matthew TaylorQuân Trần ĐìnhNoch keine Bewertungen

- 12EC62R20 Ramesh SynopsisDokument9 Seiten12EC62R20 Ramesh Synopsisprasad72207Noch keine Bewertungen

- THLDL: Wright2Dokument2 SeitenTHLDL: Wright2Dennis AtyugrasiwiNoch keine Bewertungen

- Tda 9875Dokument93 SeitenTda 9875FxprimeNoch keine Bewertungen

- SOLiD NICS PrSOLiD NICS Product Specifications V1.2oduct Specifications v1.2Dokument7 SeitenSOLiD NICS PrSOLiD NICS Product Specifications V1.2oduct Specifications v1.2Tú Nguyễn NgọcNoch keine Bewertungen

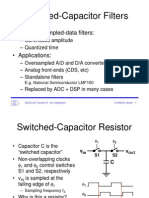

- Switched-Capacitor Filters: - "Analog" Sampled-Data FiltersDokument24 SeitenSwitched-Capacitor Filters: - "Analog" Sampled-Data FiltersPushpendra DwivediNoch keine Bewertungen

- Digital DDS Generator With AD9850 Chip DDS From SQ5RWQDokument4 SeitenDigital DDS Generator With AD9850 Chip DDS From SQ5RWQag1tatorNoch keine Bewertungen

- Active-Filtering Circuit For Audio Dacs: Analog Engineer'S Circuit: Data ConvertersDokument6 SeitenActive-Filtering Circuit For Audio Dacs: Analog Engineer'S Circuit: Data Convertersraffy mundungNoch keine Bewertungen

- Agilent Eesof Eda: Overview On Designing A Low-Noise Vco On Fr4Dokument6 SeitenAgilent Eesof Eda: Overview On Designing A Low-Noise Vco On Fr4bayman66Noch keine Bewertungen

- ECE 5221 Personal Communication Systems: Prepared By: Dr. Ivica KostanicDokument13 SeitenECE 5221 Personal Communication Systems: Prepared By: Dr. Ivica KostanicalperusluNoch keine Bewertungen

- Sound Multiplex Demodulator IC For TV in The North American MarketDokument11 SeitenSound Multiplex Demodulator IC For TV in The North American Marketjosenicolas12000Noch keine Bewertungen

- EDN Design Ideas 2006Dokument142 SeitenEDN Design Ideas 2006chag1956100% (1)

- 19.CDMA Link Budget (V0.1)Dokument31 Seiten19.CDMA Link Budget (V0.1)Hadi AgustanaNoch keine Bewertungen

- Shanthi Pavan - CT Audio DSM With FIR - JSSC 2014Dokument11 SeitenShanthi Pavan - CT Audio DSM With FIR - JSSC 2014Saleh Heidary ShalmanyNoch keine Bewertungen

- 08 HirtenfelderDokument42 Seiten08 HirtenfelderMazigh HoudNoch keine Bewertungen

- Charge Redistribution AdcDokument74 SeitenCharge Redistribution AdcAnonymous eWMnRr70qNoch keine Bewertungen

- Netzer DS-25 SpecsheetDokument8 SeitenNetzer DS-25 SpecsheetElectromateNoch keine Bewertungen

- Bandpass Continuous-Time Delta-Sigma Modulator For Wireless Receiver ICDokument4 SeitenBandpass Continuous-Time Delta-Sigma Modulator For Wireless Receiver ICBalthier8745Noch keine Bewertungen

- 05 CommonModulesNESignalFlowDokument36 Seiten05 CommonModulesNESignalFlowJuan OrellanaNoch keine Bewertungen

- Clock and Data Recovery For Serial Digital CommunicationDokument79 SeitenClock and Data Recovery For Serial Digital Communicationquail36Noch keine Bewertungen

- Sigma DeltaDokument30 SeitenSigma Deltaleenu123Noch keine Bewertungen

- Andrea GoldsmithDokument99 SeitenAndrea GoldsmithdhayavelNoch keine Bewertungen

- Transformer-Coupled Front-End For Wideband A/D Converters: Primary SecondaryDokument4 SeitenTransformer-Coupled Front-End For Wideband A/D Converters: Primary SecondaryAvinash SharmaNoch keine Bewertungen

- Class D Audio Amplifier With Ferroxcube Gapped Toroid Output FilterDokument0 SeitenClass D Audio Amplifier With Ferroxcube Gapped Toroid Output Filterikaro181083100% (1)

- Analog Devices CD ReferenceDokument8 SeitenAnalog Devices CD ReferenceAcody Ie SyNoch keine Bewertungen

- Design of Audio Delta-Sigma A/D ConvertersDokument17 SeitenDesign of Audio Delta-Sigma A/D Convertershariprasath_vNoch keine Bewertungen

- Analog Communications: - Amplitude Modulation (AM) - Frequency Modulation (FM)Dokument32 SeitenAnalog Communications: - Amplitude Modulation (AM) - Frequency Modulation (FM)casastrozNoch keine Bewertungen

- 11 09 1213-01-00ad 60ghz Impairments ModelingDokument29 Seiten11 09 1213-01-00ad 60ghz Impairments Modelingnayeem4444Noch keine Bewertungen

- Tuneintoe TV.: The Authority On Emerging Technologies For Design SolutionsDokument78 SeitenTuneintoe TV.: The Authority On Emerging Technologies For Design SolutionsstrahinjaNoch keine Bewertungen

- Architectures and RF System Design Issues For 3G Transceiver SystemsDokument26 SeitenArchitectures and RF System Design Issues For 3G Transceiver SystemsWalid Ali-AhmadNoch keine Bewertungen

- Transmission Line XDokument21 SeitenTransmission Line XKifaru Micro-electronicsNoch keine Bewertungen

- High Resolution Delta-Sigma Adcs: Slide 1Dokument64 SeitenHigh Resolution Delta-Sigma Adcs: Slide 1Sarawut PhetsilpNoch keine Bewertungen

- Ask The Application Engineer-33 All About Direct Digital SynthesisDokument5 SeitenAsk The Application Engineer-33 All About Direct Digital SynthesisleuteriosNoch keine Bewertungen

- Modelling Sigdelta Non-IdealtiesDokument5 SeitenModelling Sigdelta Non-IdealtiesVivek KumarNoch keine Bewertungen

- Lecture 050 - All-Digital Phase Lock Loops (Adplls)Dokument20 SeitenLecture 050 - All-Digital Phase Lock Loops (Adplls)Ajay GuptaNoch keine Bewertungen

- 01435604Dokument13 Seiten01435604Klanto PothikNoch keine Bewertungen

- Design of Multiplier Free Fir Filters Using A Ladf Sigmadelta MDokument4 SeitenDesign of Multiplier Free Fir Filters Using A Ladf Sigmadelta MEngr. Aneela PathanNoch keine Bewertungen

- ECE - (4 Year B.Tech Programme) - COURSE CURRICULUM R-19Dokument18 SeitenECE - (4 Year B.Tech Programme) - COURSE CURRICULUM R-19320126512L20 yerramsettibhaskarNoch keine Bewertungen

- Eval Ad7606 PDFDokument28 SeitenEval Ad7606 PDFbillylu06Noch keine Bewertungen

- DSP Lab Manual PerfectDokument139 SeitenDSP Lab Manual PerfectSsgn Srinivasarao50% (2)

- Figure 1: A Block Diagram of A Basic FilterDokument10 SeitenFigure 1: A Block Diagram of A Basic Filterammayi9845_930467904Noch keine Bewertungen

- Digital Filter DesignDokument209 SeitenDigital Filter DesigntowfiqeeeNoch keine Bewertungen

- 1-Digital Filters (FIR)Dokument71 Seiten1-Digital Filters (FIR)Muhammad IrfanNoch keine Bewertungen

- Digital Signal Processing Digital Signal Processing: DSP Lab Manual DSP Lab ManualDokument37 SeitenDigital Signal Processing Digital Signal Processing: DSP Lab Manual DSP Lab Manualsalman shariffNoch keine Bewertungen

- Basic Signal Processing With Matlab PDFDokument211 SeitenBasic Signal Processing With Matlab PDFCaio CorreiaNoch keine Bewertungen

- Dsp-Unit 5.1 Analog FiltersDokument67 SeitenDsp-Unit 5.1 Analog FiltersMaheswaraNoch keine Bewertungen

- Data Acquisition Labview 7.0 Daq CourseDokument432 SeitenData Acquisition Labview 7.0 Daq CourseKiran Jot SinghNoch keine Bewertungen

- ESDokument31 SeitenESKummari NagaiahNoch keine Bewertungen

- T.E (E&TC) - 2019 Course - 09.07.2021Dokument95 SeitenT.E (E&TC) - 2019 Course - 09.07.2021ind.sudhirNoch keine Bewertungen

- Web Audio APIDokument27 SeitenWeb Audio APIquakigNoch keine Bewertungen

- Kyowa EDX 200A CatalogDokument6 SeitenKyowa EDX 200A CatalogtnlesmanaNoch keine Bewertungen

- Syllabus 23Dokument58 SeitenSyllabus 23Muthu KumarNoch keine Bewertungen

- Iri1 WDDokument12 SeitenIri1 WDecplpraveen100% (2)

- Wiener Filter DSP ProakisDokument5 SeitenWiener Filter DSP ProakisAlex Nuñez MuñozNoch keine Bewertungen

- 1 ECE 438 Lecture NotesDokument63 Seiten1 ECE 438 Lecture Notesilluminationmoi579Noch keine Bewertungen

- PG Ece - 03112017Dokument55 SeitenPG Ece - 03112017Himanshu SinghNoch keine Bewertungen

- ECE-VII-DSP ALGORITHMS & ARCHITECTURE Part ADokument111 SeitenECE-VII-DSP ALGORITHMS & ARCHITECTURE Part AmanjumathgowdaNoch keine Bewertungen

- Zivesmv 661 EngDokument302 SeitenZivesmv 661 EngThuận Võ NgọcNoch keine Bewertungen

- Finals DSP WithMinimalErrors PDFDokument64 SeitenFinals DSP WithMinimalErrors PDFanembam putobungbongNoch keine Bewertungen

- GE Multilin SR350 Instruction Manual Ver1.5xDokument266 SeitenGE Multilin SR350 Instruction Manual Ver1.5xBill Cai100% (2)

- !!!!!!!!!!!!2009-Wiley-Handbook of Measuring System DesignDokument1.358 Seiten!!!!!!!!!!!!2009-Wiley-Handbook of Measuring System Designzoranmiskovic100% (1)

- A Computationally Efficient Frequency Domain LMS AlgorithmDokument7 SeitenA Computationally Efficient Frequency Domain LMS AlgorithmAnagachinmeyNoch keine Bewertungen

- DSP Principles Algorithms and Applications Third EditionDokument1.033 SeitenDSP Principles Algorithms and Applications Third EditionHarish Gunasekaran100% (1)

- DSP Exam AidDokument7 SeitenDSP Exam AidAnonymous cYhhyVNoch keine Bewertungen

- Solution Manual For Introduction To Digital Signal Processing 1st Edition Dick Blandford John ParrDokument8 SeitenSolution Manual For Introduction To Digital Signal Processing 1st Edition Dick Blandford John ParrLaura ThriftNoch keine Bewertungen

- Efficient FIR Filter Architectures Suitable For FPGA ImplementationDokument4 SeitenEfficient FIR Filter Architectures Suitable For FPGA Implementationyunqi guanNoch keine Bewertungen

- ZCDDokument5 SeitenZCDotavioalcaldeNoch keine Bewertungen