Beruflich Dokumente

Kultur Dokumente

M Tech NEW

Hochgeladen von

Mallik ArjunOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

M Tech NEW

Hochgeladen von

Mallik ArjunCopyright:

Verfügbare Formate

CURRICULUM VITAE

SHIVARUDRAIAH. B S/O Basavarajaiah. B. S Byandahalli, Kadabagere Post, Bangalore North Thaluk PIN: 562130

E-mail: shiv2byn@gmail.com Mobile: +91-9482138388

CARRIER OBJECTIVE To work on innovative solutions by applying and developing my technical skills as a software professional with gifted colleagues in an environment that builds and rewards creative thinking and teamwork. EDUCATIONAL QUALIFICATION Name of the Name Name of the Institution Course M. Tech [VLSI Design & Embedded Systems] B. E [Electronics and Communication] Dr. Ambedkar Institute of Technology, Bangalore East West Institute of Technology, Bangalore K.L.E'S Independent PreUniversity College, Bangalore St. Chistys High School , Bangalore University Visveswaraiah Technological University, Belgaum Visveswaraiah Technological University, Belgaum Karnataka PreUniversity Board Year of passing 2010 Aggregate percentage 76.88%

2008

69.96%

Pre-University course

2004

80.83%

SSLC

K.S.E.E. Board

2002

84.16%

TECHNICAL SKILLS Hardware Programming Software Programming Verilog HDL, Microprocessor 8085, 8086 Microcontroller 8051. Basics of C, C++. MAJOR SUBJECTS STUDIED Basic Electronics, Logic Design, Analog & Digital Communication, Embedded system design, Synthesis & Optimization of digital circuits, CMOS VLSI design, and CMOS RF circuit design. WORKSHOP ATTENDED Front end Verilog and front end design Verification PROJECTS Project Name: Implementation of a Multi-channel UART Controller Based on FIFO Technique and FPGA Description: To meet modern complex control systems communication demands, we

need to go for designing a multi-channel UART controller based on FIFO(First In First Out) technique and FPGA(Field Programmable Gate Array). It includes the design of asynchronous FIFO and structure of the controller. This controller is designed with FIFO circuit block and UART (Universal Asynchronous Receiver Transmitter) circuit block within FPGA to implement communication in modern complex control systems quickly and effectively. Form the communication sequence diagrams; it is easily to know that this controller can be used to implement communication when master equipment and slaver equipment are set at different Baud Rate. It also can be used to reduce synchronization error between sub-systems in a system with several sub-systems. The controller is reconfigurable and scalable. Keywords: FIFO, FPGA, UART. Project Name: Advanced ATM Monitoring System Description: This is an automation system for the ATM which also enhances the security functions at ATM center. This automation system will have installation feature which

will remove the human intervention in switching ON/OFF the lights both inside and outside of ATM center which would result in power saving. Software: Embedded C, Keil. PERSONAL PROFILE Date of Birth Sex Nationality Languages Known Strengths Hobbies : 28-08-1987 : Male : Indian : English, Kannada, and Hindi : Team player, Integrity, Good communication skills : Following all kinds of sports, participating in extra curricular

activities like quiz competition, listening to music etc

DECLARATION I here by declare that all the above details are true according to the best of my knowledge and belief.

Place: Date: [Shivarudraiah. B]

Das könnte Ihnen auch gefallen

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (345)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- I73e SGDV - Sigma-5 Servo Drive Datasheet enDokument24 SeitenI73e SGDV - Sigma-5 Servo Drive Datasheet enluisNoch keine Bewertungen

- 3gpp Cdrs Specs AlcatelDokument337 Seiten3gpp Cdrs Specs AlcatelPatrick AdinaNoch keine Bewertungen

- Unit 4 - Networks and The Effects of Using ThemDokument12 SeitenUnit 4 - Networks and The Effects of Using ThemEdwardNoch keine Bewertungen

- EXFO 100G Testing Guide PDFDokument104 SeitenEXFO 100G Testing Guide PDFJunaidNoch keine Bewertungen

- Avaya QuotationDokument4 SeitenAvaya QuotationBITL TechnologyNoch keine Bewertungen

- A5 Microelectronic Systems 5 Nyquist ADDokument25 SeitenA5 Microelectronic Systems 5 Nyquist ADKoldodeRostovNoch keine Bewertungen

- DatasheetDokument4 SeitenDatasheetquasemanobrasNoch keine Bewertungen

- Huawei Mobily WiMAX LTE (Samar 707649)Dokument78 SeitenHuawei Mobily WiMAX LTE (Samar 707649)Nasir Iqbal100% (1)

- Market Survey On Copper PDFDokument210 SeitenMarket Survey On Copper PDFmujib uddin siddiquiNoch keine Bewertungen

- PD Flow DocumentDokument4 SeitenPD Flow DocumentJaswanth TejaNoch keine Bewertungen

- DC Question BankDokument15 SeitenDC Question BankpalansamyNoch keine Bewertungen

- AES Grounding PaperDokument13 SeitenAES Grounding PaperBeranga2Noch keine Bewertungen

- Cypress Product Roadmap Public 001-89435 - 0LDokument255 SeitenCypress Product Roadmap Public 001-89435 - 0LKumar BabuNoch keine Bewertungen

- RTC 402Dokument54 SeitenRTC 402Noufal ShajahanNoch keine Bewertungen

- Asus P8Z77-V LX Component TrainingDokument48 SeitenAsus P8Z77-V LX Component TrainingDelwar Hossain100% (1)

- RCV 420Dokument12 SeitenRCV 420api-3725139Noch keine Bewertungen

- MC 8051 LAB ManualDokument26 SeitenMC 8051 LAB ManualShweta GadgayNoch keine Bewertungen

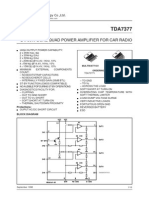

- 2 X 3 W Dual/Quad Power Amplifier For Car Radio: ProtectionsDokument10 Seiten2 X 3 W Dual/Quad Power Amplifier For Car Radio: ProtectionsJosé VidalNoch keine Bewertungen

- CHC X91 PDFDokument4 SeitenCHC X91 PDFCosmas MusondaNoch keine Bewertungen

- What Is A Tuned AmplifierDokument4 SeitenWhat Is A Tuned AmplifierSaiyma Fatima RazaNoch keine Bewertungen

- Relays TerminologyDokument1 SeiteRelays TerminologyJavid SalamovNoch keine Bewertungen

- 88H Manual - IdiposDokument8 Seiten88H Manual - IdiposErfan OktafianNoch keine Bewertungen

- VEICULAR 43 175MHzDokument11 SeitenVEICULAR 43 175MHzZamfir GeoNoch keine Bewertungen

- Itrainonline MMTK Access Point Configuration HandoutDokument11 SeitenItrainonline MMTK Access Point Configuration HandoutSantosh KhadkaNoch keine Bewertungen

- Reyrolle 7SR10 Platform: Protecting Grid With ConfidenceDokument5 SeitenReyrolle 7SR10 Platform: Protecting Grid With ConfidenceGabriel NaspiranNoch keine Bewertungen

- Chass CN 001ADokument44 SeitenChass CN 001ARodrigo SanchezNoch keine Bewertungen

- Brushed DC Speed Control With Back EMF FeedbackDokument17 SeitenBrushed DC Speed Control With Back EMF FeedbackJulian HayesNoch keine Bewertungen

- OUTLINE DRAWING DRAWING 500kVA YNyn6Dokument1 SeiteOUTLINE DRAWING DRAWING 500kVA YNyn6SetiawanBudiNoch keine Bewertungen

- Multilin F650 MODBUS Memory MapDokument411 SeitenMultilin F650 MODBUS Memory MapMaclaurinHeronNoch keine Bewertungen

- Sunmi L2 - Brochure PDADokument1 SeiteSunmi L2 - Brochure PDAStan TCNoch keine Bewertungen