Beruflich Dokumente

Kultur Dokumente

American International University-Bangladesh: Objectives

Hochgeladen von

Showkat Hossen SabujOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

American International University-Bangladesh: Objectives

Hochgeladen von

Showkat Hossen SabujCopyright:

Verfügbare Formate

AMERICAN INTERNATIONAL UNIVERSITY-BANGLADESH

FACULTY OF ENGINEERING EEE 4217: VLSI CIRCUIT DESIGN Experiment 10: Layout design of a 4x4 bit Static RAM

Objectives:

To understand the operation of 6-transistor static RAM cell. To check the layout of a 6-transistor static RAM cell. To simulate the 1-bit RAM cell layout. To build a 4x4 bit RAM array. To build a complete 4x4 bit RAM chip including I/O pads. To generate a CIF file of the RAM chip.

RAM Memory

The schematic diagram of the static memory cell used in High Capacity Static RAMs is given in Figure 1. The circuit consists of 2 cross-coupled inverters and two nMOS pass transistors. The cell has been designed to be duplicated in X and Y in order to create a large array of cells. Usual sizes for Megabit SRAM memories are 256 x 256 cells or higher. The selection line Sel concerns all the cells of one row. The lines Data and nData concern all the cells of one column.

The RAM layout is given in Figure 2. Click on File -> Read -> RAM.MSK to read it from C:\MICROWIND directory. The Data and nData signals are made with metal and cross the cell from top to bottom. This allows easy matrix-style duplication of the RAM cell.

WRITE CYCLE. Values 1 or 0 must be placed on Data, and the data inverted value on nData. Then the line Sel goes to 1. The two-inverter latch takes the Data value. When returning to 0, the RAM is in a memory state. READ CYCLE. In order to read the cell, the line Sel must be asserted. The RAM value propagates to Data, and its inverted value propagates to nData. SIMULATION. The simulation parameters correspond to the write cycle in the RAM. The simulation steps are as follows : Mem reaches 1, nMem 0 (unpredicatable value). Data gets to value 1 and nData to value 0. Sel is asserted. The memory cell reaches stays at 1. Data gets to a value of 0 and nData gets to a value of 1. Sel is still asserted. The memory cell gets 0. . Sel is inactive. The RAM is in a memory state. Simulate the RAM cell layout and check the results with that shown in Fig. 3. PRINT.

Complete RAM 4x4 Bit

You can duplicate the RAM cell into a 4x4 bit array using the command Edit -> Duplicate XY. Select the whole RAM cell and a new window appears. Enter the value 4 for X and 4 for Y into the menu. Click on Generate . The result is shown below. PRINT.

The row decoder is based on the schematic diagram of Fig. 5. One line is asserted while all the other lines are at zero. In this circuit one line was picked out from a choice of four lines. Using AND gates would be an easy solution, but in order to save the inverter, we chose NOR gates with inverted inputs. The layout of the row decoder is given in Figure 6. Click on File -> Read -> RamLineSelect.MSK to read it from C:\MICROWIND directory.

Simulate the layout of row selection circuit and check the results with that shown in Fig. 7. PRINT.

The NOR gate height should be adjusted to that of the RAM cell height. When making the final assembly between blocks, the command Edit -> Move Area is very important. This command helps to move a selected block with a lambda step. The column decoder is based on the same principles as those of the row decoder. The major modification is that the data flows both ways, that is firstly from the cell to the read circuit (Read cycle) and secondly from the write circuit to the cell (Write cycle). Fig. 8 proposes an architecture for this. The n-channel MOS device is used as a switch controlled by the column selection. When the n-channel MOS is on and Write is asserted, the data issued from DataIn is amplified by the buffer, flows from the bottom to the top and reaches the memory. If Write is off, the 3-state inverter is in high impedance, which allows one to read the information.

The final layout of the RAM 4x4 is proposed in Fig. 9. Click on File -> Read -> Ram44.MSK to read it from C:\MICROWIND directory. The simulation shown in Fig 10 proposes the read and write cycles at a specific RAM cell address. Perform the simulation and PRINT results.

The simulation of Fig. 10 can be described as follows. A [00] fixed line selection selects the upper line, that way sel0 is asserted while all others are at 0. The memory cells mem00 and mem01 do not reach the same initial state : mem00 gets to 0 and mem01 is at 1. When DataIn is at zero, writing a zero has no effect on Mem00. But when the column selection changes, DataIn=0 is copied to Mem01. When DataIn rises to 1 (t=10ns), and when write is 1, the memory cells change from 0 to 1. It is interesting to point out that the memory cell fights against the logic value before surrending and changing its internal state.

Complete RAM Chip

Click on the chip library icon and click on Pads. The window shown in Fig. 11 appears. Select the Pads Tab and the Pad ring option. A pad ring with 3 pads in X and 3 pads in Y is generated by a click on Generate Pad. In that case, a set of pads is added to your circuit. The VSS pad is situated at the bottom, and the VDD pad at the top with the associated power rings. Figure 12 displays an example of circuit with its input-output pads and interconnects. The chip contains a pad ring of 28 input/outputs (CHIP.MSK file). You open this example chip by clicking File -> Read -> Chip.MSK from C:\MICROWIND directory. Magnify the different to vuew how connenctions are made to the Pads with metal lines. Use the same technique (magnify and draw boxes) to connect various signal lines in your RAM layout to the Pads. Dont violate design rules. Connect all the Data, Address and Control (Write) lines of your RAM layout to the Pads and perform DRC. When clean, save and print the complete chip layout.

Generate CIF file

MICROWIND converts the MSK layout into CIF using a specific interface. The CIF file can be exported to various industrial software. The screen is shown below. The right table gives the correspondence between MICROWIND layers and CIF layers, the number of boxes in the layout and the corresponding over-etch. The over-etch is used to modify the final size of the CIF boxes in order to fit the exact design rules. Click on Convert to CIF to start conversion. Some parts of the result appear in the left window.

Demonstration and report

You must demonstrate your complete layout and simulation results to the lecturer during the practical class. You should also print the layout and simulation results, and get these signed by the lecturer during the class. You should submit these in the next class along with a cover sheet (clearly showing your ID number and name, course number and name, number and name of the practical assignment) and your comments on various aspects of the design/experiment for marking.

Das könnte Ihnen auch gefallen

- Architecture: MDCT CoreDokument5 SeitenArchitecture: MDCT Coregpa0007Noch keine Bewertungen

- TSTE12 Lab3 Microprogramming 101006Dokument5 SeitenTSTE12 Lab3 Microprogramming 101006Rezgin SharafanyNoch keine Bewertungen

- Sram Low Power DecoderDokument7 SeitenSram Low Power DecoderKedhar MallaNoch keine Bewertungen

- Memory PDFDokument16 SeitenMemory PDFWity WytiNoch keine Bewertungen

- ECE 198 JL Worksheet 8: Storage Elements: Random Access MemoryDokument6 SeitenECE 198 JL Worksheet 8: Storage Elements: Random Access MemoryShengyuan ZhongNoch keine Bewertungen

- ASIC-System On Chip-VLSI Design - SRAM Cell Design PDFDokument8 SeitenASIC-System On Chip-VLSI Design - SRAM Cell Design PDFGowtham SpNoch keine Bewertungen

- COA Module4Dokument35 SeitenCOA Module4puse1223Noch keine Bewertungen

- Flash MemoryDokument68 SeitenFlash Memoryshiva100% (1)

- Cmos Vlsi Design Lab 4: Full Chip Assembly: I. Core SchematicDokument5 SeitenCmos Vlsi Design Lab 4: Full Chip Assembly: I. Core SchematicdrhammoudaNoch keine Bewertungen

- Design of A 32x64-Bit SRAM - Background: Elad Alon 141Dokument9 SeitenDesign of A 32x64-Bit SRAM - Background: Elad Alon 141Christopher Patterson100% (1)

- 19bec149 Exp7 CaDokument8 Seiten19bec149 Exp7 CaZINZUVADIYA ABHISHEKNoch keine Bewertungen

- FPGA MemoryDokument9 SeitenFPGA MemoryNguyên Trịnh Vũ ĐăngNoch keine Bewertungen

- A 64 Bit Static RAM: Row Selection CircuitDokument7 SeitenA 64 Bit Static RAM: Row Selection CircuitChristopher PattersonNoch keine Bewertungen

- Semiconductor Memories: VLSI Design (18EC72)Dokument11 SeitenSemiconductor Memories: VLSI Design (18EC72)PraveenNoch keine Bewertungen

- Analysis and Design of Low Power Content Addressable Memory (CAM) CellDokument6 SeitenAnalysis and Design of Low Power Content Addressable Memory (CAM) CellNeha TripathiNoch keine Bewertungen

- Memory SystemsDokument93 SeitenMemory SystemsdeivasigamaniNoch keine Bewertungen

- Layout Manual - CMOS Inverter - Exp 3Dokument22 SeitenLayout Manual - CMOS Inverter - Exp 3ApoorvaNoch keine Bewertungen

- A Tutorial On Setting Up Electric Vlsi: Bits Pilani, Pilani-333031Dokument41 SeitenA Tutorial On Setting Up Electric Vlsi: Bits Pilani, Pilani-333031wicked_not_meNoch keine Bewertungen

- 06-Designing The Memory SystemDokument13 Seiten06-Designing The Memory SystemKhoa Pham0% (1)

- Welcome To International Journal of Engineering Research and Development (IJERD)Dokument6 SeitenWelcome To International Journal of Engineering Research and Development (IJERD)IJERDNoch keine Bewertungen

- Tutorial ModelingDokument45 SeitenTutorial ModelingRoxanaNoch keine Bewertungen

- An001-Driving Inmp001 LCDDokument14 SeitenAn001-Driving Inmp001 LCDnajiNoch keine Bewertungen

- ECD LabDokument35 SeitenECD LabRakesh kumarNoch keine Bewertungen

- MPS Lab Ex5-MemoryDokument10 SeitenMPS Lab Ex5-Memoryअमरेश झाNoch keine Bewertungen

- Design and Implementation of Static RAM Cell: Circuit Diagram of SRAMDokument4 SeitenDesign and Implementation of Static RAM Cell: Circuit Diagram of SRAMkomaladitya challaNoch keine Bewertungen

- Hardware Lecture 16Dokument4 SeitenHardware Lecture 16rinobiNoch keine Bewertungen

- Module 4Dokument28 SeitenModule 4Dr. Hadimani H.C.Noch keine Bewertungen

- Frequency Response of A CMOS Common-Source Amplifier: Experiment # 5Dokument10 SeitenFrequency Response of A CMOS Common-Source Amplifier: Experiment # 5Md. Sadique SheikhNoch keine Bewertungen

- VLSI Lab NewDokument19 SeitenVLSI Lab NewRajesh HarikrishnanNoch keine Bewertungen

- The Memory System: Fundamental ConceptsDokument115 SeitenThe Memory System: Fundamental ConceptsRajdeep ChatterjeeNoch keine Bewertungen

- comexam2مهمDokument28 Seitencomexam2مهمHappy JavaNoch keine Bewertungen

- QB UT3portionsDokument2 SeitenQB UT3portionspreethikabhaskarNoch keine Bewertungen

- HW Assignment 3Dokument8 SeitenHW Assignment 3Akshat JhaNoch keine Bewertungen

- 05 - Internal MemoryDokument63 Seiten05 - Internal MemoryKashif AmjadNoch keine Bewertungen

- Final Project DescriptionDokument3 SeitenFinal Project DescriptionVanlocTranNoch keine Bewertungen

- Internal Memory Organization (RAM& ROM)Dokument5 SeitenInternal Memory Organization (RAM& ROM)cloudNoch keine Bewertungen

- Moving Message Display SystemDokument33 SeitenMoving Message Display Systemvinod kapateNoch keine Bewertungen

- Montecarlo PDFDokument7 SeitenMontecarlo PDFSougata GhoshNoch keine Bewertungen

- Memory Address DecodingDokument25 SeitenMemory Address DecodingEkansh DwivediNoch keine Bewertungen

- DAY-15 Programmable Logic Devices PLD: Programmable Read Only Memory PROMDokument11 SeitenDAY-15 Programmable Logic Devices PLD: Programmable Read Only Memory PROMAnusha SagiNoch keine Bewertungen

- Module-5-Final GMITDokument20 SeitenModule-5-Final GMITmvs sowmyaNoch keine Bewertungen

- COA Module 4 BEC306CDokument16 SeitenCOA Module 4 BEC306Csachinksr007Noch keine Bewertungen

- Static RAMDokument235 SeitenStatic RAMAnjireddy ThatiparthyNoch keine Bewertungen

- ADS Tutorial On PCB Design To Layout: ECE 451 Automated Microwave Measurements LaboratoryDokument4 SeitenADS Tutorial On PCB Design To Layout: ECE 451 Automated Microwave Measurements Laboratoryten nheNoch keine Bewertungen

- COL215 Assignment 3: Title: Digital Image FilterDokument6 SeitenCOL215 Assignment 3: Title: Digital Image FilterKatia Rania BITAMNoch keine Bewertungen

- ,hrfikadsz NJSDFMV M VZDokument5 Seiten,hrfikadsz NJSDFMV M VZpalakNoch keine Bewertungen

- F12 Layout TutorialDokument18 SeitenF12 Layout TutorialAbuHarithHamzahNoch keine Bewertungen

- Display 8279Dokument37 SeitenDisplay 8279Muni Sankar MatamNoch keine Bewertungen

- Hardware Lecture 16Dokument4 SeitenHardware Lecture 16Taqi ShahNoch keine Bewertungen

- 6TSRAM Cell ReportDokument15 Seiten6TSRAM Cell ReportpalakNoch keine Bewertungen

- ADS Tutorial 1 PDFDokument29 SeitenADS Tutorial 1 PDFPuneeth yoganandaNoch keine Bewertungen

- Unit - 3: Unit-3, P-5 (Microprocessor & Microcontrollers) (ELE-355) 1Dokument5 SeitenUnit - 3: Unit-3, P-5 (Microprocessor & Microcontrollers) (ELE-355) 1kingraajaNoch keine Bewertungen

- Using The Siemens S65 DisplayDokument13 SeitenUsing The Siemens S65 DisplayMasoud Gheysari MNoch keine Bewertungen

- DocxDokument20 SeitenDocxmutindaNoch keine Bewertungen

- (New Paper On Sram) v39-15Dokument5 Seiten(New Paper On Sram) v39-15Pratap SaurabhNoch keine Bewertungen

- Nguyen Masters Report37Dokument1 SeiteNguyen Masters Report37PhiPhiNoch keine Bewertungen

- Emb C QB - Unit IiiDokument15 SeitenEmb C QB - Unit IiiANANTHI SNoch keine Bewertungen

- Master System Architecture: Architecture of Consoles: A Practical Analysis, #15Von EverandMaster System Architecture: Architecture of Consoles: A Practical Analysis, #15Noch keine Bewertungen

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationVon EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNoch keine Bewertungen

- PC Engine / TurboGrafx-16 Architecture: Architecture of Consoles: A Practical Analysis, #16Von EverandPC Engine / TurboGrafx-16 Architecture: Architecture of Consoles: A Practical Analysis, #16Noch keine Bewertungen

- Tutorial 2 - 3Dokument2 SeitenTutorial 2 - 3Ahan TejaswiNoch keine Bewertungen

- Nguyenvanthinh BKC13107 N01Dokument35 SeitenNguyenvanthinh BKC13107 N01Văn thinh NguyenNoch keine Bewertungen

- Lean MerchandizingDokument16 SeitenLean MerchandizingKartik SinghNoch keine Bewertungen

- Lesson 6 ExercisesDokument2 SeitenLesson 6 ExercisesLoyaltyNoch keine Bewertungen

- BR4144A.8 英 (conector)Dokument1 SeiteBR4144A.8 英 (conector)Victor GuzmanNoch keine Bewertungen

- 2 ChapterDokument42 Seiten2 Chaptersunil kumarNoch keine Bewertungen

- Bootable USBDokument5 SeitenBootable USBZvonimir BatrnekNoch keine Bewertungen

- 38smss4 Specification For Coupling Capacitor Voltage Transformer and or Carrier Coupler CapacitorDokument20 Seiten38smss4 Specification For Coupling Capacitor Voltage Transformer and or Carrier Coupler CapacitorengrandyNoch keine Bewertungen

- Erc111 DKRCC - Es.rl0.e3.02 520H8596Dokument24 SeitenErc111 DKRCC - Es.rl0.e3.02 520H8596Miguel BascunanNoch keine Bewertungen

- Sarmasoftwareservices-Hyderabad. Mobile:9949210713. MM Process FlowDokument4 SeitenSarmasoftwareservices-Hyderabad. Mobile:9949210713. MM Process FlowSARMANoch keine Bewertungen

- Kmu Cat Rollnoslip 263112Dokument1 SeiteKmu Cat Rollnoslip 263112Saeed AkhtarNoch keine Bewertungen

- En Rhel Deploy Oracle Rac Database 12c Rhel 7Dokument50 SeitenEn Rhel Deploy Oracle Rac Database 12c Rhel 7Alessandro SilveiraNoch keine Bewertungen

- Innovation and TechnologyDokument8 SeitenInnovation and TechnologyMuthomi DenisNoch keine Bewertungen

- Concord 4 Quick Install GuideDokument12 SeitenConcord 4 Quick Install Guidebill080808Noch keine Bewertungen

- JSON Data Modeling: Matthew D. Groves, @mgrovesDokument56 SeitenJSON Data Modeling: Matthew D. Groves, @mgrovesGorzilloNoch keine Bewertungen

- Checklist For FormworkDokument1 SeiteChecklist For Formworkmojeed bolajiNoch keine Bewertungen

- Figure 1. Schematic Diagram of The IOT System: DigitalinputDokument5 SeitenFigure 1. Schematic Diagram of The IOT System: DigitalinputCristian Măndică100% (2)

- T & C Fastener Co, LTD.: Certified Material Test ReportDokument1 SeiteT & C Fastener Co, LTD.: Certified Material Test Reportlady romeroNoch keine Bewertungen

- TEMS Investigation 24.1.1 - Release NoteDokument21 SeitenTEMS Investigation 24.1.1 - Release NoteMuhammad Usman100% (1)

- Jan Marie Valencia Kharla Baladjay Recca Anna Laranan Rex Martin GuceDokument46 SeitenJan Marie Valencia Kharla Baladjay Recca Anna Laranan Rex Martin GuceElsie AdornaNoch keine Bewertungen

- Online Recruitment SystemDokument42 SeitenOnline Recruitment SystemTanmay Abhijeet74% (19)

- Chapter 10 - Wave Propagation in Satellite CommunicationDokument28 SeitenChapter 10 - Wave Propagation in Satellite CommunicationQuang HưngNoch keine Bewertungen

- Lab 3 Abowd and Beales Framework FormatDokument2 SeitenLab 3 Abowd and Beales Framework FormatPhilipNoch keine Bewertungen

- LW SeriesDokument8 SeitenLW SeriesAbraham AutomationNoch keine Bewertungen

- Could Not Connect Unable To Find Driver Net - Sourceforge.jtds - Jdbc.driverDokument3 SeitenCould Not Connect Unable To Find Driver Net - Sourceforge.jtds - Jdbc.driverEze Alexander IkNoch keine Bewertungen

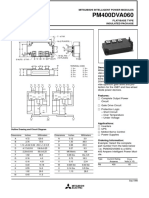

- PM400DVA060: Mitsubishi Intelligent Power ModulesDokument6 SeitenPM400DVA060: Mitsubishi Intelligent Power ModulesDiego GrisalesNoch keine Bewertungen

- Plagarisim Report1Dokument54 SeitenPlagarisim Report1Maulik JainNoch keine Bewertungen

- Sm-A405fn SVC Manual PDFDokument116 SeitenSm-A405fn SVC Manual PDFBojanNoch keine Bewertungen

- An Essay On Software Testing For Quality AssuranceDokument9 SeitenAn Essay On Software Testing For Quality AssurancekualitatemNoch keine Bewertungen

- tw250 1Dokument50 Seitentw250 1pribadi socojatiNoch keine Bewertungen