Beruflich Dokumente

Kultur Dokumente

Ep 550 Ps

Hochgeladen von

kapilhaliOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Ep 550 Ps

Hochgeladen von

kapilhaliCopyright:

Verfügbare Formate

Eureka Technology

Product Summary

EP550 SDIO/SD Memory/MMC Host Controller

FEATURES

Host controller for Secure Digital (SD), SDIO, SD combo, and MultiMedia Card (MMC) bus. Allows host CPU to access SD and MMC devices. Compatible with SD 2.0, including high capacity (SDHC) and 8-bit MMC 4.2 specifications. Many choices of CPU interfaces, including AHB, APB, SH4, Wishbone, PCI and generic user interface. Supports SDMA operation with option to remove SDMA for very small gate count implementation. Selectable data buffer size from 512 to 16Kbytes. Hardware support of CRC error detection and interrupt generation. Supports multi-function SD cards including command suspend, resume, and read wait. Option to operate user interface and card control at different clock domains. Supports all SD-enabled operating systems including Windows. Free source code included for bus driver development. Fully sythesizable code ideal for ASIC and FPGA implementations. Fully static design with edge triggered flip-flops.

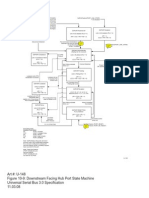

BLOCK DIAGRAM

Data Buffer DMA Control (Optional) SD Host Control Control Registers SD card Interface

Optional Interface Bus Master

Standard CPU or Generic user interface

Bus Slave

Copyright by Eureka Technology Inc. 4962 El Camino Real, Los Altos, CA 94022, USA

Page 1

Tel: 1 650 960 3800 Fax: 1 650 960 3805 http://www.eurekatech.com

Eureka Technology

EP550 SD/SDIO/MMC Host Controller

Description

The EP550 is a host controller for SD memory, SDIO, SD combo and MMC interface. The core connects the host CPU of the system to the SD card socket. External SD cards can be accessed by the host CPU through the EP550 controller IP core. SD memory and SDIO are low cost, high speed interfaces designed for removable mass storage and IO devices. It is a very flexible architecture supporting variable clock rate and 1 to 4-bit SD data width. Data rate up to 25Mbyte/sec (200Mbs) can be realized with SD interface. The MMC standard allows up to 8-bit of parallel data to be transferred with data rate of 50Mbyte/sec. Features such as plug and play, auto-detection, error correction, write protection are standard with SD card interface and supported by the EP550. The EP550 SD card host controller core is designed according to the SD Associations latest SD host controller specification (version 2.0). The core presents itself as a standard register set to the OS and application software. To access the SD card, the host CPU simply issue read/write access to the control registers in the core. The controllers core handles all the SD card protocol automatically including data shifting, timing and CRC generation. The core has an optional DMA controller so that data can be automatically transferred between the system and the SD card without CPU intervention. Because it supports the standard SD register set, the EP550 is automatically recognized by any operating systems that supports the SD bus. No driver development is needed. In applications where there is no operating system of the OS does not have built-in SD support, Eureka provides free source code to help user develop the bus driver. There are several options for user hardware interface to the controller core. The controller supports generic user interface optimized for on-chip logic interface as well as embedded CPU interface such as AMBA AHB and APB bus, Wishbone, SH4, PCI and generic address/data interface. With the EP550, SD card interface can be realized with very little development cost and effort. Designer can add SD memory and SDIO interface to the system by simply adding the EP550 module without impacting the rest of the system architecture.

Free Source Code

The EP550 implements the standard SD host controller register set which supports any standard operating systems that supports SD bus. For applications where the user need to develop its own SD driver software, Eureka provides free source code for driver development.

Copyright by Eureka Technology Inc. 4962 El Camino Real, Los Altos, CA 94022, USA

Page 2

Tel: 1 650 960 3800 Fax: 1 650 960 3805 http://www.eurekatech.com

Eureka Technology

EP550 SD/SDIO/MMC Host Controller

Optional Features

The EP550 standard core features a simple generic user interface which can be connected easily into any design. In addition, Eureka also offer the EP550 with AHB, APB, SH4, Wishbone and PCI bus interface. For certain interfaces, the bus interface may operate at a different clock domain from the SD host controller. The core is also available with and without DMA.

ACTEL DEVICE UTILIZATION DATA

Family ProASIC3 Axcelerator IGLOO Fusion Device (-speed grade) A3P1000-2 AX1000-2 AGL600V5 AFS1500 SEQ 900 894 996 900 Utilization COMB 3392 2090 3633 3429 Total 17% 16% 33% 11% RAM 2 2 2 2 53Mhz 59Mhz 34Mhz 56Mhz Performance

Copyright by Eureka Technology Inc. 4962 El Camino Real, Los Altos, CA 94022, USA

Page 3

Tel: 1 650 960 3800 Fax: 1 650 960 3805 http://www.eurekatech.com

Das könnte Ihnen auch gefallen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (345)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- GTM Datalayer2Dokument62 SeitenGTM Datalayer2Gaurav Dutt100% (1)

- SynTest Tutorial TSDokument1 SeiteSynTest Tutorial TSkapilhaliNoch keine Bewertungen

- Address Translation, Caches, and TlbsDokument32 SeitenAddress Translation, Caches, and TlbskapilhaliNoch keine Bewertungen

- ThermoMatrix 10K Temperature SensorDokument1 SeiteThermoMatrix 10K Temperature SensorkapilhaliNoch keine Bewertungen

- ECN 003 (Reset Propagation) FigureDokument1 SeiteECN 003 (Reset Propagation) FigurekapilhaliNoch keine Bewertungen

- Elc2013 ClementDokument40 SeitenElc2013 ClementkapilhaliNoch keine Bewertungen

- Tier 1 Investor Guidance 1Dokument45 SeitenTier 1 Investor Guidance 1kapilhaliNoch keine Bewertungen

- Integration of Hardware Cryptography Acceleration On Embedded Systems Under Linux 2.6Dokument6 SeitenIntegration of Hardware Cryptography Acceleration On Embedded Systems Under Linux 2.6kapilhaliNoch keine Bewertungen

- ELM - How To Use An MMCDokument8 SeitenELM - How To Use An MMCkapilhaliNoch keine Bewertungen

- Group 9 - Assignment P - Ai PresentationDokument23 SeitenGroup 9 - Assignment P - Ai Presentationapi-608841407Noch keine Bewertungen

- SOLIDWORKS MBD Endorsement EckenrodeDokument6 SeitenSOLIDWORKS MBD Endorsement EckenrodeHamid HojatiNoch keine Bewertungen

- Data Networks by Dimitri Bertsekas&Robert Gallager PDFDokument500 SeitenData Networks by Dimitri Bertsekas&Robert Gallager PDFRishav Chakraborty25% (4)

- Keo ReportDokument22 SeitenKeo ReportJoshua EvansNoch keine Bewertungen

- Assam Big DataDokument26 SeitenAssam Big DataSourabhAgarwalNoch keine Bewertungen

- Deconstructing Multi-Processors: That, Random, Generates, Computer and ProgramDokument3 SeitenDeconstructing Multi-Processors: That, Random, Generates, Computer and Programmdp anonNoch keine Bewertungen

- Installing Computer Systems and Network.Dokument72 SeitenInstalling Computer Systems and Network.Justin BurnNoch keine Bewertungen

- Sql4codesys enDokument3 SeitenSql4codesys envonnetNoch keine Bewertungen

- As 126558 FD-H Im B80GB WW GB 2122 3Dokument16 SeitenAs 126558 FD-H Im B80GB WW GB 2122 3Tim MarvinNoch keine Bewertungen

- CIS Microsoft SQL Server 2019 Benchmark v1.0.0 PDFDokument100 SeitenCIS Microsoft SQL Server 2019 Benchmark v1.0.0 PDFConciencia ImmortalNoch keine Bewertungen

- Improving ASM Disk Discovery Time PDFDokument8 SeitenImproving ASM Disk Discovery Time PDFTanviAgrawalNoch keine Bewertungen

- Priyanka - Nilakhe - Automation - Performance - Testing - 6 - Experience - Long1 - Priyanka NilakheDokument3 SeitenPriyanka - Nilakhe - Automation - Performance - Testing - 6 - Experience - Long1 - Priyanka NilakheNipun PruthiNoch keine Bewertungen

- Wago-I/O-System 750: ManualDokument62 SeitenWago-I/O-System 750: ManualAlexNoch keine Bewertungen

- A Student Attendance System With Fingerprint Scanner Integration For Strathmore UniversityDokument81 SeitenA Student Attendance System With Fingerprint Scanner Integration For Strathmore UniversitySandro Zinga Dos santosNoch keine Bewertungen

- Blue - Box To FreePBX - BlueDokument2 SeitenBlue - Box To FreePBX - Blueaddo_Noch keine Bewertungen

- Biostar Biostation SDK Manual v1.1Dokument111 SeitenBiostar Biostation SDK Manual v1.1Rajesh RamakrishnanNoch keine Bewertungen

- DosxlinuxDokument4 SeitenDosxlinuxPrinston Del CampoNoch keine Bewertungen

- VXI-11 SpecDokument66 SeitenVXI-11 SpecppatstewNoch keine Bewertungen

- Automation KivaDokument25 SeitenAutomation KivaAnirudh KowthaNoch keine Bewertungen

- STM 32 Cubef 1Dokument3 SeitenSTM 32 Cubef 1thuandvt97Noch keine Bewertungen

- Control Statements in RDokument34 SeitenControl Statements in Rajith kumar n.k.bNoch keine Bewertungen

- Scala Quick ReferenceDokument6 SeitenScala Quick ReferenceJohn GodoiNoch keine Bewertungen

- The Zachman FrameworkDokument3 SeitenThe Zachman FrameworkLois Rajas100% (1)

- Catálogo Temporizadores - English VersionDokument22 SeitenCatálogo Temporizadores - English VersionbrunoserratNoch keine Bewertungen

- Generate Number Sequence Using Chain of CommandDokument5 SeitenGenerate Number Sequence Using Chain of CommandDynamic Netsoft TechnologiesNoch keine Bewertungen

- SAP ABAP Interview Questions Top 50Dokument7 SeitenSAP ABAP Interview Questions Top 50pal singhNoch keine Bewertungen

- TMS320 C 50Dokument774 SeitenTMS320 C 50tnj_dineshNoch keine Bewertungen

- Band in A Box 2016 ManualDokument644 SeitenBand in A Box 2016 Manualmartzo-0% (1)

- 2900 H EN RM Drystar 5500 PDFDokument270 Seiten2900 H EN RM Drystar 5500 PDFNelson AltuveNoch keine Bewertungen