Beruflich Dokumente

Kultur Dokumente

The Inverse-Narrow-Width Effect: Ieee Electron Device Letters, Vol. Edl-I, No. JULY 1986 419

Hochgeladen von

Vijay Shankar PandeyOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

The Inverse-Narrow-Width Effect: Ieee Electron Device Letters, Vol. Edl-I, No. JULY 1986 419

Hochgeladen von

Vijay Shankar PandeyCopyright:

Verfügbare Formate

IEEE ELECTRON DEVICE LETTERS, VOL. EDL-I, NO.

I, JULY 1986

419

The Inverse-Narrow-Width Effect

Abstract-For the first time an analytical expression can simulate the inverse-narrow-width effect. The inverse-narrow-width effect is a reduction in the thresholdvoltage of aMOSFET with decreasing channel width. We compare the model with experimental threshold voltage data from small-geometry PMOS devices with fully recessed isolation oxides and an inverse-narrow-width effect is predicted.

I. INTRODUCTIOK

LSI and even ULSI densities can result from scaling the size of MOSFETs to nearand submicrometer dimensions. As the size the individual device decreases, the of sensitivityof variousdeviceparameters withgeometryincreases. Many previously neglected second-order effects become dominant. Parameter variations have a severe impact on device behavior and must be predictable. One important device parameter that has been studied as a function of device size is the threshold voltage. Circuit noise margins, speed, and required node voltages require an accurate predication of the threshold voltage. Threshold voltage variations resulting from scaling the channel length have been extensively investigated. Akers and Sanchez reviewed this work in [l]. Simple elegant yet geometrical models to complete two-dimensionalcomputers models can simulate this effect. The influence of the channel width on threshold voltage variations has also been studied. Analytical expressions can simulate variations these for nonrecessed [2]and semirecessed (LOCOS) [3] isolation oxide structures.Forthesestructures, reducing the devicewidth increasesthethresholdvoltage.Thisbehavior defines the narrow-width effect. VLSI and ULSI densities require devices only withshort not channels and narrow widths, but with small active area pitch. This requiresbirds-beak-freenonencroaching isolation oxides. Fully recessed isolation oxides meet these requirements. Onlyalimited amount of work reporting thresholdvoltage variations as a function of width in structures these is available. Sugino Akers and [4] used two-dimensional a computer model to simulate the effects of the angleofthe isolation oxide on the subthreshold current.They predicted the electrostaticpotentialwould increase near the edges of the channelin fully recessed oxidestructures.This causes the threshold voltage to decrease for decreasing width. Shigyo et al. [5] and Akers Hsueh and [6] using three-dimensional computermodels reportedsimilarresults. Sugino et al. [7]

Manuscript received Februaty 25, 1986: revised April 25; 1986. This work was supported in part by the Semiconductor Research Corporation. The author is with the Center for Solid State Electronics, Arizona State University, Tempe, A 2 85287. IEEE Log Number 8609388.

gave experimental verification of this effect. The reduction in the threshold voltage as the width decreases defines the inverse-narrow-width effect. Previously, no analytical expression could simulate the inverse-narrow-widtheffect.Threshold voltage simulations required a complex multidimensional computer model. In this letter, a simple yet reasonably accurate expression is derived to simulate the threshold voltage of a small-geometry MOSFET with a fully recessed isolation oxide. We compare the modelwith experimental data from small-geometry PMOS devices and an inverse-narrow-width effect is predicted. 11. THRESHOLD VOLTAGE DERIVATION The threshold voltage expression for a large-geometry MOSFET results from applying the charge conservation law in the region bounded by the gate electrode and the semiconductor bulk. The sum of this charge is

Qm+Qf-(Qn+Qb)=O

(1)

where Qm is the charge on the polysilicon gate electrode, Qf is the fixed charge in the Si02, Qn is the inversion layer charge due to the free carriers induced in the channel region, and Q b is the ionized impurity concentration in the depletion region. The definition of the threshold voltage [I] implies Qn 4 Qb. Applying Gauss law to (1) for an n-channel device gives

g J

v~+

$s

+ Qb/Cg

(2)

where V f , is the flat-band voltage, i l i S is the surface potential, and Cg is the gate capacitance. At threshold, the surface potential locks at approximately W 6 , Therefore the threshold voltage for a large-geometry MOSFET is given by

vf=vn+ 246 + Qb/Cg.

(3)

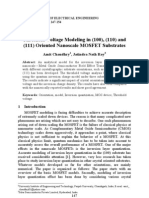

Equation (3) is valid for channel lengths longer than the source and drain depletion depths, and widths wider than the depth of the gate-induced depletion region. Fig. 1 illustrates the surface potential of a MOSFET with fully recessed isolation oxides. Notice the enhanced potentials at the edges of the channel. This is caused by fringing gate fields terminating on the sidewalls of the channel. The gate capacitance used in (3) normally is considered ideal and its capacitance is calculated using the parallel-plate approximation. For the device used in Fig. 1, the fringing fields neglected by the parallel-plate approximation are significant and must be included in C,. We model the total gate capacitance as a gate capacitor in parallel with two sidewall capacitors. The interface charge along both the thin and the field oxide-silicon boundary is considered uniform and

0741-3106/86/0700-0419$01.00 0 1986IEEE

Authorized licensed use limited to: IEEE Trans on Electron Devices Editors. Downloaded on January 2, 2009 at 05:56 from IEEE Xplore. Restrictions apply.

420

IEEE ELECTROS DEVICE LETTERS.

Poly Gate

B

VOL. EDL-7, NO. 7, JULY 1986 A Y

Td

plane

(a)

B

U

Poly Gate

u1

Fig. 1. Surface potential of a MOSFET with fully recessed isolation oxide L = 0.75 pm, W = 1.5 pm, and V, = 0.1 V.

w piane

Fig. 2 .

(b) (a) Channel edge. (b) Transformed into parallel-plate configuration.

constant. Hence the total gate capacitance is

c,= co.y(L )+ 2Cf W

( ) The argument of the natural logarithm can be simplified to 4

give

where C,, is the thin gate oxide capacitance per unit area, L is thechannellength, W isthe devicewidth,and Cy is the fringing capacitance. First,considerthelong-channelnarrow-widthMOSFET case. Fig. 2(a) illustrates one side of thechannel.Thegate electrode overlaps the recessed oxide by OL. The thin oxide has a. thickness of To,$ and the field oxide has a thickness of T,. While potential the in the inversion along layer the sidewallis constant, the potential will drop to the substrate potential after the inversion layer collapses. Since the inversion capacitance is larger than the depletion Capacitance, we approximatethepotentialalongthecompletedepth of the sidewall to be constant derive use inversion and and the capacitance for this structure. This assumption will cause the fringing capacitance Cy to be overestimated. The structure in Fig. 2(a) is transformed into the structure in Fig. 2(bj by the transformation [8]

Cy=(2c0,L/a) In (2 Td/Tox).

Therefore the total gate capacitance can be expressed as

(8)

C, = Cox( WL.) (4~,,L/n) In (2 Td/T,,)

or

(9)

C,=C,,(

WL)(l+ F / W )

(10)

where the fringing factor F is

F = (4 T O x / r ) (2 T,/T,,). In

Hencethethresholdvoltageforalong-channelnarrowwidth NMOS device is

(1 1)

z = sin

(T

w/2j

(5)

where z and w represent complex planes. In the w plane, Cf is obtained from the parallel-plate formula as

c,=E,,A/(Ug

-U])

(6)

where E,, the permittivityof the Si02, and A is the plate area is in the w plane. Realizing the fringing field component cannot extend past T,, C, in the original z plane is

with Qb = qN, W, WL, where q is the electronic charge, is N, the channel doping concentration, and Wdis the depth of the gate-induced depletion region. Including short-channel the effect in (12) the allows simulation of a small-geometry MOSFET. The bulk charge term Qbdecreases as the channel length decreases. This results from charge sharing the with source drain and depletion regions. The amount of depletion charge that terminates the gate field may be approximated as being in a trapezoid region [9]. This trapezoid area is

C,= (2cO,L/7r) In

(d(Td/TOx)- i- Td/T,,). 1

(7)

where ri isthejunctiondepth.

AKERS: INVERSE-NARROW-WIDTH EFFECT

DATA MODEL

42 1

DATA MODEL

MODEL-

DATA X

.96

ABS&l)(volts)

regions. It could alsoindicatea more accuratecapacitance expression is needed takes which into account possible nonuniform variation in the interface charge at the channel edges andalong the sidewallsand in thevariation in the potential along the sidewalls. IV. CONCLUSION A closed-form analytical expression for the threshold voltage of a small-geometry MOSFET with a fully recessed isolation oxide was derived. The threshold voltage expression was derived by modeling the gate capacitance to include the fringing fields. gate We compare the threshold voltage expression experimental with data from small-geometry PMOS devicesand an inverse-narrow-widtheffectis predicted. ACKNOWLEDGMENT The author would like to thank the people in SRDL and ATC at Motorola for processing the wafers and Dr. Lund, J. Ford, and D. Munk for all their help. REFERENCES

[ l ] L. A. Akers and J. J. Sanchez,Threshold voltage models of short, narrow, and small geometry MOSFETs: review. A Solid-state Electron., vol. 25, pp. 621-641, 1982. [2] L. A . Akers, An analytical expression for the threshold voltage of a small geometry MOSFET. Solid-state Electron., vol. 24. pp. 621627, 1981. [3] L.A.Akers, M. M. Beguwala! and F. Z. Custode,A model of a narrow-width MOSFET including tapered oxide and doping encroachment, ZEEE Trans. Electron Devices, vol. ED-28, pp. 1490-1495, 1981. [4] M. Sugino and L. A. Akers, Subthreshold currents in oxide isolated structures; ZEEE Electron Device Lett., vol. EDL-4, p. 114, 1983. [5] N. Shigyo, M. Konaka. and R. L. M. Dang, Three dimensional simulation of inverse narrow-channel effect, Electron. Lett., vol. 18, no. 6, p. 274, 1982. A three-dimensional MOSFET simula[6] L.A.AkersandK.Hsueh. tor, SZAM Tech. Abstr., p. 22A, 1985. Ford, Optimum p-channel [7] M. Sugino, L. A. Akers, and J. M. isolation structure for CMOS, ZEEE Trans. Electron Devices, vol. ED-31> pp. 1823-1829,1984. [8] M. Spiegel, Theory and Problems of Complex Variables. New York:McGraw-Hill:1964. [9] L.D.Yau, A simple theory to predict the threshold voltage of shortchannel IGFETs, Solid-State Electron., vol. 16, p. 1059, 1974.

.86

6 7 8 WIDM(MICR~NS)

Fig. 3.

Comparison of PMOS threshold voltage data (symbols) with model (lines). L = 0.75 lm.

Integrating (13) over thewidth of thedevice givesthe depletion charge volume. Hence, the small-geometry threshold voltage expression for an n-channel MOSFET with a fully recessed isolation oxide is

[l - ( v 1 + 2 W d / r j - l ) ( r j / L ) ]W / ( W + F ) ] . (14) [ 111. EXPERIMENTAL VERIFICATION P-channel devices fabricated were as described in [7]. Devices were tested using aHP 4145A. The threshold voltages were measured by an extrapolation of the incremental slope of the Id - vg curve with Vd fixed at 100 mV.Fig. 3 is a comparison of PMOS threshold voltage data from three different die with (14). The appropriate signs were changed in (14)for PMOS. As discussed in [7], the NMOS devices in this lot had a sidewall doping causing V, to increase as the width decreased. Below 3 pm, the model overestimates the threshold voltage. While the exact cause for this is unknown, it could result from confinement of the depletion region in the narrow widths the and interaction of adjacent sidewall depletion

Authorized licensed use limited to: IEEE Trans on Electron Devices Editors. Downloaded on January 2, 2009 at 05:56 from IEEE Xplore. Restrictions apply.

Das könnte Ihnen auch gefallen

- Dual-Frequency Modified C/V Technique: 150 125 100 7 5 1 50 25 / I 15MW/600nmDokument2 SeitenDual-Frequency Modified C/V Technique: 150 125 100 7 5 1 50 25 / I 15MW/600nmkurabyqldNoch keine Bewertungen

- Gate Tunneling Current and Quantum Effects in Deep Scaled MosfetsDokument5 SeitenGate Tunneling Current and Quantum Effects in Deep Scaled Mosfetsashishj1083Noch keine Bewertungen

- MOS Integrated Circuit DesignVon EverandMOS Integrated Circuit DesignE. WolfendaleNoch keine Bewertungen

- Analysis of An Aperture Coupled Micro StripDokument8 SeitenAnalysis of An Aperture Coupled Micro StripYamtarNoch keine Bewertungen

- Sedra Chapter5Dokument111 SeitenSedra Chapter5Gustavo Omar Mesones Málaga100% (2)

- Mosfet ScalingDokument0 SeitenMosfet ScalingKeith FernandesNoch keine Bewertungen

- 557 161 PDFDokument5 Seiten557 161 PDFbanoshamshad786Noch keine Bewertungen

- Ieee On Delivery,: Vol. 10, 1, January 3 65Dokument9 SeitenIeee On Delivery,: Vol. 10, 1, January 3 65Alejandro Ramirez BenitesNoch keine Bewertungen

- Fowler Nordheim Tunneling in Thin SiO2 FilmsDokument7 SeitenFowler Nordheim Tunneling in Thin SiO2 FilmskobelkNoch keine Bewertungen

- Multisection Bandpass Filters Using Capacitively Loaded Transmission LinesDokument6 SeitenMultisection Bandpass Filters Using Capacitively Loaded Transmission LinesKapil SaraswatNoch keine Bewertungen

- 1990 Richard Alpha Power Law Mosfet Model PDFDokument11 Seiten1990 Richard Alpha Power Law Mosfet Model PDFrahmanakberNoch keine Bewertungen

- Subthreshold Conduction in Mosfet'S: Acknowledgment A. KDokument14 SeitenSubthreshold Conduction in Mosfet'S: Acknowledgment A. KshanujgargNoch keine Bewertungen

- FE-Modelling of Induction Tool Responses: F Iii: GDokument4 SeitenFE-Modelling of Induction Tool Responses: F Iii: GtomhowNoch keine Bewertungen

- 540 130 PDFDokument5 Seiten540 130 PDFNava KrishnanNoch keine Bewertungen

- " (+) L' - ( ) 'U M-L ( ) : Characteristic Impedance of A Wide Slotline On Low-Permittivity SubstratesDokument3 Seiten" (+) L' - ( ) 'U M-L ( ) : Characteristic Impedance of A Wide Slotline On Low-Permittivity SubstratesepicfheilNoch keine Bewertungen

- 1.1654509 Tunneling in A Finite Superlattice PDFDokument4 Seiten1.1654509 Tunneling in A Finite Superlattice PDFKadu BritoNoch keine Bewertungen

- A Double-Tail Latch-Type Voltage Sense Amplifier With 18ps Setup+Hold TimeDokument3 SeitenA Double-Tail Latch-Type Voltage Sense Amplifier With 18ps Setup+Hold TimeWang TianyangNoch keine Bewertungen

- Circular WaveguideDokument19 SeitenCircular WaveguideLam DinhNoch keine Bewertungen

- DC Characteristics of A MOS Transistor (MOSFET) : Solved With COMSOL Multiphysics 4.4Dokument18 SeitenDC Characteristics of A MOS Transistor (MOSFET) : Solved With COMSOL Multiphysics 4.4shree_rs81Noch keine Bewertungen

- Single Electron Transistors With Sidewall Depletion Gates On A Silicon-On-Insulator Quantum WireDokument2 SeitenSingle Electron Transistors With Sidewall Depletion Gates On A Silicon-On-Insulator Quantum Wire9semNoch keine Bewertungen

- Particle-In-Cell Simulation of A Novel High Power Terahertz Vacuum Electron DeviceDokument6 SeitenParticle-In-Cell Simulation of A Novel High Power Terahertz Vacuum Electron Deviceharun hakshiNoch keine Bewertungen

- Practical Wide Frequency Approach For CalculatingDokument6 SeitenPractical Wide Frequency Approach For Calculatingmichael gorgeNoch keine Bewertungen

- ° Bogazici University PressDokument8 Seiten° Bogazici University PressaysevrimNoch keine Bewertungen

- An Active, Microfabricated, Scalp Electrode Array For EEG RecordingDokument6 SeitenAn Active, Microfabricated, Scalp Electrode Array For EEG RecordingChristopher RoblesNoch keine Bewertungen

- Session 3: Solid State Devices I MOS and Fet (A) : Wednesday, Oct. 18 P.M. To SheratonDokument2 SeitenSession 3: Solid State Devices I MOS and Fet (A) : Wednesday, Oct. 18 P.M. To SheratonManda Praveen KumarNoch keine Bewertungen

- Konstantin P. Shamrai and Shunjiro Shinohara - Modeling Electromagnetic Field Excitation and RF Power Absorption in A Large Helicon PlasmaDokument4 SeitenKonstantin P. Shamrai and Shunjiro Shinohara - Modeling Electromagnetic Field Excitation and RF Power Absorption in A Large Helicon PlasmaHimaszNoch keine Bewertungen

- Vftos in GISDokument5 SeitenVftos in GISdeepak_27Noch keine Bewertungen

- Millimeter-Wave Dual-Band Microstrip Patch Antennas Using Multilayer Gaas TechnologyDokument4 SeitenMillimeter-Wave Dual-Band Microstrip Patch Antennas Using Multilayer Gaas TechnologyShivanandKalmaniNoch keine Bewertungen

- Coaxial Pulse TransformerDokument3 SeitenCoaxial Pulse Transformer77nicuNoch keine Bewertungen

- Engg Approach To Design of Tapered Dielectric Rod Horn AntDokument9 SeitenEngg Approach To Design of Tapered Dielectric Rod Horn Antవేలుసామి లింగాసామిNoch keine Bewertungen

- Microelectronic CircuitDokument696 SeitenMicroelectronic CircuitImtiaz AhmedNoch keine Bewertungen

- MesfetDokument4 SeitenMesfetManogya SharmaNoch keine Bewertungen

- Design of Microstrip Lowpass Filters With Wide Stopband and High AttenuationDokument2 SeitenDesign of Microstrip Lowpass Filters With Wide Stopband and High AttenuationBhargav BikkaniNoch keine Bewertungen

- 1177 2687 1 SMDokument10 Seiten1177 2687 1 SMkamilawehbeNoch keine Bewertungen

- The Quantized Hall Effect: 2 Two-Dimensional Electron GasDokument31 SeitenThe Quantized Hall Effect: 2 Two-Dimensional Electron GaskiokoNoch keine Bewertungen

- Scattering in Nanotransistors: A Numerical Study: Alexei Svizhenko and M. P. AnantramDokument20 SeitenScattering in Nanotransistors: A Numerical Study: Alexei Svizhenko and M. P. AnantramKarunan BathoorNoch keine Bewertungen

- Passive Gyrotron Cavity Loading and Frequency ShiftDokument22 SeitenPassive Gyrotron Cavity Loading and Frequency ShiftAlexandr BabaskinNoch keine Bewertungen

- COMMUNICATION LAB Project (EC304) : K. Srikar Siddarth (181EC218)Dokument28 SeitenCOMMUNICATION LAB Project (EC304) : K. Srikar Siddarth (181EC218)siddsidNoch keine Bewertungen

- Impact of Mosfet Parameters On Its Parasitic Capacitances: Presented byDokument27 SeitenImpact of Mosfet Parameters On Its Parasitic Capacitances: Presented bysattuhappyNoch keine Bewertungen

- 65 Caprio ElecLett 1973Dokument2 Seiten65 Caprio ElecLett 1973kurabyqldNoch keine Bewertungen

- SAW& ComsolDokument5 SeitenSAW& Comsollabirint10Noch keine Bewertungen

- A Simple Model For Quantisation Effects IN Heavily-Doped Silicon Mosfets at Inversion ConditionsDokument4 SeitenA Simple Model For Quantisation Effects IN Heavily-Doped Silicon Mosfets at Inversion ConditionsmodasshirNoch keine Bewertungen

- Mec 10ec63 Ssic Unit2Dokument18 SeitenMec 10ec63 Ssic Unit2Noorullah ShariffNoch keine Bewertungen

- Conclusion:: To DiagnosticsDokument3 SeitenConclusion:: To DiagnosticsDhaval PatelNoch keine Bewertungen

- Exam MEP1553 Apr2010Dokument7 SeitenExam MEP1553 Apr2010Abid JamaliNoch keine Bewertungen

- Calculation of The Electric Field On An Insulator String Using The Finite Elements MethodDokument4 SeitenCalculation of The Electric Field On An Insulator String Using The Finite Elements Methodostojic007Noch keine Bewertungen

- Ursi03 AntDokument5 SeitenUrsi03 AntBezawada PrabhakarNoch keine Bewertungen

- Electrooptically-Active Slow-Light-Enhanced Silicon Slot Photonic Crystal WaveguidesDokument4 SeitenElectrooptically-Active Slow-Light-Enhanced Silicon Slot Photonic Crystal Waveguidesyuvabala2002123Noch keine Bewertungen

- Pid00050 2 CmosDokument8 SeitenPid00050 2 CmosSaurabh ChakravartyNoch keine Bewertungen

- A008 Digest StefanSoroohanDokument2 SeitenA008 Digest StefanSoroohanAnonymous NyeLgJPMbNoch keine Bewertungen

- Ee Lab ReportDokument25 SeitenEe Lab Reportsamuel_r_butlerNoch keine Bewertungen

- Thin Gate Oxide Damage Due To Plasma ProcessingDokument12 SeitenThin Gate Oxide Damage Due To Plasma ProcessingEşref TürkmenNoch keine Bewertungen

- Operation of Single-Walled Carbon Nanotube As A Radio-Frequency Single-Electron TransistorDokument5 SeitenOperation of Single-Walled Carbon Nanotube As A Radio-Frequency Single-Electron TransistorNisha AgrawalNoch keine Bewertungen

- Single Electron Transistor (SET)Dokument8 SeitenSingle Electron Transistor (SET)mokhaladNoch keine Bewertungen

- Threshold Voltage Modeling in (100), (110) and (111) Oriented Nanoscale MOSFET SubstratesDokument8 SeitenThreshold Voltage Modeling in (100), (110) and (111) Oriented Nanoscale MOSFET SubstratesprashantvlsiNoch keine Bewertungen

- 2019 Problems in Electromagnetics Vol 1Dokument35 Seiten2019 Problems in Electromagnetics Vol 1soumengoswami10Noch keine Bewertungen

- Reducing Simultaneous Switching Noise and EMI On Ground Power Planes by Dissipative Edge TerminationDokument10 SeitenReducing Simultaneous Switching Noise and EMI On Ground Power Planes by Dissipative Edge TerminationApikShafieeNoch keine Bewertungen

- I, and I, and Zref Separately We Measured Changes of AboutDokument5 SeitenI, and I, and Zref Separately We Measured Changes of AboutBodhayan PrasadNoch keine Bewertungen

- (M4-MAIN) - Pulse Response of Coaxial LinesDokument8 Seiten(M4-MAIN) - Pulse Response of Coaxial LinesLanceDavidNoch keine Bewertungen

- Electronic Devices and Circuits: The Commonwealth and International Library: Electrical Engineering Division, Volume 1Von EverandElectronic Devices and Circuits: The Commonwealth and International Library: Electrical Engineering Division, Volume 1Noch keine Bewertungen

- Appendix - Equations v3Dokument4 SeitenAppendix - Equations v3ALEN chiaNoch keine Bewertungen

- Operations ManagementDokument18 SeitenOperations ManagementMd. Shadman AminNoch keine Bewertungen

- PST30 - PST300 In-Line: Circuit DiagramsDokument4 SeitenPST30 - PST300 In-Line: Circuit DiagramsMa LhNoch keine Bewertungen

- Differential Relay: Power System ProtectionDokument12 SeitenDifferential Relay: Power System ProtectionAbdallah DaldoomNoch keine Bewertungen

- Dunki Jacobs1972 TopDokument8 SeitenDunki Jacobs1972 TopMatheus dos Reis BravimNoch keine Bewertungen

- Unloading Relief ValvesDokument6 SeitenUnloading Relief ValvesStar SealNoch keine Bewertungen

- manual.8000.1D.EVO .ENGLISHDokument8 Seitenmanual.8000.1D.EVO .ENGLISHJC GamePlayNoch keine Bewertungen

- Waffle Slab Ribbed SlabDokument28 SeitenWaffle Slab Ribbed Slabهلالي وافتخرNoch keine Bewertungen

- PN Junction Diode: Electronic Circuits (18NPC304) Assignment 2 Part - 1Dokument2 SeitenPN Junction Diode: Electronic Circuits (18NPC304) Assignment 2 Part - 1Narendran SrinivasanNoch keine Bewertungen

- Battery Crimping Tool Ez 400 Instruction ManualDokument16 SeitenBattery Crimping Tool Ez 400 Instruction ManualComparir PicsNoch keine Bewertungen

- User Manual of Product 1:: Lowrance 000-10802-001 Skimmer Transom Mount Tranducer For Lss-2 Structurescan HD FishfinderDokument17 SeitenUser Manual of Product 1:: Lowrance 000-10802-001 Skimmer Transom Mount Tranducer For Lss-2 Structurescan HD Fishfinder薛泽绵Noch keine Bewertungen

- ECG1200G Technical Specification CaltalogDokument3 SeitenECG1200G Technical Specification CaltalogShaaibNoch keine Bewertungen

- Eurosens Display CAN Manual 1 - 0Dokument25 SeitenEurosens Display CAN Manual 1 - 0AndreiNoch keine Bewertungen

- CONTROL UNIT TMC - 230 - /11: DM - TurretsDokument22 SeitenCONTROL UNIT TMC - 230 - /11: DM - TurretsVladimir100% (4)

- Modulation Techniques in Inverters: Advanced Power Electronics and Applications ECEG 6309Dokument44 SeitenModulation Techniques in Inverters: Advanced Power Electronics and Applications ECEG 6309Meng FenNoch keine Bewertungen

- Pid ControllerDokument1 SeitePid ControllerOsamaNoch keine Bewertungen

- EURO36-CB Rv00Dokument2 SeitenEURO36-CB Rv00Ahcène MezghicheNoch keine Bewertungen

- Modifying An IC735 For The 630m BandDokument9 SeitenModifying An IC735 For The 630m BandJuan Carlos AbasoloNoch keine Bewertungen

- P-15 Scales: Calibration and Field Service ManualDokument19 SeitenP-15 Scales: Calibration and Field Service ManualGustavo BiancalanaNoch keine Bewertungen

- 5 Hard Time and Maintenance ChecksDokument3 Seiten5 Hard Time and Maintenance ChecksWilly Gr100% (1)

- G5 AML Sa01818wi - 1907Dokument14 SeitenG5 AML Sa01818wi - 1907locoboeingNoch keine Bewertungen

- Beginning FPGA Programming - Partie51Dokument5 SeitenBeginning FPGA Programming - Partie51ali alilouNoch keine Bewertungen

- Assignment 2 Prestressed Concrete DesignDokument1 SeiteAssignment 2 Prestressed Concrete DesignPippen DialaNoch keine Bewertungen

- ACS601 Manual PDFDokument92 SeitenACS601 Manual PDFJNoch keine Bewertungen

- Panasonic's Basic Electrical Safety TipsDokument13 SeitenPanasonic's Basic Electrical Safety TipsRobert Oconer AguilarNoch keine Bewertungen

- Chapter 28Dokument23 SeitenChapter 28Reparting Unit IE ClubNoch keine Bewertungen

- SMD CodesDokument13 SeitenSMD Codesrafalero1Noch keine Bewertungen

- Circulating-Current-Excited Switched Reluctance Generator System With Diode RectifierDokument10 SeitenCirculating-Current-Excited Switched Reluctance Generator System With Diode Rectifierlinnan sunNoch keine Bewertungen

- 19eec44 - Analog Integrated Circuits and ApplicationsDokument2 Seiten19eec44 - Analog Integrated Circuits and ApplicationsKarunakaran M,47Noch keine Bewertungen