Beruflich Dokumente

Kultur Dokumente

Instruction Set

Hochgeladen von

Dinesh KumarOriginalbeschreibung:

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Instruction Set

Hochgeladen von

Dinesh KumarCopyright:

Verfügbare Formate

PIC16F87X

DS30292B-page 138 = 1999 Microchip Technology Inc.

TABLE 13-2: PIC16CXXX INSTRUCTION SET

Mnemonic,

Operands

Description Cycles 14-Bit Opcode Status

Affected

Notes

MSb LSb

BYTE-ORIENTED FILE REGISTER OPERATIONS

ADDWF

ANDWF

CLRF

CLRW

COMF

DECF

DECFSZ

INCF

INCFSZ

IORWF

MOVF

MOVWF

NOP

RLF

RRF

SUBWF

SWAPF

XORWF

f, d

f, d

f

-

f, d

f, d

f, d

f, d

f, d

f, d

f, d

f

-

f, d

f, d

f, d

f, d

f, d

Add W and f

AND W with f

Clear f

Clear W

Complement f

Decrement f

Decrement f, Skip if 0

Increment f

Increment f, Skip if 0

Inclusive OR W with f

Move f

Move W to f

No Operation

Rotate Left f through Carry

Rotate Right f through Carry

Subtract W from f

Swap nibbles in f

Exclusive OR W with f

1

1

1

1

1

1

1(2)

1

1(2)

1

1

1

1

1

1

1

1

1

C,DC,Z

Z

Z

Z

Z

Z

Z

Z

Z

C

C

C,DC,Z

Z

1,2

1,2

2

1,2

1,2

1,2,3

1,2

1,2,3

1,2

1,2

1,2

1,2

1,2

1,2

1,2

BIT-ORIENTED FILE REGISTER OPERATIONS

BCF

BSF

BTFSC

BTFSS

f, b

f, b

f, b

f, b

Bit Clear f

Bit Set f

Bit Test f, Skip if Clear

Bit Test f, Skip if Set

1

1

1 (2)

1 (2)

1,2

1,2

3

3

LITERAL AND CONTROL OPERATIONS

ADDLW

ANDLW

CALL

CLRWDT

GOTO

IORLW

MOVLW

RETFIE

RETLW

RETURN

SLEEP

SUBLW

XORLW

k

k

k

-

k

k

k

-

k

-

-

k

k

Add literal and W

AND literal with W

Call subroutine

Clear Watchdog Timer

Go to address

Inclusive OR literal with W

Move literal to W

Return from interrupt

Return with literal in W

Return from Subroutine

Go into standby mode

Subtract W from literal

Exclusive OR literal with W

1

1

2

1

2

1

1

2

2

2

1

1

1

C,DC,Z

Z

TO,PD

Z

TO,PD

C,DC,Z

Z

Note 1: When an I/O register is modified as a function of itself ( e.g., ), the value used will be that value present

on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external

device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned

to the Timer0 Module.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is

executed as a .

Note: Additional information on the mid-range instruction set is available in the PICmicro Mid-Range MCU Family

Reference Manual (DS33023).

= 1999 Microchip Technology Inc. DS30292B-page 139

PIC16F87X

13.1 Instruction Descriptions

ADDLW Add LiteraI and W

Syntax: [ ] ADDLW k

Operands: 0 } k } 255

Operation: (W) + k r (W)

Status Affected: C, DC, Z

Description: The contents of the W register

are added to the eight bit literal 'k'

and the result is placed in the W

register.

ADDWF Add W and f

Syntax: [ ] ADDWF f,d

Operands: 0 } f } 127

d R

Operation: (W) + (f) r (destination)

Status Affected: C, DC, Z

Description: Add the contents of the W register

with register 'f'. If 'd' is 0, the result

is stored in the W register. If 'd' is

1, the result is stored back in reg-

ister 'f'.

ANDLW AND LiteraI with W

Syntax: [ ] ANDLW k

Operands: 0 } k } 255

Operation: (W) .AND. (k) r (W)

Status Affected: Z

Description: The contents of W register are

ANDed with the eight bit literal

'k'. The result is placed in the W

register.

ANDWF AND W with f

Syntax: [ ] ANDWF f,d

Operands: 0 } f } 127

d R

Operation: (W) .AND. (f) r (destination)

Status Affected: Z

Description: AND the W register with register

'f'. If 'd' is 0, the result is stored in

the W register. If 'd' is 1, the result

is stored back in register 'f'.

BCF Bit CIear f

Syntax: [ ] BCF f,b

Operands: 0 } f } 127

0 } b } 7

Operation: 0 r (f<b>)

Status Affected: None

Description: Bit 'b' in register 'f' is cleared.

BSF Bit Set f

Syntax: [ ] BSF f,b

Operands: 0 } f } 127

0 } b } 7

Operation: 1 r (f<b>)

Status Affected: None

Description: Bit 'b' in register 'f' is set.

PIC16F87X

DS30292B-page 140 = 1999 Microchip Technology Inc.

BTFSS Bit Test f, Skip if Set

Syntax: [ ] BTFSS f,b

Operands: 0 } f } 127

0 } b < 7

Operation: skip if (f<b>) = 1

Status Affected: None

Description: If bit 'b' in register 'f' is '0', the next

instruction is executed.

If bit 'b' is '1', then the next instruc-

tion is discarded and a is exe-

cuted instead making this a 2TCY

instruction.

BTFSC Bit Test, Skip if CIear

Syntax: [ ] BTFSC f,b

Operands: 0 } f } 127

0 } b } 7

Operation: skip if (f<b>) = 0

Status Affected: None

Description: If bit 'b' in register 'f' is '1', the next

instruction is executed.

If bit 'b', in register 'f', is '0', the

next instruction is discarded, and

a is executed instead, making

this a 2TCY instruction.

CALL CaII Subroutine

Syntax: [ ] CALL k

Operands: 0 } k } 2047

Operation: (PC)+ 1r TOS,

k r PC<10:0>,

(PCLATH<4:3>) r PC<12:11>

Status Affected: None

Description: Call Subroutine. First, return

address (PC+1) is pushed onto

the stack. The eleven bit immedi-

ate address is loaded into PC bits

<10:0>. The upper bits of the PC

are loaded from PCLATH. is

a two cycle instruction.

CLRF CIear f

Syntax: [ ] CLRF f

Operands: 0 } f } 127

Operation: 00h r (f)

1 r Z

Status Affected: Z

Description: The contents of register 'f' are

cleared and the Z bit is set.

CLRW CIear W

Syntax: [ ] CLRW

Operands: None

Operation: 00h r (W)

1 r Z

Status Affected: Z

Description: W register is cleared. Zero bit (Z)

is set.

CLRWDT CIear Watchdog Timer

Syntax: [ ] CLRWDT

Operands: None

Operation: 00h r WDT

0 r WDT prescaler,

1 r TO

1 r PD

Status Affected: TO, PD

Description: instruction resets the

Watchdog Timer. It also resets

the prescaler of the WDT. Status

bits TO and PD are set.

= 1999 Microchip Technology Inc. DS30292B-page 141

PIC16F87X

COMF CompIement f

Syntax: [ ] COMF f,d

Operands: 0 } f } 127

d R [0,1]

Operation: (f) r (destination)

Status Affected: Z

Description: The contents of register 'f' are

complemented. If 'd' is 0, the

result is stored in W. If 'd' is 1, the

result is stored back in register 'f'.

DECF Decrement f

Syntax: [ ] DECF f,d

Operands: 0 } f } 127

d R [0,1]

Operation: (f) - 1 r (destination)

Status Affected: Z

Description: Decrement register 'f'. If 'd' is 0,

the result is stored in the W regis-

ter. If 'd' is 1, the result is stored

back in register 'f'.

DECFSZ Decrement f, Skip if 0

Syntax: [ ] DECFSZ f,d

Operands: 0 } f } 127

d R [0,1]

Operation: (f) - 1 r (destination);

skip if result = 0

Status Affected: None

Description: The contents of register 'f' are

decremented. If 'd' is 0, the result

is placed in the W register. If 'd' is

1, the result is placed back in reg-

ister 'f'.

If the result is 1, the next instruc-

tion is executed. If the result is 0,

then a is executed instead

making it a 2TCY instruction.

GOTO UnconditionaI Branch

Syntax: [ ] GOTO k

Operands: 0 } k } 2047

Operation: k r PC<10:0>

PCLATH<4:3> r PC<12:11>

Status Affected: None

Description: is an unconditional branch.

The eleven bit immediate value is

loaded into PC bits <10:0>. The

upper bits of PC are loaded from

PCLATH<4:3>. is a two

cycle instruction.

INCF Increment f

Syntax: [ ] INCF f,d

Operands: 0 } f } 127

d R [0,1]

Operation: (f) + 1 r (destination)

Status Affected: Z

Description: The contents of register 'f' are

incremented. If 'd' is 0, the result

is placed in the W register. If 'd' is

1, the result is placed back in reg-

ister 'f'.

INCFSZ Increment f, Skip if 0

Syntax: [ ] INCFSZ f,d

Operands: 0 } f } 127

d R [0,1]

Operation: (f) + 1 r (destination),

skip if result = 0

Status Affected: None

Description: The contents of register 'f' are

incremented. If 'd' is 0, the result is

placed in the W register. If 'd' is 1,

the result is placed back in regis-

ter 'f'.

If the result is 1, the next instruc-

tion is executed. If the result is 0, a

is executed instead making it

a 2TCY instruction.

PIC16F87X

DS30292B-page 142 = 1999 Microchip Technology Inc.

IORLW IncIusive OR LiteraI with W

Syntax: [ ] IORLW k

Operands: 0 } k } 255

Operation: (W) .OR. k r (W)

Status Affected: Z

Description: The contents of the W register are

ORed with the eight bit literal 'k'.

The result is placed in the W reg-

ister.

IORWF IncIusive OR W with f

Syntax: [ ] IORWF f,d

Operands: 0 } f } 127

d R [0,1]

Operation: (W) .OR. (f) r (destination)

Status Affected: Z

Description: Inclusive OR the W register with

register 'f'. If 'd' is 0 the result is

placed in the W register. If 'd' is 1

the result is placed back in regis-

ter 'f'.

MOVF Move f

Syntax: [ ] MOVF f,d

Operands: 0 } f } 127

d R [0,1]

Operation: (f) r (destination)

Status Affected: Z

Description: The contents of register f are

moved to a destination dependant

upon the status of d. If d = 0, des-

tination is W register. If d = 1, the

destination is file register f itself. d

= 1 is useful to test a file register

since status flag Z is affected.

MOVLW Move LiteraI to W

Syntax: [ ] MOVLW k

Operands: 0 } k } 255

Operation: k r (W)

Status Affected: None

Description: The eight bit literal 'k' is loaded

into W register. The dont cares

will assemble as 0s.

MOVWF Move W to f

Syntax: [ ] MOVWF f

Operands: 0 } f } 127

Operation: (W) r (f)

Status Affected: None

Description: Move data from W register to reg-

ister 'f'.

NOP No Operation

Syntax: [ ] NOP

Operands: None

Operation: No operation

Status Affected: None

Description: No operation.

= 1999 Microchip Technology Inc. DS30292B-page 143

PIC16F87X

RETFIE Return from Interrupt

Syntax: [ ] RETFIE

Operands: None

Operation: TOS r PC,

1 r GIE

Status Affected: None

RETLW Return with LiteraI in W

Syntax: [ ] RETLW k

Operands: 0 } k } 255

Operation: k r (W);

TOS r PC

Status Affected: None

Description: The W register is loaded with the

eight bit literal 'k'. The program

counter is loaded from the top of

the stack (the return address).

This is a two cycle instruction.

RETURN Return from Subroutine

Syntax: [ ] RETURN

Operands: None

Operation: TOS r PC

Status Affected: None

Description: Return from subroutine. The stack

is POPed and the top of the stack

(TOS) is loaded into the program

counter. This is a two cycle

instruction.

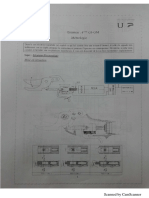

RLF Rotate Left f through Carry

Syntax: [ ] RLF f,d

Operands: 0 } f } 127

d R [0,1]

Operation: See description below

Status Affected: C

Description: The contents of register 'f' are

rotated one bit to the left through

the Carry Flag. If 'd' is 0, the

result is placed in the W register.

If 'd' is 1, the result is stored back

in register 'f'.

RRF Rotate Right f through Carry

Syntax: [ ] RRF f,d

Operands: 0 } f } 127

d R [0,1]

Operation: See description below

Status Affected: C

Description: The contents of register 'f' are

rotated one bit to the right through

the Carry Flag. If 'd' is 0, the result

is placed in the W register. If 'd' is

1, the result is placed back in reg-

ister 'f'.

SLEEP

Syntax: [

]

SLEEP

Operands: None

Operation: 00h r WDT,

0 r WDT prescaler,

1 r TO,

0 r PD

Status Affected: TO, PD

Description: The power-down status bit, PD is

cleared. Time-out status bit, TO

is set. Watchdog Timer and its

prescaler are cleared.

The processor is put into SLEEP

mode with the oscillator stopped.

Register f C

Register f C

PIC16F87X

DS30292B-page 144 = 1999 Microchip Technology Inc.

SUBLW Subtract W from LiteraI

Syntax: [ ]

SUBLW k

Operands: 0 } k } 255

Operation: k - (W) r W)

Status Affected: C, DC, Z

Description: The W register is subtracted (2s

complement method) from the

eight bit literal 'k'. The result is

placed in the W register.

SUBWF Subtract W from f

Syntax: [ ]

SUBWF f,d

Operands: 0 } f } 127

d R [0,1]

Operation: (f) - (W) r destination)

Status Affected: C, DC, Z

Description: Subtract (2s complement method)

W register from register 'f'. If 'd' is 0,

the result is stored in the W regis-

ter. If 'd' is 1, the result is stored

back in register 'f'.

SWAPF Swap NibbIes in f

Syntax: [ ] SWAPF f,d

Operands: 0 } f } 127

d R [0,1]

Operation: (f<3:0>) r (destination<7:4>),

(f<7:4>) r (destination<3:0>)

Status Affected: None

Description: The upper and lower nibbles of

register 'f' are exchanged. If 'd' is

0, the result is placed in W regis-

ter. If 'd' is 1, the result is placed in

register 'f'.

XORLW ExcIusive OR LiteraI with W

Syntax: [ ]

XORLW k

Operands: 0 } k } 255

Operation: (W) .XOR. k r W)

Status Affected: Z

Description: The contents of the W register

are XORed with the eight bit lit-

eral 'k'. The result is placed in

the W register.

XORWF ExcIusive OR W with f

Syntax: [ ] XORWF f,d

Operands: 0 } f } 127

d R [0,1]

Operation: (W) .XOR. (f) r destination)

Status Affected: Z

Description: Exclusive OR the contents of the

W register with register 'f'. If 'd' is

0, the result is stored in the W

register. If 'd' is 1, the result is

stored back in register 'f'.

Das könnte Ihnen auch gefallen

- Kaschke PPYDokument23 SeitenKaschke PPYSameer YadavNoch keine Bewertungen

- Note de Calcul Convoyeur MarocDokument10 SeitenNote de Calcul Convoyeur MarocAkram FerchichiNoch keine Bewertungen

- CometDokument581 SeitenCometnhuannd67Noch keine Bewertungen

- Arm Cortex-M3 Processor DatasheetDokument10 SeitenArm Cortex-M3 Processor DatasheetthuhienktvNoch keine Bewertungen

- Relatório R4 - SE SapeaçuDokument23 SeitenRelatório R4 - SE Sapeaçusanjeevpnd439Noch keine Bewertungen

- Suzlon: Capstone Project Report OnDokument28 SeitenSuzlon: Capstone Project Report OnReshma GuptaNoch keine Bewertungen

- QCM PDFDokument185 SeitenQCM PDFRania MabroukNoch keine Bewertungen

- AcpDokument69 SeitenAcprizcst9759Noch keine Bewertungen

- COMSOLDokument17 SeitenCOMSOLfarah jenhaniNoch keine Bewertungen

- Firmware Version V4.2 Released For S7-1200 CPUsDokument2 SeitenFirmware Version V4.2 Released For S7-1200 CPUsdgfjkhNoch keine Bewertungen

- Badr Kasbaoui: About MeDokument1 SeiteBadr Kasbaoui: About MeabdorafikNoch keine Bewertungen

- Ds Panther6x6neuDokument2 SeitenDs Panther6x6neuForum PompieriiNoch keine Bewertungen

- INET Wireless TutorialDokument3 SeitenINET Wireless Tutorialruacon35Noch keine Bewertungen

- PT Activity 2.5.1: Basic Switch Configuration: TopologyDokument9 SeitenPT Activity 2.5.1: Basic Switch Configuration: TopologyYuliani Indah Purnama SariNoch keine Bewertungen

- 2505 E Course - Communication Technology 7 Modem Methods ASK, FSK, PSKDokument2 Seiten2505 E Course - Communication Technology 7 Modem Methods ASK, FSK, PSKJohn Adam Cayanan DesuasidoNoch keine Bewertungen

- Realized By:: Class: Internship PeriodDokument24 SeitenRealized By:: Class: Internship Periodabir bzNoch keine Bewertungen

- Config Et Use Rslogix500Dokument76 SeitenConfig Et Use Rslogix500Fogape TitiNoch keine Bewertungen

- Matlab Exercise 2a-2bDokument2 SeitenMatlab Exercise 2a-2bAyman SalehNoch keine Bewertungen

- Ua5000 Ipmsan NGN Service ConfigurationDokument21 SeitenUa5000 Ipmsan NGN Service ConfigurationHudzrul NizamNoch keine Bewertungen

- ADC Part B ProgramsDokument12 SeitenADC Part B ProgramsSahana ShaviNoch keine Bewertungen

- Password Protection Using PIC Microcontroller - The Engineering ProjectsDokument10 SeitenPassword Protection Using PIC Microcontroller - The Engineering ProjectsTeo JavaNoch keine Bewertungen

- Photo Electric SensorDokument176 SeitenPhoto Electric SensorAlfiansyah Dharma Setia Djaketra100% (1)

- Code Omnet++Dokument6 SeitenCode Omnet++Eugenius IusNoch keine Bewertungen

- Hierarchical PlanningDokument21 SeitenHierarchical PlanningmkNoch keine Bewertungen

- Ece 321 Lecture RevDokument158 SeitenEce 321 Lecture RevPaolo TuazonNoch keine Bewertungen

- Airtable - Ipynb - ColaboratoryDokument4 SeitenAirtable - Ipynb - ColaboratoryVesselin NikovNoch keine Bewertungen

- FHPP Positioning Library TIADokument43 SeitenFHPP Positioning Library TIAMartin Guzman100% (1)

- Getting Started With De-Series BoardsDokument7 SeitenGetting Started With De-Series BoardsAke NilsiamNoch keine Bewertungen

- Sales Forecasting Using Kernel Based Support Vector Machine AlgorithmDokument6 SeitenSales Forecasting Using Kernel Based Support Vector Machine AlgorithmjomasoolNoch keine Bewertungen

- Redressement Contrôlé Monophasé Simple Alternance: Exercice 1Dokument4 SeitenRedressement Contrôlé Monophasé Simple Alternance: Exercice 1Ay OùbNoch keine Bewertungen

- Stage Azrou SaniDokument32 SeitenStage Azrou Saninoussayba elkhadar100% (1)

- Consommi TounsiDokument83 SeitenConsommi TounsiSami KrifaNoch keine Bewertungen

- Leak Test 01CT3PEVLMB Spain+ Engleza + RomanaDokument5 SeitenLeak Test 01CT3PEVLMB Spain+ Engleza + RomanaBoeroaia GeorgianNoch keine Bewertungen

- Piano OoDokument14 SeitenPiano OoAfser RahumanNoch keine Bewertungen

- StipDokument22 SeitenStipLatisha WalkerNoch keine Bewertungen

- Simplex Method Using MATLAB PDFDokument5 SeitenSimplex Method Using MATLAB PDFEhsan ElahiNoch keine Bewertungen

- Transfinite InterpolationDokument5 SeitenTransfinite Interpolationdev burmanNoch keine Bewertungen

- Dáp Án Test1Dokument24 SeitenDáp Án Test1Dương ĐạtNoch keine Bewertungen

- Howto - Junos Olive 12.1R1.9 For Vmware: 1) Create A New VMDokument5 SeitenHowto - Junos Olive 12.1R1.9 For Vmware: 1) Create A New VMarjanditoNoch keine Bewertungen

- Rapport PFE Smart Lead Generation Scrum EnglishDokument134 SeitenRapport PFE Smart Lead Generation Scrum Englishbhkacem souhaNoch keine Bewertungen

- Packet Tracer - VLSM Design and Implementation PracticeDokument2 SeitenPacket Tracer - VLSM Design and Implementation PracticeFiya CalmaNoch keine Bewertungen

- Tic Tac ToeDokument28 SeitenTic Tac Toelouis benNoch keine Bewertungen

- Lab 2 QUBE-Servo Filtering Workbook (Student)Dokument3 SeitenLab 2 QUBE-Servo Filtering Workbook (Student)Luis Enriquez0% (2)

- Mda Win Pic2Dokument231 SeitenMda Win Pic2Meraz AhmedNoch keine Bewertungen

- Fill in The Blanks With The Correct Tense (Simple Past or Past Progressive)Dokument1 SeiteFill in The Blanks With The Correct Tense (Simple Past or Past Progressive)Диана КрестинскаяNoch keine Bewertungen

- DSK 6713 CCS V5.5 ProcedureDokument7 SeitenDSK 6713 CCS V5.5 ProcedureNida WaheedNoch keine Bewertungen

- Table Loi NormaleDokument2 SeitenTable Loi NormaleTony M'BHAYABONoch keine Bewertungen

- Examen Metrologie PDFDokument9 SeitenExamen Metrologie PDFBotayna Kadim100% (1)

- Cours 4 - ActivitésDokument36 SeitenCours 4 - Activitésmor ndiayeNoch keine Bewertungen

- 9.1.3 Packet Tracer - Identify MAC and IP AddressesDokument3 Seiten9.1.3 Packet Tracer - Identify MAC and IP AddressesJosetjNoch keine Bewertungen

- ACP CommandeDokument1 SeiteACP CommandeZa KiaNoch keine Bewertungen

- Europass Curriculum Vitae: Personal Information Noureddine BoujnahDokument4 SeitenEuropass Curriculum Vitae: Personal Information Noureddine Boujnahنورالدين بوجناح100% (1)

- A Brief History of Real Time Embedded SystemDokument27 SeitenA Brief History of Real Time Embedded SystemPradeepdarshan PradeepNoch keine Bewertungen

- Invector Third Person Controller - Basic Locomotion GuideDokument34 SeitenInvector Third Person Controller - Basic Locomotion GuideJaneNoch keine Bewertungen

- Ripex M enDokument173 SeitenRipex M enRoh OJNoch keine Bewertungen

- What Is Codename OneDokument18 SeitenWhat Is Codename OneنورالدنياNoch keine Bewertungen

- Assembly LanguageDokument7 SeitenAssembly LanguageDilip JhaNoch keine Bewertungen

- 3 Pic16f877 InstructDokument8 Seiten3 Pic16f877 InstructAdel DouDouNoch keine Bewertungen

- Instrucciones Del Pic16f84Dokument15 SeitenInstrucciones Del Pic16f84Gaston Rodrigo PotenzaNoch keine Bewertungen

- CHP 5 Pic Micro Controller Instruction SetDokument75 SeitenCHP 5 Pic Micro Controller Instruction Setsetup.143Noch keine Bewertungen

- WinForms TrueDBGridDokument362 SeitenWinForms TrueDBGridgusvader100% (1)

- IEEE'S STD - LOGIC - 1164 Quick Reference CardDokument2 SeitenIEEE'S STD - LOGIC - 1164 Quick Reference CardILikeScribd5050Noch keine Bewertungen

- Aspen Simulation WorkbookDokument24 SeitenAspen Simulation Workbookwalisyh100% (2)

- Post Codes of BhutanDokument4 SeitenPost Codes of BhutanGyamba Dukpa50% (2)

- Avaya Integrated Management Release 6.0 Site Administration Installation and UpgradeDokument20 SeitenAvaya Integrated Management Release 6.0 Site Administration Installation and UpgradeJo JojoNoch keine Bewertungen

- AnyBody Tutorial 2011 V5Dokument229 SeitenAnyBody Tutorial 2011 V5nishantsinghbmeNoch keine Bewertungen

- Good Practice Contract Management FrameworkDokument30 SeitenGood Practice Contract Management Frameworkmohammedviqhas35410% (1)

- Unit 3 Question Bank Final Web TechnologyDokument7 SeitenUnit 3 Question Bank Final Web TechnologyRithika M NagendiranNoch keine Bewertungen

- Introduction To Programming: Seif Haridi KTHDokument44 SeitenIntroduction To Programming: Seif Haridi KTHengineer_khaula7035Noch keine Bewertungen

- 23-08-19 Investigation Report For OOSDokument2 Seiten23-08-19 Investigation Report For OOSDeepak67% (3)

- Pythonwith Spyder An Experiential Learning PerspectiveDokument230 SeitenPythonwith Spyder An Experiential Learning PerspectivePriya kambleNoch keine Bewertungen

- Barangay Service Management SystemDokument5 SeitenBarangay Service Management SystemJohn Paulo AragonesNoch keine Bewertungen

- Boarding PassDokument1 SeiteBoarding Passagoyal5145Noch keine Bewertungen

- Liquid PerformanceDokument5 SeitenLiquid PerformanceYoseph Sianturi100% (2)

- C 1942940Dokument511 SeitenC 1942940abreddy2003Noch keine Bewertungen

- Introduction To Fuzzy SetDokument2 SeitenIntroduction To Fuzzy SetTria Putri NoviasariNoch keine Bewertungen

- Sistema de Registo e Login Com PHP e MySqlDokument3 SeitenSistema de Registo e Login Com PHP e MySqltzaraujoNoch keine Bewertungen

- GX Work 2Dokument9 SeitenGX Work 2Hanafi HariyantoNoch keine Bewertungen

- HOw To Login To RNCDokument10 SeitenHOw To Login To RNCRashid MagorwaNoch keine Bewertungen

- PTC-Mathcad Software Blog: 3 Time Saving Tips Every Civil Engineer NeedsDokument8 SeitenPTC-Mathcad Software Blog: 3 Time Saving Tips Every Civil Engineer NeedsPriyanka BasuNoch keine Bewertungen

- Data Loss Prevention SoftwareDokument5 SeitenData Loss Prevention SoftwareSeth936276772Noch keine Bewertungen

- TCP-IP Guide V1-0Dokument32 SeitenTCP-IP Guide V1-0John GreenNoch keine Bewertungen

- Neo-Newbie Mar 17, 11 at 7:07pm: ScizoreonDokument3 SeitenNeo-Newbie Mar 17, 11 at 7:07pm: ScizoreonChiara OlivoNoch keine Bewertungen

- Agent State FlowchartsDokument8 SeitenAgent State FlowchartseworkflowNoch keine Bewertungen

- IBM VTL 7500 Intro & Planning GuideDokument143 SeitenIBM VTL 7500 Intro & Planning Guidemeghach80Noch keine Bewertungen

- Digital Entrepreneurship Program: Course-Career-IncomeDokument15 SeitenDigital Entrepreneurship Program: Course-Career-IncomeSuyog PatilNoch keine Bewertungen

- 6.solid State Storage MediaDokument5 Seiten6.solid State Storage MediaSam ManNoch keine Bewertungen

- Cisco UCS To Brocade Connectivity Guide: White PaperDokument33 SeitenCisco UCS To Brocade Connectivity Guide: White Paper5songNoch keine Bewertungen

- TMPKDokument11 SeitenTMPKRuswanto RiswanNoch keine Bewertungen

- Komal Devi CVDokument8 SeitenKomal Devi CVMuhammed Amjad IslamNoch keine Bewertungen