Beruflich Dokumente

Kultur Dokumente

MSAP Project So

Hochgeladen von

Bernardo SoOriginalbeschreibung:

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

MSAP Project So

Hochgeladen von

Bernardo SoCopyright:

Verfügbare Formate

Extended SAP Computer Architecture

Bernardo F. So Jr. Daisy Agpawa ECE617 Advanced Microprocessors Department of Electronics and Communications Engineering De La Salle University, Manila bernardo_so_jr@yahoo.com.ph, daisy_agpawa@yahoo.com

. INTRODUCTION This paper details an 8-bit Microprocessor architecture and implementation. The design is based on the Simple-AsPossible computer by Albert Malvino, explained in Digital Conputer Electronics (1992). This is a pedagogical architecture meant to introduce students to the basics of computer design. This paper extends the instruction set of SAP from four instructions to 4 instructions to 16 instructions. The following explains the features of the design:

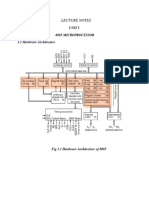

Figure 1 describes the overall block diagram of the system (see figure 9 for full size figure). There are 9 basic components, with the control unit implemented by a finite state machine. The control unit is responsible for the enable signals of the registers, and control of the ALU. A. Program counter

46.95 MHZ maximum clock speed(verilog implementation) 8-bit wide data bus, 16-bit instructions Maximum of 256 instructions 256 bytes of RAM 4 bi-directional 8-bit ports Basic instruction set, with data transfer, arithmetic and logic (no multiply/divide), and branch instructions Multi-cycle instructions (instructions take several clock pulses) . SYSTEM DESIGN

The program counter is a parallel-in, parallel-out register. It controls which instructions are processed (instructions stored in ROM). The PC increments by two (since instructions are 16-bit wide) every clock pulse as long as incpc is asserted. The signal clrpc is asserted during system reset in which case the counter goes back to zero. The program counter value can also come from parallel data (during branching), if either signal JMP_signal is asserted (unconditional jmp), or if signal zero an JZ/JNZ is asserted (jump if/not zero). The data comes in from the IBUS. B. Memory Address Register (MAR)

CONTROL UNIT

RAMOUT ACCOUT IROUT2

IBUS

JMP Zero JZ JNZ LDM Enable Rd Enable PC Value ADDR

ALUOUT A B C D

This is a simple parallel-in, parallel-out register that is meant to hold the value of the Program counter. It changes value only when signal LDM is asserted. The purpose of this is to hold the PC data so that other steps/cycles can use it. Source

register

Program counter (+2)

PCOUT

MAR

ROM

Program Memory

ADDR + 1

IR1 IR2

IROUT2

C.

select srcSel (3 bit)

ROM

incpc clrpc RAM (read enable) LDA su select ACCOUT ALUOUT Wr (write enable)

RAM Address

IBUS

RAM 1 x 32 bytes

data in

RAMOUT

IBUS

8-bit

ALU

enable_a OUTA A

PORTA

enable_b OUTB 8-bit Bi-directional ports

B

B

PORTB

enable_c OUTC

LDB

C D Fig.1: Overall block diagram

PORTC

enable_d

PORTD

OUTD

This is a 1 x 32 memory block which is fed by the MAR. The instructions are stored here (max of 256 instructions) and controlled by the PC (which is the value MAR holds). Since instructions are 16-bit wide, ROM outputs two 8-bit data. Instructions always start on EVEN addresses. The upper 8 bits are the instruction opcode, which the lower 8 bits are allocated for memory addresses or immediate data. ROM changes value if signal rd is asserted.

Page 1 of 8

D.

Instruction register (IR)

AD D SUB

Add A and B, save in A Subtract A and B, save in A Logical AND Logical OR Invert A Increment A Decrement A Unconditional jump Jump if A is zero Jump if A is not zero Stop operation

This is similar in purpose to MAR, since it holds the ROM output for use in other steps. It outputs two 8-bit values (for opcode and instruction data). The upper 8 bits are fed to the control unit, while the lower 8 bits go to the RAM and the destination register. E. RAM

AND OR NOT INC A DEC A JMP JZ

The RAM can hold 256 bytes of data. Address is controlled mainly by the lower 8 bits of each instruction. The output is fed to the destination register. Data can also be saved if signal wr is asserted, and data is fed through IBUS. F. A and B

JNZ HLT

Registers A and B simply hold a single byte. A is frequently used as an accumulator. Both are fed through the IBUS. Data from the PORTS are also saved to A. G. PORTS

IBUS input enable_a A (output to dest register )

Fig. 2: PORTA

Table 1 gives a short description of the instruction set (Table 4 gives the opcode and operations involved). These instructions were chosen to illustrate basic capabilities of a processor.

I.

Control Unit (Source register)

LDM LDA

Source register

LDB enable_a enable_b enable_c enable_d

select destSel (3 3: Source register Fig. bit)

Figure 2 illustrates a simple implementation of PORTA. Direction is controlled by tri-state buffers. If enable_a is asserted, data is outputted thru the PORT. Otherwise, the PORT is an input port which is fed to A (then going to the source register). H. Instruction set

Table 1: Instruction set LDA LDA i LDA p SVA OUT Load data in A Load immediate value to A Load value from PORT to A Save A into memory Output A into PORT

The source register selects the enable of each component. destSel comes from another component of the control unit.

Page 2 of 8

J.

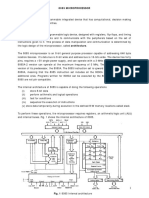

Control Unit (Instruction decode)

LOADA LDAi LDAp SVA OUT ADD IROUT1 SUB AND OR NOT INCA DECA JMP JZ JNZ HLT

EXPERIMENT DESIGN

Instruction Decode

The processor was implemented in Xilinx ISE 12.4, and testing was done on the simulator ISIM. All the instructions are hardcoded in the ROM. The flow of instructions tests all the instructions, with a final jump back to the start. Table 2 shows the contents of the ROM. There are a total of 44 instructions hardcoded.

Fig. 3: Instruction Decode

This block gets the upper 8 bits of the instructions (IR1), and determines the kind of instructions. The corresponding signal is then asserted, and will be used to determine the control signals. K. Control Unit (FSM)

clk

LOADA LDAi LDAp SVA OUT ADD SUB AND OR NOT INCA DECA JMP JZ JNZ HLT

RAM Jmp_signal clrpc incpc

State machine (18 states, T0 to T18)

destSel srcSel rd wr su

Fig. 4: FSM

Table 2: Hardcoded instructions ROM location Instruct ion LDA LDAi SVA LDA LDA OUT OUT 1 6 1 5 3 0 1

Expected A should be 7 A should be 6 Mem 01 should be 6 A should be h30 A should be 6 PORTA should be 6 PORTB should be 6

The state machine controls the destination register and source registers, as well as the memory reads and writes. There are a total of 19 states, the full detail of which is included in table 4. The control signals are listed in table 4, with their hex value, and designed into a mealy machine. The control signals were obtained via analysis of the microoperations.

0 2 4 6 8 10 12

Page 3 of 8

14 16 18 20 22 24 26 28 30 32 34 36 38 40 42 44

OUT OUT ADD SUB AND OR NOT INC A DEC A LDA JZ LDA JZ LDA LDA JMP

3 2 9 9 9 9 x x x E 0 F 2 C 8 8 0

PORTD should be 6 PORTC should be 6 A should be 6 + 8 = Eh A=E-8 A = 0110 AND 1000 A = 0000 OR 1000 A = F7h A= F8h A=F7h A=1h NOT JUMP A=0h JUMP to 41 A=0 A=1 Back to start

DATA AND RESULTS

The system was found to be accurate after running ISIM. Below is a sample of screenshots to verify that the system is indeed working:

Page 4 of 8

Fig. 5: Load Waveform

Figure 5 demonstrates that (1) The PC is indeed counting by 2; (2) that the control signals (test3 in waveform) change per step; (3) that for the first instruction (LDA), A indeed changed to 07hex; (4) that the PORTs are high impedance for any instruction except for OUT.

on the Xilinx platform. The ISIM simulator does not accept an input.

Fig. 7: Load Waveform

Lastly, figure 7 shows that a jump instruction (IR1 = 0C, IR2 = 00 means jump to 0), does indeed change the program counter to zero. .

[1]

REFERENCES

Chu, P. (2008). FPGA Prototyping by Verilog Examples. Wiley-Interscience.

Fig. 6: Out Waveform

Figure 6 shows that for IR1 = 04 (OUT instruction), and selecting PORTC, since IR2 = 10, the value of A is indeed displayed on PORTC. Take note that the design assumes a device is on hand to detect and save the data. The author could not make a way to simulate an input (LDAp) for the PORTS

APPENDIX

CONTROL UNIT

RAMOUT ACCOUT IROUT2

IBUS

JMP Zero JZ JNZ LDM Enable Rd Enable PC Value ADDR

ALUOUT A B C D

Source registe

Program counter (+2)

PCOUT

MAR

ROM

Program Memory

ADDR + 1

IR1 IR2

IROUT2

select srcSel (3 bit)

incpc clrpc RAM (read enable) LDA su select ACCOUT ALUOUT Wr (write enable )

RAM Address

IBUS

RAM 1 x 32 bytes

data in

RAMOUT

IBU

8-b

ALU

enable_a OUTA A

PORTA

enable_b OUTB 8-bit Bi-directional ports OUTC

B

B

PORTB

enable_c

LDB

PORTC

enable_d

Fig. 9: Block Diagram of Extended SAP

D

PORTD

OUTD

ble 4: Hardcoded instructions

LD B

RA M

JM P

clrp c

incp c

destSel

srcS el

r d

w r

su 00 0 00 0 00 0 1 0 0 0 0 F

Hex 0 0 0 0 3 0

MicroOperati ons RESET PC 0 ALL MAR PC IR M[MAR] PC PC + 2

Stat e

000

T15

0 0

0 0

0 0

0 0

0 1

0 1

0 1

0 1

000 001

0 1

0 0

T0 T1

LDA 0 LD B RA M 1 0 JM P 0 clrp c 0 incp c 0 1 0 000 srcS el 1 r d 0 w r 00 0 4 2 1 0 A RAM[IR2] go to fetch MicroOperati ons LDAi A IR2 go to fetch LDAp A PORTNUM T2 Stat e

destSel

su 00 0 0 2

Hex 5 0

010

T3

0 0 0 0

0 0 0 0

0 0 0 0

0 0 0 0

0 0 0 0

0 0 0 0

1 1 1 1

0 0 0 0

100 101 110 111

1 1 1 1

0 0 0 0

00 0 00 0 00 0 00 0 00 0

0 2 0 2 0 2 0 2 0 7

9 0 B 0 D 0 F 0 2 8

T4

SVA 0 0 0 0 0 1 1 1 001 0 1 M<-A go to fetch OUT PORTA <- A PORTB <- A PORTC <- A PORTD <- A go to fetch ADD B <RAM[IR2] A <- A + B go to fetch SUB B <RAM[IR2] A <- A + B go to fetch AND B <RAM[IR2] A <- A & B go to fetch OR B <RAM[IR2] A <- A or B go to fetch NOT A <- ~A go to fetch T5 T6

0 0 0 0

0 0 0 0

0 0 0 0

0 0 0 0

0 0 0 0

0 1 1 1

1 0 0 1

1 0 1 0

001 001 001 001

0 0 0 0

0 0 0 0

00 0 00 0 00 0 00 0

0 3 0 4 0 5 0 6

2 0 2 0 2 0 2 0

1 0

1 0

0 0

0 0

0 0

1 0

1 1

1 0

000 011

1 0

0 0

00 0 00 0

C 7 0 2

1 0 6 0

T7 T8

1 0

1 0

0 0

0 0

0 0

1 0

1 1

1 0

000 011

1 0

0 0

00 0 00 1

C 7 0 2

1 0 6 1

T7 T9

1 0

1 0

0 0

0 0

0 0

1 0

1 1

1 0

000 011

1 0

0 0

00 0 01 0

C 7 0 2

1 0 6 2

T7 T10

1 0

1 0

0 0

0 0

0 0

1 0

1 1

1 0

000 011

1 0

0 0

00 0 01 1

C 7 0 2

1 0 6 3

T7 T11

011

10 0

0 2

6 4

T12

INCA 0 0 0 0 0 0 1 0 011 0 0 10 1 0 2 6 5 A <- A + 1 go to fetch DECA A <- A - 1 go to fetch JMP PC <- IR2 go to fetch JZ / JNZ PC<-IR2 if A is 0 go to fetch T13

011

11 0

0 2

6 6

T14

010

00 0

2 7

4 0

T15

010

11 1

0 7

4 7

T16

Das könnte Ihnen auch gefallen

- Digital Logic And Computer OrganizationDokument18 SeitenDigital Logic And Computer OrganizationJit AggNoch keine Bewertungen

- Sap 1Dokument54 SeitenSap 1ICANSAP0% (3)

- Evolution of Simple-As-Possible ComputersDokument13 SeitenEvolution of Simple-As-Possible ComputersMd Raton AliNoch keine Bewertungen

- SAP-1 (Simple As Possible-1) Computer ArchitectureDokument8 SeitenSAP-1 (Simple As Possible-1) Computer ArchitecturesaikotNoch keine Bewertungen

- Basic SAP-1 Computer Architecture ExplainedDokument9 SeitenBasic SAP-1 Computer Architecture ExplainedAshna100% (1)

- Micro Controller Lab ManualDokument36 SeitenMicro Controller Lab ManualKefiraNoch keine Bewertungen

- Basic Concepts of MicroprocessorsDokument32 SeitenBasic Concepts of MicroprocessorsAakrati SharmaNoch keine Bewertungen

- Unit I PDFDokument25 SeitenUnit I PDFSomnath2014Noch keine Bewertungen

- PLMU Computer Studies Dept SAP-1 modificationDokument17 SeitenPLMU Computer Studies Dept SAP-1 modificationJaysen GeronimoNoch keine Bewertungen

- Part 1Dokument30 SeitenPart 1ady63100% (1)

- Micro ControllersDokument32 SeitenMicro ControllersBhuvnesh SinghNoch keine Bewertungen

- Hardwired ControlDokument6 SeitenHardwired Controlapi-19967001Noch keine Bewertungen

- Unit1 Addressing Modes and GPRDokument70 SeitenUnit1 Addressing Modes and GPRsaumya2213215Noch keine Bewertungen

- Microprocessor and Micro ControllerDokument118 SeitenMicroprocessor and Micro ControllerShiva ShanNoch keine Bewertungen

- Week 04Dokument68 SeitenWeek 04aroosa naheedNoch keine Bewertungen

- Understanding LCDDokument7 SeitenUnderstanding LCDOscar LyeNoch keine Bewertungen

- Introduction to Intel 8085 MicroprocessorDokument35 SeitenIntroduction to Intel 8085 MicroprocessorVasudev Rao KonjetiNoch keine Bewertungen

- Addressing Modes & Instruction SetDokument39 SeitenAddressing Modes & Instruction SetlekaNoch keine Bewertungen

- Sap 1Dokument54 SeitenSap 1Israr Ahmad Dawar100% (3)

- Tkbase + 2148 D-Board: Lpc2148 Training ManualDokument47 SeitenTkbase + 2148 D-Board: Lpc2148 Training ManualMahesh BhatkalNoch keine Bewertungen

- PIC - New - Part 1 PIC Microcontroller Systems PDFDokument5 SeitenPIC - New - Part 1 PIC Microcontroller Systems PDFLam Nguyen100% (1)

- MPMC NotesDokument301 SeitenMPMC NotesVarinder KumarNoch keine Bewertungen

- ESD Lab RevisedDokument22 SeitenESD Lab RevisedravindarsinghNoch keine Bewertungen

- Micro Controller Lab ManualDokument38 SeitenMicro Controller Lab ManualSameer Sadiq100% (1)

- Cs2 Practical PDFDokument62 SeitenCs2 Practical PDFMaitri ShahNoch keine Bewertungen

- Micro Controller Lab Manual 1Dokument38 SeitenMicro Controller Lab Manual 1Suresh KumarNoch keine Bewertungen

- ECE 552 Introduction to Computer Architecture Design Project ReportDokument10 SeitenECE 552 Introduction to Computer Architecture Design Project ReportzzzzoobbiiaaNoch keine Bewertungen

- PD 6124 ADokument36 SeitenPD 6124 AmarinlosterNoch keine Bewertungen

- 8085 Microprocessor Kit DescriptionDokument51 Seiten8085 Microprocessor Kit DescriptionPrince Blissful100% (1)

- 8085 Features, Signal DescriptionDokument13 Seiten8085 Features, Signal DescriptionRakesh Kumar DNoch keine Bewertungen

- MICROPORCESSOR 8085 Lab ManualDokument53 SeitenMICROPORCESSOR 8085 Lab ManualAjay PatilNoch keine Bewertungen

- 8085 Processor Unit I: Mr. S. VinodDokument52 Seiten8085 Processor Unit I: Mr. S. VinodVinod SrinivasanNoch keine Bewertungen

- Lecture 3Dokument88 SeitenLecture 3Hemanth KumarNoch keine Bewertungen

- Question Bank For MPDokument38 SeitenQuestion Bank For MPmekalajesiNoch keine Bewertungen

- Training ReportDokument18 SeitenTraining Reportpiyushji125Noch keine Bewertungen

- Blockdiagramof 8085Dokument40 SeitenBlockdiagramof 8085Akhil NameirakpamNoch keine Bewertungen

- Mpa Question Bank1Dokument16 SeitenMpa Question Bank1Sharon FrancisNoch keine Bewertungen

- Microprocessor Lab Manual EE0310Dokument44 SeitenMicroprocessor Lab Manual EE0310sathishkumar.vNoch keine Bewertungen

- IN and OUT instructions in the 8086 microprocessor: input and output operationsDokument10 SeitenIN and OUT instructions in the 8086 microprocessor: input and output operationsdtselvanNoch keine Bewertungen

- ES Lab FileDokument37 SeitenES Lab FileMøhït JáñgírNoch keine Bewertungen

- 8085 MaterialDokument12 Seiten8085 MaterialsameerNoch keine Bewertungen

- Mimari ReportDokument27 SeitenMimari ReportRomaan AliNoch keine Bewertungen

- Fundamental Concepts of BPUDokument16 SeitenFundamental Concepts of BPURam GaneshNoch keine Bewertungen

- 8085 Architecture: Control UnitDokument10 Seiten8085 Architecture: Control UnitsweetmemoriesneverdiNoch keine Bewertungen

- Unit 2 FinalDokument31 SeitenUnit 2 Finalswetha bagadi it's good but how it will workNoch keine Bewertungen

- 8086 ProgramingDokument9 Seiten8086 ProgramingAneel Kumar BhatiaNoch keine Bewertungen

- Sap 1 2Dokument21 SeitenSap 1 2Brandon Maciel50% (2)

- Electronics Project Automatic Bike Controller Using Infrared RaysDokument16 SeitenElectronics Project Automatic Bike Controller Using Infrared RaysragajeevaNoch keine Bewertungen

- Laboratory Manual Microprocessor 8085: SL - No. Name of The Experiments NoDokument25 SeitenLaboratory Manual Microprocessor 8085: SL - No. Name of The Experiments NobhaswatiNoch keine Bewertungen

- 8051 Architecture FullDokument39 Seiten8051 Architecture FullRaja RajNoch keine Bewertungen

- Unit II Basic Processing TopicsDokument47 SeitenUnit II Basic Processing TopicsKaruppanan KomathyNoch keine Bewertungen

- 8085 - Short SummaryDokument14 Seiten8085 - Short SummaryTarunVarmaNoch keine Bewertungen

- Coa Lecture Unit 2Dokument82 SeitenCoa Lecture Unit 2Sumathy JayaramNoch keine Bewertungen

- Instruction CodesDokument35 SeitenInstruction Codesanilk_patiNoch keine Bewertungen

- Sap 2Dokument35 SeitenSap 2Michael Vincent B. Nierva88% (8)

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Von EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Noch keine Bewertungen

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationVon EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNoch keine Bewertungen

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Von EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Noch keine Bewertungen

- Projects With Microcontrollers And PICCVon EverandProjects With Microcontrollers And PICCBewertung: 5 von 5 Sternen5/5 (1)

- Distance Sensors Catalog-8014441Dokument404 SeitenDistance Sensors Catalog-8014441etorinNoch keine Bewertungen

- How To Design The Perfect PCBDokument33 SeitenHow To Design The Perfect PCBDiego Ricardo Paez ArdilaNoch keine Bewertungen

- Dell Emc Poweredge R640: Installation and Service ManualDokument173 SeitenDell Emc Poweredge R640: Installation and Service ManualangevilessNoch keine Bewertungen

- Data Domain, Deduplication and MoreDokument6 SeitenData Domain, Deduplication and MorebinhNoch keine Bewertungen

- Reducing Miss PenaltyDokument34 SeitenReducing Miss Penaltyi_2loveu32350% (1)

- BHCnav Brochure v4 PDFDokument7 SeitenBHCnav Brochure v4 PDFYanier Forero OrtizNoch keine Bewertungen

- Technical Support International: Module 8: Software UpdateDokument10 SeitenTechnical Support International: Module 8: Software UpdateBrayan RamírezNoch keine Bewertungen

- PMP 450x Release Notes - 20.0.1Dokument33 SeitenPMP 450x Release Notes - 20.0.1jaraqu01Noch keine Bewertungen

- PowerPoint TemplateDokument20 SeitenPowerPoint Templatehuynhducquoc0122100% (3)

- Sample Nda AgreementDokument4 SeitenSample Nda Agreementbirdone3Noch keine Bewertungen

- Get admission in computer courses and earn a degree after examsDokument2 SeitenGet admission in computer courses and earn a degree after examsShahbaz HassanNoch keine Bewertungen

- Design and Implementation of Convolutional Neural Network Accelerator Based On RISCVDokument6 SeitenDesign and Implementation of Convolutional Neural Network Accelerator Based On RISCVmadupiz@gmailNoch keine Bewertungen

- Git Cheat SheetDokument1 SeiteGit Cheat Sheetkzelda100% (1)

- How To Become An Online Entrepreneur Ebook V2Dokument7 SeitenHow To Become An Online Entrepreneur Ebook V2Nick BlackNoch keine Bewertungen

- IFP-2100/ECS RFP-2100: Installation and Operation GuideDokument264 SeitenIFP-2100/ECS RFP-2100: Installation and Operation GuideMurali DaranNoch keine Bewertungen

- Project RAM Detail: Responsibility Assignment Matrix (RAM)Dokument6 SeitenProject RAM Detail: Responsibility Assignment Matrix (RAM)farhanyazdani100% (1)

- Java MCQ-5Dokument4 SeitenJava MCQ-5Sri SriNoch keine Bewertungen

- Major 7th Chords: Extracted From "The Complete Book of Improvisation" by Fred LipsiusDokument182 SeitenMajor 7th Chords: Extracted From "The Complete Book of Improvisation" by Fred LipsiusJuan Carlos Fiallos Rodas100% (1)

- Need of Cloud in DevOpsDokument17 SeitenNeed of Cloud in DevOpsSuneetha BullaNoch keine Bewertungen

- A Novel Adoption of LSTM in Customer Touchpoint Prediction Problems Presentation 1Dokument73 SeitenA Novel Adoption of LSTM in Customer Touchpoint Prediction Problems Presentation 1Os MNoch keine Bewertungen

- Basic Overview of Ms Dos CommandsDokument6 SeitenBasic Overview of Ms Dos CommandsAjay ChandranNoch keine Bewertungen

- Structural design and software for G+4 mixed-use buildingDokument343 SeitenStructural design and software for G+4 mixed-use buildingyimamNoch keine Bewertungen

- 10 Hybris Spring AOPDokument4 Seiten10 Hybris Spring AOPravikanchuNoch keine Bewertungen

- Online ClassDokument5 SeitenOnline ClassLokendra RathoreNoch keine Bewertungen

- Puter Vision With TensorFlow 2 X 1838827064Dokument419 SeitenPuter Vision With TensorFlow 2 X 1838827064超揚林100% (2)

- Company Profile-Human Resource ServicesDokument16 SeitenCompany Profile-Human Resource Servicessyed pashaNoch keine Bewertungen

- Samsung XE700 5 - BA41-01714A 01715A 01716ADokument1 SeiteSamsung XE700 5 - BA41-01714A 01715A 01716AJaelaniNoch keine Bewertungen

- E17040 ZenWiFi AX XT8 UM PDFDokument151 SeitenE17040 ZenWiFi AX XT8 UM PDFEP TANNoch keine Bewertungen

- JESS Functions and I/O TutorialDokument5 SeitenJESS Functions and I/O TutorialolivukovicNoch keine Bewertungen

- Microsoft Word (Microsoft 365 Apps and Office 2019) : Exam MO-100Dokument2 SeitenMicrosoft Word (Microsoft 365 Apps and Office 2019) : Exam MO-100Saber RaddaouiNoch keine Bewertungen