Beruflich Dokumente

Kultur Dokumente

Reporte Histéresis

Hochgeladen von

Alan Cruz RojasOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Reporte Histéresis

Hochgeladen von

Alan Cruz RojasCopyright:

Verfügbare Formate

Anlisis y Control de Sistemas No Lineales

Histresis

y L+

S-

S+

L-

Dr. Carlos Manuel Astorga Zaragoza

Alan Cruz Rojas Antonio Coronel Escamilla

Cuernavaca, Morelos, sbado, 14 de abril de 2012

Introduccin Frecuentemente encontramos elementos no lineales cuya caracterstica entradasalida tienen memoria; esto es, la salida en cualquier instante de tiempo puede depender de la historia completa de la entrada. La figura 1.1 muestra la caracterstica del tipo histresis. Esta grfica corresponde a un relevador con histresis. y L+

S-

S+

LFigura 1.1 Relevador con histresis (Izquierda: Grfica ideal, Derecha: Grfica real).

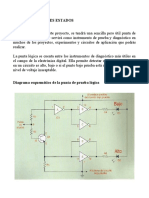

Para valores altamente negativos en la entrada, la salida estar en el nivel ms bajo . Conforme la entrada valla aumentando, la salida permanece en hasta que la entrada alcance . Incrementando la entrada hasta , la salida cambia al nivel ms alto y permanece ah para valores altos de la entrada. Ahora, si decrementamos la entrada, la salida permanece en el nivel alto hasta que la entrada cruce el valor , punto en el cual, la salida cambia al nivel ms bajo y permanece ah para valores bajos de la entrada. Desarrollo Tal caracterstica entrada-salida puede ser generada, por ejemplo, por el circuito amplificador operacional de la figura 1.2. El circuito caracteriza amplificadores operacionales ideales y diodos ideales. Un amplificador operacional ideal tiene el voltaje en su entrada inversora (-) igual a su entrada no inversora (+) y tiene corrientes de entrada cero en ambas terminales. Un diodo ideal tiene la caracterstica mostrada en la figura 1.3. Cuando la entrada de voltaje es altamente negativa, los diodos D1 y D3 estarn activados mientras que D2 y D4 desactivados. Debido a que las entradas inversoras de ambos amplificadores operacionales estn en tierra virtual, las corrientes R5 y D3 sern cero y la salida de D3 estar en tierra virtual. Por eso, la salida de voltaje

estar dada por . Esta situacin permanecer tanto tiempo como la corriente en D1 sea positiva. Esto es,

Figura 1.2 Circuito amplificador operacional que presenta un relevador con la histresis de la figura 1.1.

i on off v

Figura 1.3 Caracterstica

de un diodo ideal.

Segn incrementemos la entrada , la salida y permanecer en hasta que la entrada alcance el valor . Ms all de este valor, los diodos D1 y D3 estarn desactivados mientras D2 y D4 encendidos. Una vez ms, debido a que las entradas inversoras de ambos amplificadores operacionales estn en tierra virtual, las corrientes R5 y D4 sern cero, y la entrada de D4 estar en tierra virtual. Por eso, la salida estar dada por . Esta situacin permanecer tanto tiempo como la corriente en D2 sea positiva, esto es,

Por lo tanto obtenemos la caracterstica entrada-salida de la figura 1.1 con:

Implementacin fsica Los valores propuestos para estas ecuaciones son los siguientes: R1 = 15 K R2 = 2.2 K R3 = 2.2 K R4 = 15 K R5 = 1 K R6 = 15 K R7 = 15 K E = 12 volts Con estos valores se obtienen los siguientes voltajes tanto en la entrada como en la salida:

El circuito armado qued de la siguiente manera:

Figura 1.4 Fotografas de la implementacin del circuito de un amplificador operacional con histresis.

Das könnte Ihnen auch gefallen

- Pre Laboratorio IIIDokument14 SeitenPre Laboratorio IIIGuillermo garciaNoch keine Bewertungen

- Sonda Logica Detector de Niveles CMOS TTLDokument3 SeitenSonda Logica Detector de Niveles CMOS TTLCharles BabbageNoch keine Bewertungen

- Informe de Amplificadores Operacionales Américo MonzonDokument19 SeitenInforme de Amplificadores Operacionales Américo Monzonamericomonzon476Noch keine Bewertungen

- Labo1 - Informe PrevioDokument16 SeitenLabo1 - Informe PreviodaniNoch keine Bewertungen

- Circuitos SecuencialesDokument21 SeitenCircuitos SecuencialesFrancisco Rodriguez CozarNoch keine Bewertungen

- Mod 5.3 Conversión de DatosDokument49 SeitenMod 5.3 Conversión de Datosalejandro reguilon escalonaNoch keine Bewertungen

- El Amplificador Operacional IdealDokument8 SeitenEl Amplificador Operacional IdealkristelNoch keine Bewertungen

- Familias LogicasDokument6 SeitenFamilias LogicasIvan TellezNoch keine Bewertungen

- TAREA 3-Edgar Perdomo PorrasDokument13 SeitenTAREA 3-Edgar Perdomo PorrasedgarNoch keine Bewertungen

- Rectificador MonofasicoDokument5 SeitenRectificador MonofasicoJean Alexander YRNoch keine Bewertungen

- Puntalogica 12vDokument12 SeitenPuntalogica 12vAlexander RicoNoch keine Bewertungen

- Unidad 2 - Jonathan Alexander Santana Perez - 2009-0639Dokument11 SeitenUnidad 2 - Jonathan Alexander Santana Perez - 2009-0639cpyin88Noch keine Bewertungen

- Circuitos Combinatorios Con VHDLDokument21 SeitenCircuitos Combinatorios Con VHDLCharbel Leal KuriNoch keine Bewertungen

- Practica #1 Alarma de BancoDokument3 SeitenPractica #1 Alarma de BancoDaniel GonzalezNoch keine Bewertungen

- Punta Lógica TTL de Tres EstadosDokument8 SeitenPunta Lógica TTL de Tres EstadosMiguel Lop100% (1)

- Tema 8Dokument19 SeitenTema 8ELEC CAMASNoch keine Bewertungen

- Flip Flops Und2Dokument9 SeitenFlip Flops Und2cpyin88Noch keine Bewertungen

- Divisor de FrecuenciaDokument7 SeitenDivisor de Frecuenciajorge_0508Noch keine Bewertungen

- ClaseIIB 14 Conversion DACDokument7 SeitenClaseIIB 14 Conversion DACVinicio Quilumba100% (1)

- Practica 2Dokument13 SeitenPractica 2Luis Gerardo Alba ArgüelloNoch keine Bewertungen

- Funcionalidad de Las DTLDokument7 SeitenFuncionalidad de Las DTLMargot BautistaNoch keine Bewertungen

- Para Que Sirve Un OPAMPDokument16 SeitenPara Que Sirve Un OPAMPJacCke MeDinaNoch keine Bewertungen

- Practicanro2ixismarionny 180203015704Dokument21 SeitenPracticanro2ixismarionny 180203015704Santiago ArciniegasNoch keine Bewertungen

- Aplicacion de Las Compuertas LogicasDokument8 SeitenAplicacion de Las Compuertas LogicasKennyi L. Aro Apaza83% (6)

- Amplificador OperacionalDokument6 SeitenAmplificador OperacionalEric Dueñas TrujilloNoch keine Bewertungen

- Ope2 V3Dokument19 SeitenOpe2 V3Consuelo MarinNoch keine Bewertungen

- Compuertas LógicasDokument5 SeitenCompuertas LógicasGuadalupe SosaNoch keine Bewertungen

- Aplicaciones No Lineales Del Amplificador No Lineal.Dokument3 SeitenAplicaciones No Lineales Del Amplificador No Lineal.bryansolorzanoNoch keine Bewertungen

- Practica 5Dokument29 SeitenPractica 5María MorenoNoch keine Bewertungen

- Primer Proyecto de Electronica DigitalDokument7 SeitenPrimer Proyecto de Electronica DigitalArturo RosalesNoch keine Bewertungen

- Punta Logica Tres EstadosDokument3 SeitenPunta Logica Tres Estadosgtran100% (1)

- Amplificadores Operacionales y Su Uso en La ElectrónicaDokument18 SeitenAmplificadores Operacionales y Su Uso en La ElectrónicaEduardo Sierra PinachoNoch keine Bewertungen

- Trabajo de Compuertas LogicasDokument11 SeitenTrabajo de Compuertas LogicasElias Jose Gonzalez Jimenez100% (1)

- INVESTIGACION Amplificadores Operacionales y Su Uso en La ElectrónicaDokument12 SeitenINVESTIGACION Amplificadores Operacionales y Su Uso en La ElectrónicawmqgnhwmnsNoch keine Bewertungen

- Semiconvertidor Trifásico AC EXPOCDokument10 SeitenSemiconvertidor Trifásico AC EXPOCAlex SalasNoch keine Bewertungen

- Reporte de Laboratorio 4 EditadaDokument23 SeitenReporte de Laboratorio 4 EditadaSolis Castillo Gerardo SamuelNoch keine Bewertungen

- Proyectos ElectrónicaDokument5 SeitenProyectos ElectrónicaEliecer GonzalezNoch keine Bewertungen

- Segundo Examen Parcia1Dokument11 SeitenSegundo Examen Parcia1Julio AlarcónNoch keine Bewertungen

- Consultar Un Método Indirecto para Medir La Impedancia de Entrada de Un CircuitoDokument7 SeitenConsultar Un Método Indirecto para Medir La Impedancia de Entrada de Un CircuitoMateo Josue100% (1)

- Unidad - Nº2 - Amplificadores OperacionalesDokument27 SeitenUnidad - Nº2 - Amplificadores OperacionalesIsmael Arias InostrozaNoch keine Bewertungen

- Practica 1 Amplificador InversorDokument10 SeitenPractica 1 Amplificador InversorAxel CruzNoch keine Bewertungen

- Punta LogicaDokument5 SeitenPunta LogicaGustavo Burbano100% (1)

- Diseño de Una Punta LogicaDokument2 SeitenDiseño de Una Punta LogicaJhoel ZabalaNoch keine Bewertungen

- Practica 4Dokument11 SeitenPractica 4Cesar Mauricio DavidNoch keine Bewertungen

- Telecomunicaciones 2Dokument18 SeitenTelecomunicaciones 2Darwin Jesús Arela QuispeNoch keine Bewertungen

- CircuitosDokument95 SeitenCircuitosdjtut0100% (2)

- Trabajo Iuta Compuertas Logicas y CircuitosDokument9 SeitenTrabajo Iuta Compuertas Logicas y CircuitosDavid S Arias100% (1)

- Electronica EjerciciosDokument9 SeitenElectronica Ejerciciosandrea bustosNoch keine Bewertungen

- Practica 1Dokument5 SeitenPractica 1Ana Laura MatiasNoch keine Bewertungen

- Practica 4 - 5CV6Dokument16 SeitenPractica 4 - 5CV6Solis Castillo Gerardo SamuelNoch keine Bewertungen

- Simbologia LogicaDokument12 SeitenSimbologia LogicaCelso Jose RequenaNoch keine Bewertungen

- Derivador y Comparador Ua 741Dokument5 SeitenDerivador y Comparador Ua 741Renato HernandoNoch keine Bewertungen

- Lm741 y OpamsDokument6 SeitenLm741 y OpamsLuis Antonio SotoNoch keine Bewertungen

- Practica 9 - AnalogicaDokument8 SeitenPractica 9 - AnalogicaKamila KNoch keine Bewertungen

- Proyecto 3 (TTL)Dokument4 SeitenProyecto 3 (TTL)Rodrigo QuintanillaNoch keine Bewertungen

- 5ta Clase Electrónica DigitalDokument24 Seiten5ta Clase Electrónica DigitalChaneudys Miguel García PérezNoch keine Bewertungen

- Practica 4Dokument22 SeitenPractica 4Kike ContrerasNoch keine Bewertungen

- COMPUERTAS LÓGICAS y Ejemplos de CircuitosDokument8 SeitenCOMPUERTAS LÓGICAS y Ejemplos de CircuitosCarlos MNoch keine Bewertungen

- Veces Es Deseable Poder Disponer de Una Corriente Proporcional A Una Tensión Cualquiera DadaDokument21 SeitenVeces Es Deseable Poder Disponer de Una Corriente Proporcional A Una Tensión Cualquiera DadaRichard WccNoch keine Bewertungen

- Armónicas en Sistemas Eléctricos IndustrialesVon EverandArmónicas en Sistemas Eléctricos IndustrialesBewertung: 4.5 von 5 Sternen4.5/5 (12)

- Tecnicas Compostaje y LombriculturaDokument27 SeitenTecnicas Compostaje y LombriculturaCarolina Ivon Inostroza HuaracànNoch keine Bewertungen

- Detección de Fallas en Periféricos Internos y Externos de La PCDokument18 SeitenDetección de Fallas en Periféricos Internos y Externos de La PCMiguelon Cespedes50% (2)

- Practicas 1 Informe Final.Dokument41 SeitenPracticas 1 Informe Final.No soy Bot ytNoch keine Bewertungen

- Personalidad Del Delincuente Capitulo 1Dokument4 SeitenPersonalidad Del Delincuente Capitulo 1Adrian O. Martinez MunozNoch keine Bewertungen

- Caso Sobre El Cambio OrganizacionalDokument2 SeitenCaso Sobre El Cambio Organizacionaljuan0% (1)

- Planes y Programas Primaria 01-05-14Dokument91 SeitenPlanes y Programas Primaria 01-05-14Guiver RenanNoch keine Bewertungen

- Grupo 6Dokument5 SeitenGrupo 6Christian Rosales AndradeNoch keine Bewertungen

- Andres David Barrero Barbosa-Libertad de Conciencia y Libertad ReligiosaDokument4 SeitenAndres David Barrero Barbosa-Libertad de Conciencia y Libertad ReligiosagigiugigNoch keine Bewertungen

- Formación de La Imagen Radiológica 2021Dokument56 SeitenFormación de La Imagen Radiológica 2021Oscar Jeldes DíazNoch keine Bewertungen

- Plasson ElectroFusionDokument52 SeitenPlasson ElectroFusionJuan Carlo SarmientoNoch keine Bewertungen

- 7 Fuentes de MagnetismoDokument4 Seiten7 Fuentes de MagnetismoDisman D'smNoch keine Bewertungen

- Guia Helipuertos PDFDokument9 SeitenGuia Helipuertos PDFSeiya Neyogiri NgupiNoch keine Bewertungen

- Ada1 Fundamentos - PadmanDokument3 SeitenAda1 Fundamentos - PadmanAkari Tuz GarcíaNoch keine Bewertungen

- INANNA - Cantos e Himnos de SumeriaDokument89 SeitenINANNA - Cantos e Himnos de Sumeriaדוד יו100% (2)

- Monografia La AnorexiaDokument27 SeitenMonografia La AnorexiaAngel ManuelNoch keine Bewertungen

- Role Playing para Servicio Al ClienteDokument2 SeitenRole Playing para Servicio Al Clientejon diazNoch keine Bewertungen

- Criterios de Diseño SciDokument6 SeitenCriterios de Diseño SciJosé Oswaldo Atalaya SánchezNoch keine Bewertungen

- Santiago Cabrera InformeDokument5 SeitenSantiago Cabrera InformeCesar Portocarrero ValdiglesiasNoch keine Bewertungen

- Buenas Noches DR y Compañeros Mi Aporte Al ForoDokument2 SeitenBuenas Noches DR y Compañeros Mi Aporte Al ForoYanet Requejo Villegs100% (2)

- Como Curar La Eyaculación PrecozDokument9 SeitenComo Curar La Eyaculación PrecozAlex Hernández ToroNoch keine Bewertungen

- Modelo de Evaluación de La Familia FriedmanDokument3 SeitenModelo de Evaluación de La Familia FriedmanScribdTranslationsNoch keine Bewertungen

- Mecanismos 6 2020Dokument40 SeitenMecanismos 6 2020Ricardo SandovalNoch keine Bewertungen

- Informe de Din 8 Sanidad MilitarDokument16 SeitenInforme de Din 8 Sanidad MilitarSami Salazar100% (1)

- HIDROGENODokument24 SeitenHIDROGENOtonyNoch keine Bewertungen

- Ondas en Un HiloDokument20 SeitenOndas en Un Hiloalex66xNoch keine Bewertungen

- Plan de Relaciones ComunitariasDokument68 SeitenPlan de Relaciones ComunitariasJhon Jairo CiezaNoch keine Bewertungen

- Taller 1. Cálculo IntegralDokument5 SeitenTaller 1. Cálculo IntegralJair Antonio Hernandez RomeroNoch keine Bewertungen

- Suscripción Digital - Todas Las Noticias de Colombia en Un Lugar - EL ESPECTADORDokument2 SeitenSuscripción Digital - Todas Las Noticias de Colombia en Un Lugar - EL ESPECTADORalfonsoNoch keine Bewertungen

- Dieta Detox de Tres Días - Belleza PDFDokument14 SeitenDieta Detox de Tres Días - Belleza PDFgaby yepesNoch keine Bewertungen

- Estado Estacionario y Flujo de PotenciaDokument26 SeitenEstado Estacionario y Flujo de PotenciaBrigido HerreraNoch keine Bewertungen