Beruflich Dokumente

Kultur Dokumente

Design

Hochgeladen von

naga7389Originalbeschreibung:

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Design

Hochgeladen von

naga7389Copyright:

Verfügbare Formate

DC-link Voltage Ripple Analysis and Impedance Network Design of

Single-phase Z-source Inverter

Yifan Yu, Qianfan Zhang, Xiaofei Liu, Shumei Cui

Institute of Electromagnetic and Electronic Technology

HARBIN INSTITUTE OF TECHNOLOGY

Harbin, China

E-Mail: yu_yifan@hit.edu.cn, zhang_qianfan@hit.edu.cn

Acknowledgements

This research is funded by Project HIT.NSRIF.2009042 supported by Natural Scientific Research

Innovation in Harbin Institute of Technology and Project 2009RFLXG010 supported by Innovation

Funding for Returned Overseas Chinese Scholars in Harbin.

Keywords

Power conditioning, Photovoltaic, Z-source inverter, Impedance network design,

Abstract

One major drawback of single-phase Z-source inverter is the introduction of low-frequency DC-link

voltage ripple, which does not exist in three-phase Z-source inverter. Therefore, proper sizing of

impedance network of single-phase Z-source inverter becomes a serious issue. In this paper,

impedance network design rules of single-phase Z-source inverter are proposed in order to limit the

low-frequency DC-link voltage ripple in an acceptable range. The design rules are derived under the

assumptions that open state could be considered as part of active state and linear approximation of

inductor current and capacitor voltage is accurate enough. Finally, the feasibility of this impedance

network design rules has been validated both by computer simulations and laboratory experiments.

Introduction

Z-source inverter, first proposed in paper [1], provides a viable single stage topology to satisfy the

pressing demand of both voltage boosting and inversion (Fig. 1). Shoot-through state, which is strictly

forbidden in conventional voltage source inverter, is allowed and implemented here for voltage

boosting purpose. Z-source inverter is suitable in grid connection of alternative energy sources such as

photovoltaic array s as they usually produce low variable DC voltage.

Fig. 1: Single-phase full bridge Z-source inverter

The concept of Z-source inverter has attracted researchers attention for the last decade. Large

numbers of publications could be found regarding problems of pulse width modulation for this special

shoot-through state [2]-[4], various modeling and control methods [5][6] and possible applications [7]-

[12]. Nevertheless, limited numbers of publications could be found so far on the detailed procedure of

impedance network design. Impedance network design method of three-phase ZSI is proposed in

paper [13] in order to limit high-frequency (HF) DC-link voltage ripple. However, unlike the situation

of its three-phase counterpart, the performance of single-phase ZSI is dominated by low-frequency

(LF) DC-link voltage ripple. Design results based on limiting HF DC-link voltage ripple still suffer

greatly from LF harmonics that are hard to filter out in the inverter output. Therefore, to fill this gap,

design approach of the impedance network based on limiting the low-frequency DC-link voltage

ripple is presented in this paper.

DC side current of single-phase ZSI

Several pulse width modulation techniques are available so far for Z-source inverter, including Simple

Boost Control [1], Maximum Boost Control [2] and Constant Maximum Boost Control [3]. Simple

Boost Control, which is generally used for its easy implementation, is described in Fig. 2.

Fig. 2: Simple boost control of single-phase ZSI

DC

L

L

C C

Active-1 State (A1)

DC

L

L

C C

Shoot-through-1 State (S1)

E

s

I

l(A)

V

C(A)

I

l(S)

V

C(S)

(a) (b)

Fig. 3: (a) Active-1 State; (b) Shoot-through-1 State

Six possible operation states of ZSI are identified in [13], among which Active-1, Open-1 and Shoot-

through-1 States (named dynamic states) contribute to the power conversion process. And Open-1

state could be considered as part of Active-1 state for analytical simplicity. The other three operation

states (named static states) only occur when the capacitor voltage and inductor current fluctuate in a

wide range. The following analysis is derived based on assumptions: (1) switching frequency is high

enough compared to output frequency; (2) static states are avoided; (3) Open-1 state could be

considered as part of Active-1 state; (4) linear approximation is accurate enough; (5) effects due to

switch transitions are negligible.

Since the inverter bridge itself has no energy storage elements, the instantaneous power input must

equal the instantaneous power output,

( )

( ) ( )(1 ) ( )sin sin( )

d

d d s d

V t

V t I t d MV t t M t

Z

| = e e (1)

where V

d

(t) I

d

(t) stand for DC-link voltage and current, d

s

for shoot-through duty ratio, M for

modulation index, Z and for load impedance and power factor, for inverter output angular

frequency. Note that the effects brought by switching frequency components are neglected. The term

(1d

s

) indicates that shoot-through state is not involved in energy transfer process from DC to AC

side. Hence, DC side current drawn by the inverter bridge can be expressed as

2 2

( ) ( )

( ) cos cos(2 ) ( )

2 (1 ) 2 (1 )

d d

d d d

s s

M V t M V t

I t t I i t

Z d Z d

| | = e = +

(2)

where I

d

(bar) and i

d

(t) denote the average and oscillating value of DC side current, respectively.

Equation (2) indicates that in addition to DC component, the current also contains sinusoidal

component at twice the output frequency. DC side current of three-phase ZSI contains DC component

only, which solely results in HF DC-link voltage ripple [13]. The situation of single-phase ZSI,

nevertheless, is more complicated: (1) DC component yields similar result to three-phase case; (2)

sinusoidal component leads to sinusoidal oscillation of DC-link voltage, also at twice the output

frequency. Therefore, both high and low frequency ripples need to be taken into consideration while

sizing the impedance network.

High-frequency ripple analysis of single-phase ZSI

HF ripple analysis of single-phase ZSI should to be performed first in order to provide the operating

point needed in LF ripple analysis later. HF ripple analysis of single-phase ZSI is essentially of the

same pattern as that of three-phase ZSI presented in paper [13]. Effects related to LF ripples could be

temporarily neglected without much error since the allowed LF ripple factors are usually small.

During Shoot-through-1 (S-1) state, the diode gets reverse biased and energy is transferred from

capacitors to inductors through these shoot-through switches (Fig. 3(a)). If we assume that capacitor

voltage and inductor current vary linearly with time instead of sinusoidal waveforms, peak ripple

value of capacitor voltage V

c(s)

and peak ripple value of inductor current I

l(s)

during S-1 state could

be expressed by

( ) ( )

( ) ( )

0.5 0.5

2 2

l s s s c s s s

c s l s

V d T

I

L

I d T

V

C

A = A = (3)

where T

s

stands for carrier time period, L and C for inductance and capacitance of impedance network,

E

s

for DC source voltage, V

c(s)

(bar) and I

l(s)

(bar) for average value of capacitor voltage and inductor

current during S-1 state. During Active-1 (A-1) state, the diode gets forward biased and energy is

transferred from DC source and inductors to load and capacitors (Fig. 3(b)). Peak ripple value of

capacitor voltage V

c(A)

and peak ripple value of inductor current I

l(A)

during A-1 state could be

expressed by

( )

( ) ( )

( )

( ) ( )

1 0.5

( )(1 )0.5

2 2

l A d s s

c A s s s

c A l A

I I d T

V E d T

V I

C L

A = A = (4)

where V

c(A)

(bar) and I

l(A)

(bar) stand for average value of capacitor voltage and inductor current during

A-1 state. Fig.4 shows the waveforms of capacitor voltage and inductor current analyzed above.

( ) c s V A

c V

( ) c s V

( ) c A V A

( ) c A V

0.5 s T 0.5 s s d T

t

0.5 s s d T 0.5 s T

t

( ) l s I

S-1 A-1 S-1 A-1

( ) l s I A

( ) l A I

( ) l A I A

l I

c V l I

t t

High-frequency view

Low-frequency view

Capacitor voltage

Inductor current

Fig. 4: Waveforms of capacitor voltage and inductor current for HF ripple analysis

For steady-state operation, initial values of all variables equal their final values for every carrier cycle,

( ) ( ) ( ) ( ) c A c s c c A c s c V V V V V V = = A = A = A ( ) ( ) ( ) ( ) l A l s l l A l s l I I I I I I = = A = A = A

(5)

By combining (2)-(5), average value of capacitor voltage and inductor current could be expressed as

1 1

1 2 1 2

s s

c s l d

s s

d d

V E I I

d d

= =

(6)

HF ripple factor of capacitor voltage and inductor current can be expressed as

2

( )

cos

8 (1 )(1 2 )

c s s

vc H

s s c

V M d T

k

C Z d d V

| A

= =

( )

2

(1 )(1 2 )

2 cos

s s s s

l

il H

l

d d d T Z

I

k

LM I |

A

= = (7)

To validate assumption (1), k

vc(H)

k

vc(H)1

and k

il

k

il(H)1

, thus

2

( )1

cos

8 (1 )(1 2 )

s s

c H s s

M d T

C

kv Z d d

|

>

2

( )1

(1 )(1 2 )

2 cos

s s s s

il H

d d d T Z

L

k M |

> (8)

During Active-1 State, 2 d c s V V E = (refer to Fig. 3(a)). Therefore, HF ripple factor of DC-link voltage

2

( )

cos

4 (1 2 )

d s s

v H

s d

V M d T

k

C Z d V

| A

= =

(9)

Low-frequency ripple analysis of single-phase ZSI

As mentioned above, LF ripples of single-phase ZSI originate in the oscillating component of DC side

current. Therefore, the major objective of LF-ripple analysis is to calculate the corresponding LF

oscillating component of capacitor voltage, inductor current and DC-link voltage caused by i

d

(t),

respectively. Base on the operating point given in HF ripple analysis, capacitor voltage, inductor

current and DC-link voltage can be expressed by

( ) ( ) c c c V t V v t = + ( ) ( ) l l l I t I i t = + ( ) ( ) d d d V t V v t = + (10)

where v

c

(t) i

l

(t) v

d

(t) are corresponding LF oscillations. Hence, based on Equation (2) DC side current

could be modified as

2 2 2

( )

( ) cos cos(2 ) cos ( )

2 (1 ) 2 (1 ) 2 (1 )

d d d

d d d

s s s

M V M V M v t

I t t I i t

Z d Z d Z d

| | | ~ e + = +

(11)

( ) c s V A

c V

( ) c s V

( ) c A V A

( ) c A V

0.5 s T 0.5 s s d T

t

0.5 s s d T 0.5 s T

t

( ) l s I

( ) l s I A

( ) l A I

( ) l A I A

l I

c V

l I

t

1 c V A

1 l I A

l I

c V

( ) c c V v t +

( ) l l I i t +

0.25T 0.25T

t

Fig. 5: Waveforms of capacitor voltage and inductor current for LF ripple analysis

During S-1 and A-1 state,

( )

( )

( ) 0.5

2 ( )

l s s s

c s

I t d T

V t

C

A =

( )

( )

( ) 0.5

2 ( )

c s s s

l s

V t d T

I t

L

A = (12)

( )

( ) ( )

( )

( ) ( ) 1 0.5

2 ( )

l A d d s s

c A

I t I i t d T

V t

C

A =

( )

( )

( ( ) )(1 )0.5

2 ( )

c A s s s

l A

V t E d T

I t

L

A = (13)

Therefore, capacitor voltage and inductance voltage variation for one carrier period

1 ( ) ( ) 1 ( ) ( ) ( ) 2 ( ) 2 ( ) ( ) 2 ( ) 2 ( ) c c A c s l l A l s V t V t V t I t I t I t A = A A A = A A (14)

Assuming ( ) ( ) ( ) ( ) ( ) c A c s c V t V t V t = = and ( ) ( ) ( ) ( ) ( ) l A l s l I t I t I t = = yields

1

0

( ) ( )(1 2 ) ( )(1 ) ( ) ( )(1 2 ) ( )(1 )

0.5

s

c l s d s c l s d s

T

s

V t i t d i t d dv t i t d i t d

T C dt C

A

= = (15)

1

0

( ) ( )(1 2 ) ( ) ( )(1 2 )

0.5

s

l c s l c s

T

s

I t v t d di t v t d

T L dt L

A

= = (16)

Solving Equations (15) (16) yields

2

2

2 4 2 2 2 2 2

2

2

2 4 2 2 2 2 2

2 2 2 2

1

2 2 2

( ) sin(2 )

4 cos (4 (1 2 ) )

(1 2 )

( ) cos(2 )

2 4 cos (4 (1 2 ) )

(1 2 ) sin 4 sin 2 cos

tan ( )

(1 2 ) cos 4 cos 2 sin cos

d

c

s

s d

l

s

s

s

M LV

v t t

M L Z LC d

M d V

i t t

M L Z LC d

d Z LC Z M L

d Z LC Z M L

u

|

u

|

| | |

u

| | | |

e

= e +

e + e

= e +

e + e

e + e

=

+ e + e

(17)

LF ripple factors of capacitor voltage and inductor current

2

( )

2

2 4 2 2 2 2 2

2

( )

2

2 4 2 2 2 2 2

(1 ) 4 cos (4 (1 2 ) )

(1 2 )

cos 4 cos (4 (1 2 ) )

vc L

s s

s

il L

s

M L

k

d M L Z LC d

d Z

k

M L Z LC d

|

| |

e

=

e + e

=

e + e

(18)

Finally, LF DC-link voltage ripple factor

2

( )

2

2 4 2 2 2 2 2

4 cos (4 (1 2 ) )

v L

s

M L

k

M L Z LC d |

2e

=

e + e

(19)

Impedance network design approach

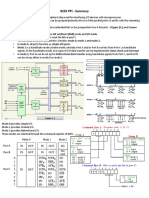

Based on above analysis, detailed design approach of impedance network of single-phase ZSI is

presented with both high-frequency and low-frequency ripple constraints taken into consideration.

Since the paper focuses on impedance network design, only required capacitance C and inductance L

are taken as the design output variables. On the other hand, low (high) frequency DC-link voltage

ripple factor is proportional to low (high) frequency capacitor voltage ripple factor (refer to Equations

(7) and (9), (18) and (19), respectively).

Fig. 6: Detailed design procedure of impedance network

Therefore, the input variables of the design procedure in Fig. 6 should include:

targeted high-frequency capacitor voltage ripple factor k

vc(H)1

targeted high-frequency inductor current ripple factor k

il(H)1

targeted low-frequency capacitor voltage ripple factor k

vc(L)1

targeted low-frequency inductor current ripple factor k

il(L)1

The design procedure includes the following steps:

1) calculating C based on k

vc(H)1

constraint

2) calculating L based on k

il(H)1

constraint

3) checking whether k

vc(L)1

constraint is met, modifying C if not

4) checking whether k

il(L)1

constraint is met, modifying L if not

One single-phase ZSI (as Table I) adopting Simple Boost Control [1] is presented as a design example.

To meet four different groups of design requirements, the corresponding impedance network design

results are listed in Table II. Computer simulation results attained using Matlab/simulink are also

provided (Fig. 7) to verify the effectiveness of the proposed design procedure. It is notable that the

discrepancy existing between design and simulation increases with ripple factor.

Simulation low-frequency capacitor voltage ripple factor is calculated by

( )simu

measured maximum voltage measured minimum voltage

measured maximum voltage measured minimum voltage

vc L k

=

+

(20)

Table I: Parameters of designed single-phase ZSI

Output

voltage/frequency

DC source

(E

s

)

Load

resistance/inductance

Carrier

frequency (f

s

)

Shoot-

through duty

ratio (d

s

)

Modulation

index (M)

55V/50Hz 70V 10 / 2mH 10kHz 0.1 0.8889

Table II: Impedance network design results

Design input Design output Simulation comparison

k

vc(H)1

k

il(H)1

k

il(L)1

k

vc(L)1

(k

v (L)

) L / mH C / uF k

vc(L)

2% 2% 10%

1.00% (1.80%) 2.29 7679 0.96%

1.50% (2.70%) 2.29 5355 1.40%

2.00% (3.60%) 2.29 4192 1.79%

3.00% (5.40%) 2.29 3029 2.50%

0.8 0.805 0.81 0.815

74

76

78

80

82

X: 0.8124

Y: 78.49

C

a

p

a

c

i

t

o

r

v

o

t

l

a

g

e

/

V

Time / s

X: 0.8074

Y: 76.99

(a) L=2.29mH, C=7679uF

0.8 0.805 0.81 0.815

74

76

78

80

82

X: 0.8123

Y: 78.95

C

a

p

a

c

i

t

o

r

v

o

t

l

a

g

e

/

V

Time / s

X: 0.8073

Y: 76.77

(b) L=2.29mH, C=5355uF

0.8 0.805 0.81 0.815

74

76

78

80

82

X: 0.8124

Y: 79.38

C

a

p

a

c

i

t

o

r

v

o

t

l

a

g

e

/

V

Time / s

X: 0.8074

Y: 76.59

(c) L=2.29mH, C=4129uF

0.8 0.805 0.81 0.815

74

76

78

80

82 X: 0.812

Y: 80.19

C

a

p

a

c

i

t

o

r

v

o

t

l

a

g

e

/

V

Time / s

X: 0.8071

Y: 76.28

(d) L=2.29mH, C=3029uF

Fig. 7: Simulation waveforms of capacitor voltage

Experimental verification

The same parameters as the simulation (Table I) are used for laboratory prototype. For illustration of

the accuracy of the proposed design approach, low-frequency capacitor voltage ripple factor is both

theoretically calculated and experimentally measured for individual group of impedance network (L

and C) combination. Experimental results are summarized in Table III and Fig. 8 and shown in detail

in Fig. 9. Experimental low-frequency capacitor voltage ripple factor is calculated by

( )exp

measured peak to peak ripple

2 measured average voltage

vc L k =

(21)

Table III: Comparison between theoretical predictions and experimental results

Impedance network parameters Low-frequency capacitor voltage ripple factor k

vc(L)

L / mH C / uF Theoretical predictions Experimental results

2.29 2700 3.49% 3.09%

2.29 3640 2.38% 2.24%

2.29 4580 1.80% 1.97%

2.29 5400 1.49% 1.41%

2.29 6340 1.24% 1.27%

2.29 7280 1.06% 1.10%

0 1000 2000 3000 4000 5000 6000 7000

0

0.5

1

1.5

2

2.5

3

3.5

4

C / uF

L

o

w

-

f

r

e

q

u

e

n

c

y

c

a

p

a

c

i

t

o

r

v

o

l

t

a

g

e

r

i

p

p

l

e

f

a

c

t

o

r

/

%

Theroretical Predictions

Experimental Results

Fig. 8: Comparison between theoretical predictions and experimental results

From Table III and Fig. 8, it is noted that the accuracy of proposed design method is acceptable for

small ripple, but deteriorates with larger ripple, which is expected from the computer simulation. This

observed feature indicates that for large ripple factor design cases, the design results obtained by

theoretical calculation need further modification by simulation or experimental test. The cause of this

phenomenon could be explained by that the accuracy of linear approximation deteriorates with

increasing ripple.

(a) L=2.29mH, C=2700uF

(b) L=2.29mH, C=3640uF

(c) L=2.29mH, C=4580uF

(d) L=2.29mH, C=5400uF

(e) L=2.29mH, C=6340uF

(f) L=2.29mH, C=7280uF

Fig. 9: Experimental waveforms of DC source voltage (blue) (10V/div), inverter output voltage (green)

(25V/div) and capacitor voltage (red) (1V/div) (AC coupling) with different groups of L and C

combinations; measured peak to peak ripple of capacitor voltage (a)4.80V (b)3.48V (c)3.08V

(d)2.20V (e)1.98V (f)1.72V; measured average capacitor voltage (a)77.57V (b)77.83V (c)78.15V

(d)78.03V (e)78.01V (f)78.11V

Conclusion

In this paper, impedance network design rules of single-phase Z-source inverter are proposed based on

limiting the low-frequency DC-link voltage ripple in an acceptable range. Computer simulation and

experimental results are provided to verify the effectiveness of the proposed design method. For small

ripple design cases, presented design method is of acceptable accuracy. For large ripple factor design

cases, the design results obtained by theoretical calculation may need further modification by

simulation or experimental test. Possible contributing factor to the existing discrepancy for large ripple

factor includes the assumption that linear approximation is of enough accuracy.

References

[1] Fang Zheng Peng: Z-Source Inverter, IEEE Trans. on Ind. Appl., Vol.39, No. 2, pp.504-510, Mar./Apr. 2003.

[2] Fang Zheng Peng, Miaosen Shen, and Zhaoming Qian: Maximum Boost Control of the Z-Source Inverter,

IEEE Trans. on Power Electron., Vol. 20, No. 4, Jul. 2005

[3] Miaosen Shen, Jin Wang, Alan Joseph, Fang Zheng Peng, Leon M. Tolbert, and Donald J. Adams: Constant

Boost Control of the Z-Source Inverter to Minimize Current Ripple and Voltage Stress, IEEE Trans. on Ind.

Appl., Vol. 42, No. 3, May/June 2006

[4] P. C. Loh, D. M. Vilathgamuwa, Y. S. Lai, G. T. Chua and Y. Li: Pulse-width Modulation of Z-source

Inverters, IEEE Trans. on Power Electron., Vol. 20, No. 6, pp.1346-1355, Nov. 2005

[5] Shuitao Yang, Xinping Ding, Fang Zheng Peng and Zhaoming Qian: Unified Control Technique for Z-

Source Inverter, PESC 2008, pp. 3236 3242

[6] Jingbo Liu, Jiangang Hu and Longya Xu: Dynamic Modeling and Analysis of Z Source Converter:

Derivation of AC Small Signal Model and Design-Oriented Analysis, IEEE Trans. on Power Electron., Vol. 22 ,

No.5, pp. 1786 1796, Sep. 2007

[7] Yu Tang, Shaojun Xie, Chaohua Zhang and Zegang Xu: Improved Z-Source Inverter With Reduced Z-

Source Capacitor Voltage Stress and Soft-Start Capability, IEEE Trans. on Power Electron., Vol. 24, No. 2, pp.

409 415, May 2009

[8] Wei Qian, Fang Zheng Peng and Honnyong Cha: Trans-Z-source Inverters, ICPE 2010, pp. 1874 1881

[9] J. Anderson and F. Z. Peng: Four Quasi-Z-Source Inverters, PESC 2008, pp. 2743 2749

[10] Yuan Li, J. Anderson, F. Z. Peng and Dichen Liu: Quasi-Z-Source Inverter for Photovoltaic Power

Generation Systems, APEC 2009, pp. 918 924

[11] Xinping Ding, Zhaoming Qian, Shuitao Yang, Bin Cui and Fang Zheng Peng: A New Adjustable-Speed

Drives (ASD) System Based on High-Performance Z-Source Inverter, IAS 2007, pp. 2327 2332

[12] Zhi Jian Zhou, Xing Zhang, Po Xu and W. X. Shen: Single-Phase Uninterruptible Power Supply Based on

Z-Source Inverter, IEEE Trans. on Ind. Electron., Vol. 55, No.8, pp. 2997 3004, Aug. 2008

[13] Sumedha Rajakaruna and Laksumana Jayawickrama: Steady-State Analysis and Designing Impedance

Network of Z-Source Inverters, IEEE Trans. on Ind. Electron., Vol. 57, No. 7, pp. 2483 - 2491, Jul. 2010

Das könnte Ihnen auch gefallen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- A FormulaDokument2 SeitenA FormulaUmesh Rao H NNoch keine Bewertungen

- Unit 1Dokument52 SeitenUnit 1naga7389Noch keine Bewertungen

- B.Tech. ITDokument108 SeitenB.Tech. ITPushpavalli MohanNoch keine Bewertungen

- Control System Lab ManualDokument52 SeitenControl System Lab ManualMohammad Umar RehmanNoch keine Bewertungen

- Lab Experiment For Synchro Transmitter and Receiver PDFDokument8 SeitenLab Experiment For Synchro Transmitter and Receiver PDFnaga7389100% (1)

- Lab Experiment For Synchro Transmitter and Receiver PDFDokument8 SeitenLab Experiment For Synchro Transmitter and Receiver PDFnaga7389100% (1)

- 2012 Beee Nov - Dec PDFDokument3 Seiten2012 Beee Nov - Dec PDFnaga7389Noch keine Bewertungen

- Kings College of EngineeringDokument12 SeitenKings College of Engineeringsubugana100% (1)

- Data Structures Lab ManualDokument36 SeitenData Structures Lab ManualKaral Marx SNoch keine Bewertungen

- 2014 Beee May - Jun PDFDokument2 Seiten2014 Beee May - Jun PDFnaga7389Noch keine Bewertungen

- Lecture Notes-Basic Electrical and Electronics EngineeringDokument30 SeitenLecture Notes-Basic Electrical and Electronics Engineeringalfanardm100% (4)

- GE6252 Basic Electrical and Electronics Engineering Regulation 2013 Lecture Notes PDFDokument143 SeitenGE6252 Basic Electrical and Electronics Engineering Regulation 2013 Lecture Notes PDFVenkatesan Swamy100% (1)

- Lecture Notes-Basic Electrical and Electronics EngineeringDokument30 SeitenLecture Notes-Basic Electrical and Electronics Engineeringalfanardm100% (4)

- 2013 BEEE Nov - Dec PDFDokument2 Seiten2013 BEEE Nov - Dec PDFnaga7389Noch keine Bewertungen

- Ge6252 Beee Syllabus PDFDokument1 SeiteGe6252 Beee Syllabus PDFnaga7389Noch keine Bewertungen

- NHMDokument1 SeiteNHMnaga7389Noch keine Bewertungen

- BEEE Important Questions 16 MarksDokument5 SeitenBEEE Important Questions 16 Marksaeroheroz25% (4)

- Ministry of New and Renewable Energy: Download Application FormatDokument1 SeiteMinistry of New and Renewable Energy: Download Application Formatnaga7389Noch keine Bewertungen

- GATE Electrical Engineering 2011Dokument18 SeitenGATE Electrical Engineering 2011naga7389Noch keine Bewertungen

- NN1-Architecture and Performance of Neural Networks For Efficient AC Control in BuildingsDokument20 SeitenNN1-Architecture and Performance of Neural Networks For Efficient AC Control in Buildingsnaga7389Noch keine Bewertungen

- Cop MPG-DSTDokument10 SeitenCop MPG-DSTnaga7389Noch keine Bewertungen

- GATE2013Solution EE Set BDokument51 SeitenGATE2013Solution EE Set BManiranjan RoutNoch keine Bewertungen

- PRJ 6712 839Dokument30 SeitenPRJ 6712 839naga7389Noch keine Bewertungen

- Lab Equipments AU Chennai 2013Dokument29 SeitenLab Equipments AU Chennai 2013naga7389Noch keine Bewertungen

- Sibi 2Dokument5 SeitenSibi 2naga7389Noch keine Bewertungen

- RPNG: A Tool For Random Process Network Generation: Prediction MB - Data3 MB - Pred - Prop MB - Prop Ref - FramesDokument13 SeitenRPNG: A Tool For Random Process Network Generation: Prediction MB - Data3 MB - Pred - Prop MB - Prop Ref - Framesnaga7389Noch keine Bewertungen

- BiomassS PDFDokument4 SeitenBiomassS PDFnaga7389Noch keine Bewertungen

- Lab Equipments AU Chennai 2013Dokument29 SeitenLab Equipments AU Chennai 2013naga7389Noch keine Bewertungen

- Filter DesignDokument6 SeitenFilter Designnaga7389Noch keine Bewertungen

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- Diodo BZXDokument3 SeitenDiodo BZXAndrey SilvaNoch keine Bewertungen

- Senb8604 02 02 - 44606Dokument41 SeitenSenb8604 02 02 - 44606Christian BedoyaNoch keine Bewertungen

- Satellite L755 SP5167CMDokument3 SeitenSatellite L755 SP5167CMspk343Noch keine Bewertungen

- Pidnn Arduino2Dokument2 SeitenPidnn Arduino2Byron Xavier Lima CedilloNoch keine Bewertungen

- 15 - IPPC-6152A - 6172A - 6192A - DS Touch PC CatalogDokument3 Seiten15 - IPPC-6152A - 6172A - 6192A - DS Touch PC CatalogChan Chi Wong PenNoch keine Bewertungen

- Surge Arresters and Surge Suppressors in TransformerDokument22 SeitenSurge Arresters and Surge Suppressors in TransformerMegan ChaiNoch keine Bewertungen

- NI cRIO-9066 - 376186a - 02Dokument8 SeitenNI cRIO-9066 - 376186a - 02angeljchrNoch keine Bewertungen

- EC6302 Digital ElectronicsDokument12 SeitenEC6302 Digital ElectronicsJabeen BanuNoch keine Bewertungen

- AN78010 - NXP Antenna TheoryDokument26 SeitenAN78010 - NXP Antenna TheoryhbaocrNoch keine Bewertungen

- Program Control InstructionDokument52 SeitenProgram Control InstructionriajdcNoch keine Bewertungen

- DDS Function GeneratorDokument3 SeitenDDS Function GeneratorjckworldNoch keine Bewertungen

- Kg545 II UserDokument86 SeitenKg545 II Usersaneesh81100% (1)

- Hikvision Supported Device On MilestoneDokument53 SeitenHikvision Supported Device On MilestoneFadli BadarudinNoch keine Bewertungen

- TH-9800 - RF Test ReportDokument43 SeitenTH-9800 - RF Test ReportBenjamin DoverNoch keine Bewertungen

- Fabrication Mod 2Dokument16 SeitenFabrication Mod 2albin shajanNoch keine Bewertungen

- NSN Lte-Advanced White PaperDokument20 SeitenNSN Lte-Advanced White Paperjoseph221106Noch keine Bewertungen

- DLD ProjectDokument2 SeitenDLD ProjectAafi QaisarNoch keine Bewertungen

- Class 2Dokument21 SeitenClass 2md sakhwat hossainNoch keine Bewertungen

- DMA ControllerDokument9 SeitenDMA ControllerVanga Shiva Rama KrishnaNoch keine Bewertungen

- 8255 PPI-handouts To StudentsDokument4 Seiten8255 PPI-handouts To StudentsSurinder SuriNoch keine Bewertungen

- 5458 SP-IDLU-UST110-CUO8O-32PP (EnV011117)Dokument4 Seiten5458 SP-IDLU-UST110-CUO8O-32PP (EnV011117)eltioelpanNoch keine Bewertungen

- System Component and Protection DevicesDokument16 SeitenSystem Component and Protection DevicesSandeep KumarNoch keine Bewertungen

- TCA9803 Use Cases & Issues Slva878Dokument8 SeitenTCA9803 Use Cases & Issues Slva878Mogra BlissNoch keine Bewertungen

- BEI-TT10K Product Datasheet - CDokument2 SeitenBEI-TT10K Product Datasheet - CSergio Ivan Merchan MejiaNoch keine Bewertungen

- 16 Bit Comparator Using 4 Bit ComparatorsDokument7 Seiten16 Bit Comparator Using 4 Bit ComparatorsSudhakara RaoNoch keine Bewertungen

- Overview Aerials HRDFDokument17 SeitenOverview Aerials HRDFChavaNoch keine Bewertungen

- DO 9404 Dual Regulating Indicator With Microprocessor Configuration and Two Inputs, For Voltage or CurrentDokument3 SeitenDO 9404 Dual Regulating Indicator With Microprocessor Configuration and Two Inputs, For Voltage or CurrentreyspartaNoch keine Bewertungen

- Support Overload ManualDokument6 SeitenSupport Overload ManualhabibullaNoch keine Bewertungen

- Relay Setting For 7ut51 Differential Protection RelayDokument12 SeitenRelay Setting For 7ut51 Differential Protection Relayyesrojas100% (1)

- BRO SecuriFire Systemdescription enDokument56 SeitenBRO SecuriFire Systemdescription enamad4youNoch keine Bewertungen