Beruflich Dokumente

Kultur Dokumente

VHDL (VHSIC Hardware Description Language) Is A Description Language For

Hochgeladen von

Omkar SheteOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

VHDL (VHSIC Hardware Description Language) Is A Description Language For

Hochgeladen von

Omkar SheteCopyright:

Verfügbare Formate

ASSIGNMENT NO: 15 PROBLEM STATEMENT: Implement Combinational Circuits(Using VHDL) THEORY: Adder,Mux

VHDL (VHSIC Hardware Description Language) is a description language for electronic digital systems. The development of this language was driven out of the need, to create a standard language for the documentation of the structure and function of integrated circuits (ICs). The development of VHDL was initiated at the begin of the eighties out of the united states Government's VHSIC (Very High Speed Integrated Circuit)-Project of the American defense Ministry (Department of Defense, DoD). In December 1987 it was standardized by the IEEE (Institute of Electrical and Electronic Engineers) as IEEE 1076-1987 Norm. Since IEEE-Standards are continuously being developed new standardization follows every five year. The latest IEEE 1076-1993 standard was completed in 1993. Since begin of the nineties, VHDL gains worldwide an increasing significance in the electronic development. The language serves meanwhile, in the design and verification of complex digital circuits and systems, not only the purpose of documentation, but also increasingly the structuring, specification, modeling, simulation and synthesis in the development of digital hardware. There is nowadays a large number of VHDL Tools which work on various design levels for which VHDL serves as a data exchange format. Hence graphic editors (schematic editors) are being used for the development of wiring diagram that visualize the structural description of a design on the logic level. A VHDL code generator which is integrated in the editor can generate therefrom a VHDL description for the design. Hence a component net list on the circuit level can be generated from the synthesis able VHDL code of this description. VHDL simulators are being used for the verification of separated development steps or the whole design. Those tools allow the detection and removal of design errors in an earlier stage of the development phase. Even under use of VHDL tools a manual adjustment or optimization of the VHDL code must be frequently tackled. In this case detailed knowledge of the VHDL language is absolutely necessary.

CONCLUSION: Adder,MUX using VHDL has been studied.

ASSIGNMENT NO: 16 PROBLEM STATEMENT: Implement Sequential Circuits (Using VHDL) - Asynchronous, Synchronous Counter

THEORY:

VHDL (VHSIC Hardware Description Language) is a description language for electronic digital systems. The development of this language was driven out of the need, to create a standard language for the documentation of the structure and function of integrated circuits (ICs). The development of VHDL was initiated at the begin of the eighties out of the united states Government's VHSIC (Very High Speed Integrated Circuit)-Project of the American defense Ministry (Department of Defense, DoD). In December 1987 it was standardized by the IEEE (Institute of Electrical and Electronic Engineers) as IEEE 1076-1987 Norm. Since IEEE-Standards are continuously being developed new standardization follows every five year. The latest IEEE 1076-1993 standard was completed in 1993. Since begin of the nineties, VHDL gains worldwide an increasing significance in the electronic development. The language serves meanwhile, in the design and verification of complex digital circuits and systems, not only the purpose of documentation, but also increasingly the structuring, specification, modeling, simulation and synthesis in the development of digital hardware. There is nowadays a large number of VHDL Tools which work on various design levels for which VHDL serves as a data exchange format. Hence graphic editors (schematic editors) are being used for the development of wiring diagram that visualize the structural description of a design on the logic level. A VHDL code generator which is integrated in the editor can generate therefrom a VHDL description for the design. Hence a component net list on the circuit level can be generated from the synthesis able VHDL code of this description. VHDL simulators are being used for the verification of separated development steps or the whole design. Those tools allow the detection and removal of design errors in an earlier stage of the development phase. Even under use of VHDL tools a manual adjustment or optimization of the VHDL code must be frequently tackled. In this case detailed knowledge of the VHDL language is absolutely necessary.

CONCLUSION: Asynchronous, Synchronous Counter using VHDL has been studied.

ASSIGNMENT NO: 17 PROBLEM STATEMENT: I Implement Basic gates using VHDL THEORY:

VHDL (VHSIC Hardware Description Language) is a description language for electronic digital systems. The development of this language was driven out of the need, to create a standard language for the documentation of the structure and function of integrated circuits (ICs). The development of VHDL was initiated at the begin of the eighties out of the united states Government's VHSIC (Very High Speed Integrated Circuit)-Project of the American defense Ministry (Department of Defense, DoD). In December 1987 it was standardized by the IEEE (Institute of Electrical and Electronic Engineers) as IEEE 1076-1987 Norm. Since IEEE-Standards are continuously being developed new standardization follows every five year. The latest IEEE 1076-1993 standard was completed in 1993. Since begin of the nineties, VHDL gains worldwide an increasing significance in the electronic development. The language serves meanwhile, in the design and verification of complex digital circuits and systems, not only the purpose of documentation, but also increasingly the structuring, specification, modeling, simulation and synthesis in the development of digital hardware. There is nowadays a large number of VHDL Tools which work on various design levels for which VHDL serves as a data exchange format. Hence graphic editors (schematic editors) are being used for the development of wiring diagram that visualize the structural description of a design on the logic level. A VHDL code generator which is integrated in the editor can generate therefrom a VHDL description for the design. Hence a component net list on the circuit level can be generated from the synthesis able VHDL code of this description. VHDL simulators are being used for the verification of separated development steps or the whole design. Those tools allow the detection and removal of design errors in an earlier stage of the development phase. Even under use of VHDL tools a manual adjustment or optimization of the VHDL code must be frequently tackled. In this case detailed knowledge of the VHDL language is absolutely necessary.

CONCLUSION: Basic gates using VHDL has been studied.

INDEX

SR. NO.

TITLE OF THE EXPERIMENT

01 02 03 04 05 06 07 08 09

10 11 12 13 14 15 16 17 18 19

Code converters, e.g. Excess-3 to BCD and vice versa. Multiplexers: Application like Realization of Boolean expression using Multiplexer Design, Built and test 4-bit BCD adder by using 4-bit binary IC-7483 Parity Generator and Parity Detector Design a ROM using DEMUX IC 74138 and store the data. Design a 3-bit asynchronous counter using MS J-K flip-flop (ic7476). Build and practically test your circuit. Design, build and practically test 2-bit synchronous UP-DOWN counter using J-K flip-flop. Design, build and practically test sequential circuit, which generate the following sequence: 0-1-0-0-1 Design & Implement Sequence Generator for the given sequence by using J-K flip-flops (IC 7476). Avoid the lockout condition & Draw Bush diagrams required to bring the counter from invalid state to Valid state. -1-3-5-7Design and implement mod-10 and mod 100 by using decade counter (7490). Design 4 bit Pseudo random sequence generator using shift register IC 74194. Build and practically test your circuit. Design & Implement 4-Bit Barrel Shifter to perform Shift &Rotation operation to left & right Design, built & test Sequential circuit, which detect the following Sequence For both Mealy & Moore circuit -1-1-0Design an ASM chart and ckt. for the given waveforms Combinational Circuits(Using VHDL) - Adder,Mux Sequential Circuits (Using VHDL) - Asynchronous, Synchronous Counter Basic gates using VHDL Annex. A: Distribution List Annex B: Revision Record

Das könnte Ihnen auch gefallen

- ERS 220 Digital Systems: HDL/VHDL HDL/VHDL HDL/VHDL HDL/VHDLDokument36 SeitenERS 220 Digital Systems: HDL/VHDL HDL/VHDL HDL/VHDL HDL/VHDLtoyboy108Noch keine Bewertungen

- Intermediate C Programming for the PIC Microcontroller: Simplifying Embedded ProgrammingVon EverandIntermediate C Programming for the PIC Microcontroller: Simplifying Embedded ProgrammingNoch keine Bewertungen

- Welcome To The VHDL LanguageDokument399 SeitenWelcome To The VHDL LanguageardserNoch keine Bewertungen

- Digital Integrated Circuit Design Using Verilog and SystemverilogVon EverandDigital Integrated Circuit Design Using Verilog and SystemverilogBewertung: 3 von 5 Sternen3/5 (4)

- Seminar Report On Vhsic Hardware Description Language: (VHDL)Dokument20 SeitenSeminar Report On Vhsic Hardware Description Language: (VHDL)Jasdeep SinghNoch keine Bewertungen

- Main Topics:: Circuit Design Based On VHDL VHDL Basics Advanced VHDL Language Structures Circuit ExamplesDokument33 SeitenMain Topics:: Circuit Design Based On VHDL VHDL Basics Advanced VHDL Language Structures Circuit ExamplesnamratashakyaNoch keine Bewertungen

- VHDLDokument33 SeitenVHDLsansureNoch keine Bewertungen

- VLSI Design for Video Coding: H.264/AVC Encoding from Standard Specification to ChipVon EverandVLSI Design for Video Coding: H.264/AVC Encoding from Standard Specification to ChipNoch keine Bewertungen

- Main Topics:: Circuit Design Based On VHDL VHDL Basics Advanced VHDL Language Structures Circuit ExamplesDokument33 SeitenMain Topics:: Circuit Design Based On VHDL VHDL Basics Advanced VHDL Language Structures Circuit Examplesnandan_pappuNoch keine Bewertungen

- Modern Arm Assembly Language Programming: Covers Armv8-A 32-bit, 64-bit, and SIMDVon EverandModern Arm Assembly Language Programming: Covers Armv8-A 32-bit, 64-bit, and SIMDNoch keine Bewertungen

- Module 4A HDL Intro 04-12-23Dokument15 SeitenModule 4A HDL Intro 04-12-23raovinayakm2Noch keine Bewertungen

- High Efficiency Video Coding (HEVC): Algorithms and ArchitecturesVon EverandHigh Efficiency Video Coding (HEVC): Algorithms and ArchitecturesNoch keine Bewertungen

- 16ECU19 - VLSI Design and VHDL: Introduction and Basic Concept of VHDL Session IDokument42 Seiten16ECU19 - VLSI Design and VHDL: Introduction and Basic Concept of VHDL Session Iசெல்வம் முத்துராமன்Noch keine Bewertungen

- VHDLDokument2 SeitenVHDLBiswaranjan MohapatraNoch keine Bewertungen

- VHDL CourseworkDokument7 SeitenVHDL Courseworkafiwhwlwx100% (2)

- Lecture 4Dokument4 SeitenLecture 4litoduterNoch keine Bewertungen

- A VHDL Scalable-Encryption-AlgorithmDokument79 SeitenA VHDL Scalable-Encryption-AlgorithmghionoiucNoch keine Bewertungen

- DSD Using VHDLDokument54 SeitenDSD Using VHDLShashi Bhushan Kotwal100% (1)

- VHDLDokument94 SeitenVHDLAkshay MandawariaNoch keine Bewertungen

- Comprehensive Study of Flow To Program FPGA Kit Using VHDLDokument4 SeitenComprehensive Study of Flow To Program FPGA Kit Using VHDLIJRECENoch keine Bewertungen

- VHDL Training ReportDokument25 SeitenVHDL Training ReportAbhishek Kumar63% (8)

- Intro VHDL PDFDokument12 SeitenIntro VHDL PDFkokome350% (1)

- VLSI System Design & Modeling TechniqueDokument46 SeitenVLSI System Design & Modeling TechniqueShuvodip DasNoch keine Bewertungen

- VHDLDokument5 SeitenVHDLRoemil CabalNoch keine Bewertungen

- History of VHDL DevelopmentDokument17 SeitenHistory of VHDL DevelopmentRittal 96Noch keine Bewertungen

- Project Report On Implementation of Some Basic Hardware Designs at FPGA Using VERILOGDokument27 SeitenProject Report On Implementation of Some Basic Hardware Designs at FPGA Using VERILOGAnkitGarg100% (1)

- 1.1 Vlsi (Very Large Scale Integeration)Dokument36 Seiten1.1 Vlsi (Very Large Scale Integeration)Rishiraj NalandiNoch keine Bewertungen

- Technical Aspects of Creating and Assessing A Learning Environment in Digital Electronics For High School StudentsDokument8 SeitenTechnical Aspects of Creating and Assessing A Learning Environment in Digital Electronics For High School StudentsKishore KNoch keine Bewertungen

- Essential VHDLDokument127 SeitenEssential VHDLMelody ShieldsNoch keine Bewertungen

- Introduction To VHDL: EE 595 EDA / ASIC Design LabDokument20 SeitenIntroduction To VHDL: EE 595 EDA / ASIC Design LabSudipta DasNoch keine Bewertungen

- Design and Implementation of 32-Bit Alu On Xilinx Fpga Using VHDLDokument38 SeitenDesign and Implementation of 32-Bit Alu On Xilinx Fpga Using VHDLNigam MeherNoch keine Bewertungen

- VHDLDokument324 SeitenVHDLKrishna Chaitanya T75% (4)

- Thesis Based On VHDLDokument8 SeitenThesis Based On VHDLevkrjniig100% (2)

- VHDL Simulation of Fir FilterDokument66 SeitenVHDL Simulation of Fir FilterSaurabh Minotra67% (3)

- Vlsi Minor Training ReportDokument16 SeitenVlsi Minor Training ReportAditya KumarNoch keine Bewertungen

- Vindhya Institute of Technology and ScienceDokument20 SeitenVindhya Institute of Technology and ScienceApoorva PandeyNoch keine Bewertungen

- Ahp31 Ma1phDokument24 SeitenAhp31 Ma1phRittal 96Noch keine Bewertungen

- 1.introduction To HDLsDokument32 Seiten1.introduction To HDLsSiby JosephNoch keine Bewertungen

- Vlsi Design Using VHDLDokument20 SeitenVlsi Design Using VHDLAbhinav ShuklaNoch keine Bewertungen

- FPGA-Based Advanced Real Traffic Light Controller SystemDokument89 SeitenFPGA-Based Advanced Real Traffic Light Controller SystemAnil Mahankali100% (1)

- Verilog (About Tool and Steps)Dokument4 SeitenVerilog (About Tool and Steps)udayNoch keine Bewertungen

- About VlsiDokument14 SeitenAbout VlsiAnonymous 1aqlkZNoch keine Bewertungen

- Vlsi VivaDokument9 SeitenVlsi VivaNimisha KhandelwalNoch keine Bewertungen

- Module 1: Overview of Digital Design With Verilog HDLDokument48 SeitenModule 1: Overview of Digital Design With Verilog HDLGranTorinoNoch keine Bewertungen

- 0769500234-Digital Systems DesignDokument515 Seiten0769500234-Digital Systems DesignG Abhishek Rao100% (1)

- HDL Lab Ece Uvce Jan20Dokument50 SeitenHDL Lab Ece Uvce Jan20Bhavid ANoch keine Bewertungen

- BEC7L1 - Digital Cmos Vlsi-LabDokument66 SeitenBEC7L1 - Digital Cmos Vlsi-LabRamkumardevendiranDevenNoch keine Bewertungen

- Module 1 PDFDokument15 SeitenModule 1 PDFShivu KNoch keine Bewertungen

- Vlsi VHDLDokument22 SeitenVlsi VHDLsamiularefin2000Noch keine Bewertungen

- Module - 5 Introduction To VHDL 5.1: ObjectivesDokument14 SeitenModule - 5 Introduction To VHDL 5.1: Objectivesabhilash gowdaNoch keine Bewertungen

- Basic VHDL Course: BY Shin IgneelDokument19 SeitenBasic VHDL Course: BY Shin IgneelShin IgneelNoch keine Bewertungen

- VHDL Unit 2 Part 1Dokument20 SeitenVHDL Unit 2 Part 1TanishaNoch keine Bewertungen

- HDL Manual 2018 19 UpdatedDokument59 SeitenHDL Manual 2018 19 UpdatedNisha TNoch keine Bewertungen

- VHDLDokument7 SeitenVHDLmaya9988Noch keine Bewertungen

- Case Study VHDLDokument6 SeitenCase Study VHDLSneha KaurNoch keine Bewertungen

- VHDL Unit 2 Part 3Dokument45 SeitenVHDL Unit 2 Part 3TanishaNoch keine Bewertungen

- VHDL-Unit-2-Part-5 1Dokument92 SeitenVHDL-Unit-2-Part-5 1TanishaNoch keine Bewertungen

- SolarDokument1 SeiteSolarOmkar SheteNoch keine Bewertungen

- Solar PhotovoltaicsDokument1 SeiteSolar PhotovoltaicsOmkar SheteNoch keine Bewertungen

- DesignDokument1 SeiteDesignOmkar SheteNoch keine Bewertungen

- Interrupts in PIC18Fxxx: DefinitionDokument1 SeiteInterrupts in PIC18Fxxx: DefinitionOmkar SheteNoch keine Bewertungen

- Electrochemical Cells Flashlights Smartphones Electric Cars Electric Power Cathode Anode ElectrolytesDokument1 SeiteElectrochemical Cells Flashlights Smartphones Electric Cars Electric Power Cathode Anode ElectrolytesfikaduNoch keine Bewertungen

- Solar PhotovoltaicsDokument1 SeiteSolar PhotovoltaicsOmkar SheteNoch keine Bewertungen

- Feed-In Tariff Net Metering Decentralized Electricity Generation Grid-Tie InverterDokument1 SeiteFeed-In Tariff Net Metering Decentralized Electricity Generation Grid-Tie InverterOmkar SheteNoch keine Bewertungen

- Juice Machine PDFDokument6 SeitenJuice Machine PDFOmkar SheteNoch keine Bewertungen

- You Shouldn't Have To Pay To Learn! Master The Basics of Computer Science and Programming Using Python in Just 9 Weeks in This Introductory Online Course From MITDokument1 SeiteYou Shouldn't Have To Pay To Learn! Master The Basics of Computer Science and Programming Using Python in Just 9 Weeks in This Introductory Online Course From MITOmkar SheteNoch keine Bewertungen

- Has On-Chip. EEPROM or Flash Memory of 4 Kb. SeveraDokument1 SeiteHas On-Chip. EEPROM or Flash Memory of 4 Kb. SeveraOmkar SheteNoch keine Bewertungen

- Reader Should ... - Selection From 8051 Microcontrollers, 2nd EditionDokument1 SeiteReader Should ... - Selection From 8051 Microcontrollers, 2nd EditionOmkar SheteNoch keine Bewertungen

- The 8051 Microcontroller and Embedded Systems. CHAPTER 14. 8051 INTERFACING TO EXTERNAL MEMORY. 2. OBJECTIVES. Contrast and CompareDokument1 SeiteThe 8051 Microcontroller and Embedded Systems. CHAPTER 14. 8051 INTERFACING TO EXTERNAL MEMORY. 2. OBJECTIVES. Contrast and CompareOmkar SheteNoch keine Bewertungen

- AyalaDokument1 SeiteAyalaOmkar SheteNoch keine Bewertungen

- An Interrupt Is An External or Internal Event That Interrupts The Microcontroller To Inform It That A Device Needs Its ServiceDokument1 SeiteAn Interrupt Is An External or Internal Event That Interrupts The Microcontroller To Inform It That A Device Needs Its ServiceOmkar SheteNoch keine Bewertungen

- IJSRP Paper Submission Format Single ColumnDokument3 SeitenIJSRP Paper Submission Format Single ColumnpodamakriNoch keine Bewertungen

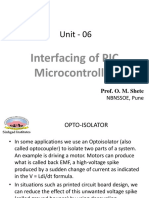

- Unit - 06: Interfacing of PIC MicrocontrollerDokument7 SeitenUnit - 06: Interfacing of PIC MicrocontrollerOmkar SheteNoch keine Bewertungen

- 1234Dokument1 Seite1234Omkar SheteNoch keine Bewertungen

- 1Dokument1 Seite1Omkar SheteNoch keine Bewertungen

- PaperFormat (MS Word)Dokument5 SeitenPaperFormat (MS Word)adylanNoch keine Bewertungen

- PIC16F877A-Based Temperature Monitoring SystemDokument1 SeitePIC16F877A-Based Temperature Monitoring SystemOmkar SheteNoch keine Bewertungen

- Two Day Induction Programme Was Conducted For First Year Engineering Students On 22 July and 23 July 2013Dokument1 SeiteTwo Day Induction Programme Was Conducted For First Year Engineering Students On 22 July and 23 July 2013Omkar SheteNoch keine Bewertungen

- EnergyDokument1 SeiteEnergyOmkar SheteNoch keine Bewertungen

- IJEAT Paper TemplateDokument4 SeitenIJEAT Paper TemplateAvinash KambleNoch keine Bewertungen

- ExamDokument1 SeiteExamOmkar SheteNoch keine Bewertungen

- CDMDokument1 SeiteCDMOmkar SheteNoch keine Bewertungen

- KrishDokument1 SeiteKrishOmkar SheteNoch keine Bewertungen

- Afs Admission Form 2015-16Dokument3 SeitenAfs Admission Form 2015-16Mitra DiyaNoch keine Bewertungen

- CDMDokument1 SeiteCDMOmkar SheteNoch keine Bewertungen

- IEEE Outline FormatDokument3 SeitenIEEE Outline FormatAlex HerrmannNoch keine Bewertungen

- Design For Testability NotesDokument41 SeitenDesign For Testability NotesNaga Nithesh100% (3)

- Resolve Infinite Loop Zero Delay GLSDokument9 SeitenResolve Infinite Loop Zero Delay GLSJagadish KgNoch keine Bewertungen

- Asic Design HbookDokument101 SeitenAsic Design Hbooksrbhgpt72100% (1)

- Verilog - ManoDokument43 SeitenVerilog - ManoMohammod Ahad ArianNoch keine Bewertungen

- Introduction Simulation Modelsim Altera and Altera Quartus II SetupDokument7 SeitenIntroduction Simulation Modelsim Altera and Altera Quartus II SetupMoo0% (1)

- Siemens SW Tessent IJTAG FS 82810 C3Dokument3 SeitenSiemens SW Tessent IJTAG FS 82810 C3rajitkarmakarNoch keine Bewertungen

- Dwnload Full Digital Systems Design Using Verilog 1st Edition Roth Solutions Manual PDFDokument35 SeitenDwnload Full Digital Systems Design Using Verilog 1st Edition Roth Solutions Manual PDFhaodienb6qj100% (13)

- Fire Protection List of Effective PagesDokument81 SeitenFire Protection List of Effective PagesRafael H Juliao BolañoNoch keine Bewertungen

- Timing Closure: VLSI Physical Design: From Graph Partitioning To Timing ClosureDokument74 SeitenTiming Closure: VLSI Physical Design: From Graph Partitioning To Timing ClosureVamsi KrishnaNoch keine Bewertungen

- Lecture 1 3Dokument62 SeitenLecture 1 3Sivakumar PothirajNoch keine Bewertungen

- Design: PlanningDokument214 SeitenDesign: PlanningShounak DasNoch keine Bewertungen

- Cat7 en WebDokument432 SeitenCat7 en WebGoran MladenovicNoch keine Bewertungen

- Arun Kumar Paper Tcs ComaniesDokument68 SeitenArun Kumar Paper Tcs ComaniesDanielle DeanNoch keine Bewertungen

- Timing Analysis of Source Synchronous Interface Using ALTLVDS v1.0Dokument6 SeitenTiming Analysis of Source Synchronous Interface Using ALTLVDS v1.0huangjsmikeNoch keine Bewertungen

- 357-Article Text-510-1-10-20190306Dokument5 Seiten357-Article Text-510-1-10-20190306IdhamNoch keine Bewertungen

- Esp-Cv: Custom Design Formal Equivalence Checking Based On Symbolic SimulationDokument5 SeitenEsp-Cv: Custom Design Formal Equivalence Checking Based On Symbolic Simulationdubey100% (1)

- VOX Guitar Organ V251 SchematicDokument5 SeitenVOX Guitar Organ V251 SchematicdodNoch keine Bewertungen

- Dr.G.Senthil Kumar - VLSI - Design - LabDokument121 SeitenDr.G.Senthil Kumar - VLSI - Design - LabNilesh VermaNoch keine Bewertungen

- CAD Tools For Low PowerDokument29 SeitenCAD Tools For Low PowerSEHARABANU MULLANoch keine Bewertungen

- Lattice Dec1306 Clock Problems Digital Systems PDFDokument23 SeitenLattice Dec1306 Clock Problems Digital Systems PDFdeveloper_2k11Noch keine Bewertungen

- Asus GL752VW - RG SchematicDokument7 SeitenAsus GL752VW - RG SchematicazertNoch keine Bewertungen

- Chapter 1 - Overview On Digital IC DesignDokument45 SeitenChapter 1 - Overview On Digital IC DesignNorjuliana Muhammad TahaNoch keine Bewertungen

- EE-421 Digital System Design Lab (Fall 2016) : Or, NotDokument12 SeitenEE-421 Digital System Design Lab (Fall 2016) : Or, NotBilal SiddiqueNoch keine Bewertungen

- System Level Timing Analysis 1Dokument9 SeitenSystem Level Timing Analysis 1MaheshNoch keine Bewertungen

- Verilog Text BookDokument431 SeitenVerilog Text Bookprabhakar reddyNoch keine Bewertungen

- Cours2 - Design and Simulation Using VHDLDokument93 SeitenCours2 - Design and Simulation Using VHDLsoundouselhammanyNoch keine Bewertungen

- RTL Coding GuidelinesDokument35 SeitenRTL Coding GuidelinesPrabakaran EllaiyappanNoch keine Bewertungen

- Contador 0-59 en VHDLDokument12 SeitenContador 0-59 en VHDLkattyNoch keine Bewertungen

- VerilogDokument104 SeitenVerilogPhu TranNoch keine Bewertungen

- Lecture 3 - Design FlowDokument18 SeitenLecture 3 - Design Flowkumarkankipati19100% (1)

- Calculus Workbook For Dummies with Online PracticeVon EverandCalculus Workbook For Dummies with Online PracticeBewertung: 3.5 von 5 Sternen3.5/5 (8)

- Basic Math & Pre-Algebra Workbook For Dummies with Online PracticeVon EverandBasic Math & Pre-Algebra Workbook For Dummies with Online PracticeBewertung: 4 von 5 Sternen4/5 (2)

- Quantum Physics: A Beginners Guide to How Quantum Physics Affects Everything around UsVon EverandQuantum Physics: A Beginners Guide to How Quantum Physics Affects Everything around UsBewertung: 4.5 von 5 Sternen4.5/5 (3)

- Mathematical Mindsets: Unleashing Students' Potential through Creative Math, Inspiring Messages and Innovative TeachingVon EverandMathematical Mindsets: Unleashing Students' Potential through Creative Math, Inspiring Messages and Innovative TeachingBewertung: 4.5 von 5 Sternen4.5/5 (21)

- Mental Math: How to Develop a Mind for Numbers, Rapid Calculations and Creative Math Tricks (Including Special Speed Math for SAT, GMAT and GRE Students)Von EverandMental Math: How to Develop a Mind for Numbers, Rapid Calculations and Creative Math Tricks (Including Special Speed Math for SAT, GMAT and GRE Students)Noch keine Bewertungen

- Mental Math Secrets - How To Be a Human CalculatorVon EverandMental Math Secrets - How To Be a Human CalculatorBewertung: 5 von 5 Sternen5/5 (3)

- Images of Mathematics Viewed Through Number, Algebra, and GeometryVon EverandImages of Mathematics Viewed Through Number, Algebra, and GeometryNoch keine Bewertungen

- Build a Mathematical Mind - Even If You Think You Can't Have One: Become a Pattern Detective. Boost Your Critical and Logical Thinking Skills.Von EverandBuild a Mathematical Mind - Even If You Think You Can't Have One: Become a Pattern Detective. Boost Your Critical and Logical Thinking Skills.Bewertung: 5 von 5 Sternen5/5 (1)

- How Math Explains the World: A Guide to the Power of Numbers, from Car Repair to Modern PhysicsVon EverandHow Math Explains the World: A Guide to the Power of Numbers, from Car Repair to Modern PhysicsBewertung: 3.5 von 5 Sternen3.5/5 (9)

- A Mathematician's Lament: How School Cheats Us Out of Our Most Fascinating and Imaginative Art FormVon EverandA Mathematician's Lament: How School Cheats Us Out of Our Most Fascinating and Imaginative Art FormBewertung: 5 von 5 Sternen5/5 (5)

- A Guide to Success with Math: An Interactive Approach to Understanding and Teaching Orton Gillingham MathVon EverandA Guide to Success with Math: An Interactive Approach to Understanding and Teaching Orton Gillingham MathBewertung: 5 von 5 Sternen5/5 (1)