Beruflich Dokumente

Kultur Dokumente

Design and Analysis of ZVZCS Converter With Active Clamping

Hochgeladen von

editor9891Originalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Design and Analysis of ZVZCS Converter With Active Clamping

Hochgeladen von

editor9891Copyright:

Verfügbare Formate

J.

Sivavara Prasad et al, International Journal of Computer Science & Communication Networks,Vol 1(1),September-October 2011

Design and analysis of ZVZCS converter with active clamping

Mr.J.Sivavara Prasad 1 Dr.Ch.Sai babu 2 Dr.Y.P.Obelesh 3

1. Mr. J.Sivavara Prasad, Asso. Professor in Dept. of EEE, Aditya College of Engg., Madanapalle 2. Dr.Ch. Sai babu, Professor in Dept. of EEE, JNTU Kakinada. 3. Dr.Y.P.Obelesh, HOD in Dept. of EEE, Lakkireddy Balreddy Institute of Technology, Mylavaram.

Abstract-The design and analysis of ZVZCS converter with active clamping is proposed. By adding a secondary active clamp and controlling the clamp switch moderately, ZVS (for leading leg switches) and ZCS (for lagging leg switches) are achieved without any lossy components, the reverse avalanche break down of leading-leg IGHTs or the saturable reactor in the primary. Many advantages including simple circuit topology, high efficiency, and low cost make the new converter attractive for high voltage and high power (> 10 kW) applications. The principle of operation is explained and analyzed. The features and design considerations of the new converter are also illustrated and verified on an 1.8 kW, 100 kHz IGBT based experimental circuit. 1.INTRODUCTION IGBTs are widely used in the switching power conversion applications because of their distinctive advantages such as easiness in drive and high frequency switching capability. The performance of IGBTs has been continuously improved and the latest IGBTs can be operated at 10-20 kHz

Available online @ www.ijcscn.com

without including any snubber circuit. More over, IGBTs are replacing MOSFETs for the several or several tens kilo-watts power range applications since IGBTs can handle higher voltage and power with higher power density and lower cost comparing to MOSFETs. The maximum operating frequency of IGBTs is limited to 20-30 kHz [ 11 because of their current tailing problem. To operate IGBTs at high switching frequencies, it is required to reduce the turn-off switching loss. ZVS with a substantial external capacitor or ZClS can be a solution. The ZCS, however, is deemed more effective since the minority carrier is swept out before turning off. ZVS-FB-PWM converters have received considerable attention in recent years. This converter is controlled by phase shifted PWM technique which enables the use of all parasitic elements in the bridge to provide ZVS conditions for the switches. Distinctive advantages including ZVS with no additional components and low device voltage/current stresses make it very attractive for high frequency, high-power applications where MOSFETs are predominantly used as the power

50

J.Sivavara Prasad et al, International Journal of Computer Science & Communication Networks,Vol 1(1),September-October 2011

switches. The IGBTs, however, are not suited for the ZVS-FB-PWM converter because the ZVS range is quite limited unless the leakage inductance is very large. In addition, several demerits such as duty cycle loss and parasitic ringing in the secondary limit the maximum power rating of the converter. To apply IGBTs for high frequency converter, a ZVZCSFB-PWM converter was presented. IGBTs with no anti parallel diodes are used for all primary switches. During freewheeling period, the primary current is reset by using reverse avalanche break down voltage of the leading leg IGBTs, which provides ZCS condition to lagging leg IGBTs. However, it has some drawbacks as follows: The stored energy in the leakage inductance is completely dissipated in the leading-leg IGBTs; The maximum controllable duty cycle is limited since the reverse avalanche breakdown voltage is low (1 5-30V) and fixed. Therefore, the overall efficiency will be deteriorated unless the leakage inductance is very low. Another approach for ZVZCS-FBPWM converter was presented. By utilizing dc blocking capacitor and adding a saturable inductor in the primary, the primary current during the freewheeling period is reset which provides ZCS condition to the lagging leg switches. Meanwhile, the leading leg switches are still operated with ZVS. The stored energy in the leakage inductance is recovered to the dc blocking capacitor and finally transferred to the load. By increasing the blocking capacitor voltage (i.e. by reducing capacitance), wide duty cycle control range is attainable even when the leakage inductance is relatively large. This converter can be effectively applied to several kW power range applications. Some demerits including loss in saturable inductor and

Available online @ www.ijcscn.com

its cooling problem hinder further increase of power level above 10 kW. This paper proposes a novel ZVZCS-FB-PWM converter to improve the performance of the previously presented ZVZCS-FB-PWM converters. The ZVS mechanism of leading leg switches is the same as that of the converters [2-5,8]. The ZCS of lagging leg switches, however, are achieved by adding an active clamp in the secondary rectifier and controlling it moderately. No lossy components are added to achieve ZVZCS operation and the duty cycle loss is almost negligible. So, the new converter overcomes most of the limitations of the soft switching full bridge PWM converters, which makes the new converter very attractive for high voltage, high power (> 10 kW) applications where IGBTs are predominantly used as the power switches. The basic operation and features of the proposed converter are described. A 1.8 kW, 100 kHz prototype has been built using IGBTs (a MOSFET for the clamp switch) and tested to verify the principle of operation.

2. Operation and Analysis

51

J.Sivavara Prasad et al, International Journal of Computer Science & Communication Networks,Vol 1(1),September-October 2011

The basic structure of the proposed ZVZCS-FBPWM converter is the same as that of the ZVS-FB-PWM converter with the active clamp in the secondary side. The control of the primary switches is also the same, phase shift PWM control. The control of active clamp is a little different, which will be explained later in this section. To illustrate steady state operation, several assumptions are made as follows: . All components are ideal, . Output filter inductor is large enough to be treated as a constant current source during a switching period,, . Clamp capacitor is large enough to be treated as a constant voltage source During a switching period. The new converter has eight operating modes within each operating half-cycle. The equivalent circuits and operation waveforms are shown in Figs. 2 and 3, respectively. Mode 1: S1 and S2 are conducting and the input power is delivered to the output. At the beginning of this mode, the rectifier voltage which was increasing is clamped by Vc through the body diode of Sc. The stored energy in the leakage inductance which is generated by the resonance between the leakage inductance and parasitic capacitance is recovered to the clamp capacitor. So, the primary current is decreased as follows:

capacitance and reverse recovery time of the rectifier diodes. Mode 2: The body diode of Sc blocks and the secondary rectifier voltage becomes

Vrec =n VS

(3)

The S1 and S2 are still on and the powering mode is sustained during this mode. Mode 3: According to the given duty cycle, S1 is turned off and then, the reflected load current to the primary charges C1 and discharges C3. The switch voltage increases linearly as follows:

Vsl (t)= {(n IO)/(C1+ C3)}.t (4)

The turn-off process of S1 is low loss if the external capacitor is large enough to hold the switch voltage at near zero during the switch turn-off time. During this mode, the secondary rectifier voltage is also decreased with almost same rate. At the end of this mode, D3 is turned on. Mode 4: After D3 starts conducting, S3 can be turned on with ZVS. The load current freewheels through the primary side, D3 and S2. To reset the primary current, the clamp switch is turned on and then, the rectifier voltage becomes Vc. This voltage is applied to the leakage inductance and the primary current is linearly decreased with the slope of Vc/n Ll k k and IC is linearly increased. The primary current reaches zero at the end of this mode. Mode 5: The rectifier diodes are turned off since the primary current is zero and Sc is still on. During this mode, the primary current sustained at zero and Cc supplies whole load current.

52

IP (t)= (1/Ll k ){Vs-(Vc /n)}.t

(1)

where n is transformer turn ratio and the clamp capacitor current can be expressed as follows: IC= (IP /n)-IO (2) This mode ends when I, becomes zero. The duration of this mode depends on the leakage inductance and the junction

Available online @ www.ijcscn.com

J.Sivavara Prasad et al, International Journal of Computer Science & Communication Networks,Vol 1(1),September-October 2011

Mode 6: The Sc is turned off and then the rectifier voltage is dropped to zero. The load current freewheels through the rectifier itself. No current flows through the primary.

Mode 7: At the end of freewheeling mode, S2 can be turned off with ZCS. No tail current exists since all minority carriers are eliminated by recombination. This mode is dead time between S2 and S4. Mode 8: To terminate from freewheeling mode, S4 is turned on. This turn-on process is also ZCS since the primary current can not be changed abruptly and no diode reverse recovery is involved. The primary current Ip is linearly increased with the slop of Vs/ Ll k .The rectifier voltage is still zero. This is the end of an operating half-cycle. 3. Features of the Proposed Converter 3. 1. Eflective Soft Switching (ZVZCS) Soft switching mechanism (ZVS for leading-leg switches and ZCS for lagging leg switches) of the proposed converter has exactly the same as those of the ZVZCS converters. The converters use lossy components to achieve ZCS of

Available online @ www.ijcscn.com 53

J.Sivavara Prasad et al, International Journal of Computer Science & Communication Networks,Vol 1(1),September-October 2011

lagging leg switches. The stored energy in the leakage inductance is completely dissipated in the leading-leg IGBTs during freewheeling mode or there exists the core loss of saturable reactor. In addition, additional losses exists in the clamp resistor for both converters if the passive clamp circuit is used to clamp the secondary rectifier voltage. Therefore, both converters have limited power range (several kW). In the proposed converter, however, ZCS of lagging-leg switches is achieved more efficiently by modifying control of the active clamp. No lossy components are involved in achieving ZCS and no parasitic ringing is generated in the secondary rectifier. So, the proposed converter can handle higher power level (> 10 kW). The ZCS of lagging-leg switches is achieved with whole load ranges and the ZVS of the leading-leg switches is also achieved with wide load range. 3. 2..More Reduced Conduction Loss The primary voltage, current, and the secondary voltage of the proposed converter are compared to those of the ZVS , and the ZVZCS converters as shown in Fig. 4. The ZVS converter has considerable duty cycle loss since large leakage inductance is required to obtain wide ZVS range. The ZVZCS converters improves the overall efficiency by removing the freewheeling current in the primary and reducing the duty cycle loss. The maximum duty cycle, however, is limited by the primary current reset-time, Treset which is determined by the applied voltage to the leakage inductance VL l k during freewheeling period as follows: TRESET = Ll k{(n IO)/ VL l k } (5) The Treset of the converters is considerably large since low voltage (several tens volts) is applied to the

Available online @ www.ijcscn.com

leakage inductance, which affects the overall efficiency as same as the duty cycle loss. In the proposed ZVZCS converter, however, a small Treset achieved since the high voltage (VC/n) is applied to the leakage inductance. So, the overall efficiency of the proposed converter is improved due to low duty cycle loss as well as small Treset.

54

J.Sivavara Prasad et al, International Journal of Computer Science & Communication Networks,Vol 1(1),September-October 2011

Available online @ www.ijcscn.com

55

J.Sivavara Prasad et al, International Journal of Computer Science & Communication Networks,Vol 1(1),September-October 2011

3. 3.Duty Cycle Boost Effect The secondary rectifier duty cycle is usually lower than that of the primary because of the duty cycle loss. In the proposed converter, however, the rectifier duty cycle can be higher than that of the primary as shown in Fig. 5. This phenomenon is named as duty cycle boost effect. The duty cycle boost effect is caused by the operation of the active clamp from the beginning of freewheeling period to provide ZCS condition to the lagging-leg switches. This means that the stored energy in the leakage inductance is recovered to the clamp capacitor and finally transferred to the load by means of the duty cycle boost effect. This feature is very important for the ZVZCS converters which use IGBTs for main switches. The primary duty cycle can not be increased to near unity since the minimum dead-time is required to achieve a complete ZCS turn-off of the lagging-leg switches which is the time for minority carrier recombination of IGBTs. The effective duty cycle of the proposed converter, however, can be increased to near unity due to the duty cycle boost effect. The effective duty cycle of the proposed converter can be expressed as follows: (6) Deff =Dprim D +Dboost where D is the duty cycle loss. The Dboost is determined directly by the turn-on time of the clamp switch. The duty cycle boost effect also helps to improve the overall efficiency. 4. Design Considerations 4.1. Decision of Dead Times An appropriate dead time is required for both leading and lagging-leg switches to achieve maximum performance. Dead time for leading-leg switches: The dead time for leading-leg switches is determined by two factors, the ZVS range and the maximum duty

Available online @ www.ijcscn.com

cycle of the primary side. The minimum dead time is determined by ZVS range as follows: Td, lead (C1+C3){Vs/ IO,ZVS} (7) where IO,ZVS is given ZVS range as one of design parameters. The maximum dead time is limited by the maximum duty cycle of the primary side. Dead time for lagging-leg switches: The minimum dead time of lagging-leg switches is determined by the time TZCS to achieve a complete ZCS of the lagging-leg switches as follows: Td, lag TZCS (8) where the TZCS is the minority carrier recombination time of waveforms. IGBTs. The maximum dead time is also limited by the maximum duty cycle of the primary side. 4.2. Decision of Dead Times The illustrative waveforms of the secondary rectifier voltage and the clamp capacitor current according to the turn-on time of Sc are depicted in Fig. 6. To achieve a complete ZCS of lagging-leg switches, the primary current should be reset. The required turn-on time Tsc of Sc is obtained as follows:

Tsc {(n2 Ll k)/Vc} Io, max

(9)

The clamp capacitor current is abruptly increased according to the on-time Tsc as shown in Fig. 6. Therefore, the Tsc need to be kept as small as possible to reduce the conduction loss of clamp switch and in turn allow use of a small switch for Sc. The clamp capacitor voltage is regulated automatically as shown in Fig. 6. 4.3. Active Clamp Circuit for CenterTapped Transformer

56

J.Sivavara Prasad et al, International Journal of Computer Science & Communication Networks,Vol 1(1),September-October 2011

The proposed ZVZCS power conversion technique can also be applied for the center-tapped transformer as shown in Fig. 7. The basic operation principle is exactly the same as that of the simple output transformer except diode voltage.

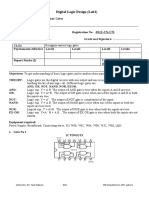

5. Experimental Results An 1.8 kW, 100 kHz prototype of the proposed ZVZCS-FB-PWM converter has been built and tested to verify the principle of operation. Fig. 8 shows the experimental circuit with the part numbers and the circuit parameters. The transformer is built using an EE/55/55 core with the turns ratio of Np:Ns=28:5. The leakage inductance measured at the switching frequency is 3.6 uH. IRGPC40UD2 IGBTs are used for the primary switches. The recommended switching frequency for the IRGPC40UD2 provided by the data sheet is only 10-20 kHz. As will be shown, these IGBTs can be operated at 100 kHz without any detrimental effects on the efficiency. Fig. 9 shows the waveforms of the primary voltage and current and the secondary rectifier voltage at full load (nominal duty cycle of 0.78) and Fig. 10 shows the extended waveforms at the switching transitions of leading and lagging legs. All waveforms are well matched with the expected ones. The primary voltage shows slow down slope due to the external capacitors added to the leading-leg switches and fast up slope. The duty cycle loss is about 0.lus. The primary current is quickly reset right after the primary voltage is dropped to zero and sustained during the freewheeling period. The primary current reset time is only 0.15 us. The turn-on time of the active switch is about 0.35 us. Fig. 11 shows the extended switching waveforms of leading-leg switches. It can be seen that the anti-parallel diode current flows for short time and stays zero and thus, a complete ZVS turn-on is achieved. The tail current is seen but the turn-off switching loss is remarkably

Available online @ www.ijcscn.com

57

J.Sivavara Prasad et al, International Journal of Computer Science & Communication Networks,Vol 1(1),September-October 2011

reduced comparing to hard switching since the rising slope of the switch voltage is slow. The ZVS range for the leading-leg switches is about 20 % of full load. Fig. 12 shows the extended switching waveforms of lagging-leg switches. It can be seen that a complete ZCS turn-off is achieved since the primary current is zero during the whole freewheeling period and the turn-on process of the other switch is almost ZCS. Small pulse current during turn-on transition is the charging current of the switch output capacitor. Fig. 13 shows the waveforms of the secondary active clamp. The clamp switch is turned-on for very short time comparing 1.0 the operating period (7 %). The rectifier voltage waveform shows a little noisy since the clamp switch operates under hard switching. The clamp capacitor current waveform is the same as the expected. The maximum measured efficiency is about 94 %.

Available online @ www.ijcscn.com

58

J.Sivavara Prasad et al, International Journal of Computer Science & Communication Networks,Vol 1(1),September-October 2011

is presented. The operation, features and design considerations are illustrated and verified by the experimental results on a 1.8 kW, 100 kHz IGBT based. It is shown that ZVS for leading leg switches and ZCS for lagging leg switches are achieved by the help of the active clamp. The efficiency attained at full load was about 94 %. The proposed converter has distinctive advantages over the previously presented ZVZCS converters as follows: a) ZVS and ZCS without any lossy components; b) wide ZVS and ZCS range; c) high duty cycle is attainable; d) more reduced conduction loss in the primary; e) no severe parasitic ringing. Many advantages of the new circuit makes the proposed converter very promising for high voltage (400-800 V), high power (> 10 kW) applications with high power density. REFERENCES [I] C.M.C. Duarte and I. Barbi, "A Family of ZVS-PWM Active-Clamping DC-to-DC Converters: Synthesis, Analysis, and Experimentation", in INTELEC, 1995 Proceedings, pp. 502509. [ 2] "IGBT Designer's Manual," International Rectifier, El Segundo, CA, 1994. [2] J. A. Sabate, V. Vlatkovic, R. B. Ridley, F. C. Lee, and B.H. Cho, "Design considerations for high-voltage high power full-bridge zero-voltage-switched PWM converter," IEEE APEC Rec. 1990, pp. 275284. [3] J. A. Sabate, V. Vlatkovic, R. B. Ridley, F. C. Lee, and B. H. Cho, "High voltage high power ZVS full bridge

59

6. CONCLUSIONS A novel ZVZCS-FB-PWh4 converter using secondary active clamp

Available online @ www.ijcscn.com

J.Sivavara Prasad et al, International Journal of Computer Science & Communication Networks,Vol 1(1),September-October 2011

PWM converter employing active snubber," IEEE APEC Rec. [4] R. Redl, N. 0. Sokal, and L. Balogh, "A novel soft switching full bridge dc/dc converter: analysis, design considerations, and experimental results at 1 SKW, lOOKHz," IEEE PESC Rec. 1990, pp. 162-172. [SI A. W. Lotfi, Q. Chen, and F. C. Lee, "A nonlinear optimization tool for the full bridge zero-voltage switched PWM dc/dc converter," IEEE APEC Rec. 1992, [6] G. Hua, E. X. Yang, Y. Jiang, and F. C. Lee, "Novel zero current- transition PWM converters", IEEE PESC Rec. [7] K. Chen and T. A. Stuart, "1.6KW, 1lOkhz dc/dc converter optimized for IGBTs", IEEE Trans. on Power Electronics, Vol. 8, No. 1, pp.18-25, 1993. [8] J. G. Cho, J. Sabate, G. Hua, and F. C. Lee, "Zero voltage and zero current switching full bridge PWM converter for high power applications," IEEE PESC Rec. 1994, pp. 1991, pp. 158-163. pp. 1301-1309. 1993, pp. 538-544. 102- 108. [9] "IGBT Designer's Manual," International Rectifier, El Segundo, CA, 1994.

Available online @ www.ijcscn.com

60

Das könnte Ihnen auch gefallen

- Comparison Between LCC and VSCDokument5 SeitenComparison Between LCC and VSCijsretNoch keine Bewertungen

- 160.54-m1 Micro Board DataDokument24 Seiten160.54-m1 Micro Board Dataazam chohhan100% (1)

- SnapLogic User GuideDokument136 SeitenSnapLogic User GuideranjankrishnaNoch keine Bewertungen

- Salwico Cargo Addressable Installation Manual EDokument74 SeitenSalwico Cargo Addressable Installation Manual EAshish DharjiyaNoch keine Bewertungen

- A Simple Structure of Zero-Voltage Switching Zero Current Switching Buck ConverterDokument9 SeitenA Simple Structure of Zero-Voltage Switching Zero Current Switching Buck Convertersang young soNoch keine Bewertungen

- Zero-Voltage and Zero-Current Switching FullDokument8 SeitenZero-Voltage and Zero-Current Switching FullFrank GonzalezNoch keine Bewertungen

- An 7517Dokument9 SeitenAn 7517MallickarjunaNoch keine Bewertungen

- A New Soft-Switching Technique For Buck, BoostDokument8 SeitenA New Soft-Switching Technique For Buck, BoostVisu TamilNoch keine Bewertungen

- High-Efficiency Active-Clamp Forward Converter With Transient Current Build-Up (TCB) ZVS TechniqueDokument9 SeitenHigh-Efficiency Active-Clamp Forward Converter With Transient Current Build-Up (TCB) ZVS TechniquekerblaNoch keine Bewertungen

- An Improved Soft-Switching Buck Converter With Coupled InductorDokument7 SeitenAn Improved Soft-Switching Buck Converter With Coupled InductorSanthosh GuduruNoch keine Bewertungen

- 6high Power Full-Bridge DC-DC Converter Using A Center-Tapped Transformer and A Full-Wave Type Rectifier PDFDokument12 Seiten6high Power Full-Bridge DC-DC Converter Using A Center-Tapped Transformer and A Full-Wave Type Rectifier PDFmajidNoch keine Bewertungen

- Wide Range Soft Switching PWM Three-Level DC-DC Converters Suitable For Industrial ApplicationsDokument14 SeitenWide Range Soft Switching PWM Three-Level DC-DC Converters Suitable For Industrial Applicationsstrngr06Noch keine Bewertungen

- J'14 - Analysis, Design and Performance of A Soft-Switching Single-Phase InverterDokument12 SeitenJ'14 - Analysis, Design and Performance of A Soft-Switching Single-Phase Inverter閒雲野鶴Noch keine Bewertungen

- Design and Application For PV Generation System Using A Soft-Switching Boost Converter With SARCDokument13 SeitenDesign and Application For PV Generation System Using A Soft-Switching Boost Converter With SARCIJERDNoch keine Bewertungen

- Family of Soft-Switching PWMDokument7 SeitenFamily of Soft-Switching PWMMohan KrishnaNoch keine Bewertungen

- A Zero-Voltage and Zero-Current Switching Full Bridge DC-DC Converter With Transformer IsolationDokument8 SeitenA Zero-Voltage and Zero-Current Switching Full Bridge DC-DC Converter With Transformer IsolationJie99Noch keine Bewertungen

- High Efficiency Bi-Directional Converter For Flywheel Energy Storage ApplicationsDokument10 SeitenHigh Efficiency Bi-Directional Converter For Flywheel Energy Storage Applicationsmridul mpNoch keine Bewertungen

- Comparison and Simulation of Full Bridge and LCL-T Buck DC-DC Converter SystemsDokument5 SeitenComparison and Simulation of Full Bridge and LCL-T Buck DC-DC Converter SystemsKrishnaveni Subramani SNoch keine Bewertungen

- Fuzzy Logic Controller Based Implemented ZVT-ZCT PWM Boost Converter Using Renewable Energy SourceDokument6 SeitenFuzzy Logic Controller Based Implemented ZVT-ZCT PWM Boost Converter Using Renewable Energy SourceGRD JournalsNoch keine Bewertungen

- High-Power Density Design of A Soft-Switching High-Power Bidirectional DC-DC ConverterDokument9 SeitenHigh-Power Density Design of A Soft-Switching High-Power Bidirectional DC-DC Convertermurthy237Noch keine Bewertungen

- An Improved ZVT-ZCT PWM DC-DC Boost Converter With Increased EfficiencyDokument8 SeitenAn Improved ZVT-ZCT PWM DC-DC Boost Converter With Increased EfficiencyDeepak NayakNoch keine Bewertungen

- Topic Assignment14Dokument6 SeitenTopic Assignment14cuongakamarineNoch keine Bewertungen

- ZVSDokument28 SeitenZVS12BACAUNoch keine Bewertungen

- ZvsDokument29 SeitenZvsSandy RonaldoNoch keine Bewertungen

- Non Isolated Bidirectional DC DC ConverterDokument6 SeitenNon Isolated Bidirectional DC DC ConverterAnuja VargheseNoch keine Bewertungen

- Analysis, Design and Implementation of Zero-Current-Switching Resonant Converter DC-DC Buck ConverterDokument12 SeitenAnalysis, Design and Implementation of Zero-Current-Switching Resonant Converter DC-DC Buck Converterdaber_huny20Noch keine Bewertungen

- New Zero Voltage Switching Bridgeless PFDokument10 SeitenNew Zero Voltage Switching Bridgeless PFHaijun GuNoch keine Bewertungen

- ZVS Boost Converter With A Flyback Snubber CircuitDokument8 SeitenZVS Boost Converter With A Flyback Snubber Circuitmishranamit2211Noch keine Bewertungen

- Switched Capacitor FilterDokument20 SeitenSwitched Capacitor FilterArijit ShawNoch keine Bewertungen

- Improved Step Down Conversion in Interleaved Buck Converter and Low Switching LossesDokument10 SeitenImproved Step Down Conversion in Interleaved Buck Converter and Low Switching LossesinventyNoch keine Bewertungen

- Performance of A Current-Fed Soft Switched Full-Bridge Boost Double Stage Converter Using ZVS PWMDokument8 SeitenPerformance of A Current-Fed Soft Switched Full-Bridge Boost Double Stage Converter Using ZVS PWMiajerNoch keine Bewertungen

- Ee 328 Lecture 1Dokument40 SeitenEe 328 Lecture 1Hasan Hatice IlcalıNoch keine Bewertungen

- Lin 2013Dokument12 SeitenLin 2013Pavan Singh TomarNoch keine Bewertungen

- Four Novel PWM Shoot-Through Control Methods For Impedance Source DC-DC ConvertersDokument10 SeitenFour Novel PWM Shoot-Through Control Methods For Impedance Source DC-DC ConvertersUtkarsh PrakashNoch keine Bewertungen

- Two-Stage H-Bridge Transformer Coupled DC-DC Converter With Zero Voltage SwitchingDokument8 SeitenTwo-Stage H-Bridge Transformer Coupled DC-DC Converter With Zero Voltage SwitchingRakeshconclaveNoch keine Bewertungen

- Single Stage Inverter Topology For Renewable Resources: Jeena Mary Abraham, M.S.P. Subathra, Senraj. RDokument5 SeitenSingle Stage Inverter Topology For Renewable Resources: Jeena Mary Abraham, M.S.P. Subathra, Senraj. RskrtamilNoch keine Bewertungen

- A Novel Three-Level DC-DC Converter With Load Adaptive ZVS Auxiliary CircuitDokument6 SeitenA Novel Three-Level DC-DC Converter With Load Adaptive ZVS Auxiliary Circuitdsshin_psNoch keine Bewertungen

- Design and Implementation of ZCS BUCK CONVERTERDokument51 SeitenDesign and Implementation of ZCS BUCK CONVERTERAriful Haque100% (1)

- Implementation of ZVS-ZCS Combined Snubber NetworkDokument6 SeitenImplementation of ZVS-ZCS Combined Snubber NetworkYuiophjklNoch keine Bewertungen

- EEE - IJEEE - Analysis, Design and - Irfan Jamil - China-PakistanDokument12 SeitenEEE - IJEEE - Analysis, Design and - Irfan Jamil - China-Pakistaniaset123Noch keine Bewertungen

- Heavy Load Light Load Conversion ReportDokument41 SeitenHeavy Load Light Load Conversion ReportSanjivee SachinNoch keine Bewertungen

- High-Efficient Multilevel Half-Bridge ConverterDokument9 SeitenHigh-Efficient Multilevel Half-Bridge Converter'Mantas PuhtėjavasNoch keine Bewertungen

- SRR Engineering College: Design and Implementation of Current Self-Balance Mechanism in Multiphase Buck ConverterDokument26 SeitenSRR Engineering College: Design and Implementation of Current Self-Balance Mechanism in Multiphase Buck ConverterSurekha AthikesavanNoch keine Bewertungen

- Performance Enhancement of A Novel Interleaved Boost Converter by Using A Soft-Switching TechniqueDokument10 SeitenPerformance Enhancement of A Novel Interleaved Boost Converter by Using A Soft-Switching TechniqueHaijun GuNoch keine Bewertungen

- I J Seas 20160123Dokument10 SeitenI J Seas 20160123Eugin RajNoch keine Bewertungen

- Novel Sngle Phase ZCSDokument7 SeitenNovel Sngle Phase ZCSAntonio Hadade NetoNoch keine Bewertungen

- Quasi-Parallel Resonant DC Link Inverter With Improved PWM CapabilityDokument2 SeitenQuasi-Parallel Resonant DC Link Inverter With Improved PWM CapabilityfatyfroisNoch keine Bewertungen

- Zero Voltage Switching Resonant Power Devices by Bill AndrecakDokument28 SeitenZero Voltage Switching Resonant Power Devices by Bill AndrecakRekhamtrNoch keine Bewertungen

- DC-DC Converter: Four Switches V V 2, Capacitive Turn-Off Snubbing, ZV Turn-OnDokument10 SeitenDC-DC Converter: Four Switches V V 2, Capacitive Turn-Off Snubbing, ZV Turn-OnRomitan AlexandraNoch keine Bewertungen

- Theory of Switched Mode Power SupplyDokument21 SeitenTheory of Switched Mode Power Supplyseahate100% (1)

- SST ReportDokument4 SeitenSST ReportkspariharNoch keine Bewertungen

- Coping W Poor Dynamic Performance of Super-Junction MOSFET Body Diodes PDFDokument6 SeitenCoping W Poor Dynamic Performance of Super-Junction MOSFET Body Diodes PDFefremofeNoch keine Bewertungen

- High Power Factor Soft SwitchedDokument7 SeitenHigh Power Factor Soft SwitchedMohan KrishnaNoch keine Bewertungen

- A New Full Bridge DC/DC Converter Topology With ZVZCS FeaturesDokument9 SeitenA New Full Bridge DC/DC Converter Topology With ZVZCS FeaturesAshok KumarNoch keine Bewertungen

- Boost Inverter Circuit With A Coupled Inductor Using Renewable Energy SourceDokument8 SeitenBoost Inverter Circuit With A Coupled Inductor Using Renewable Energy SourceAnonymous qSgOUqNoch keine Bewertungen

- Implementation and Simulation of Half Bridge Series Resonant Inverter in Zero Voltage SwitchingDokument5 SeitenImplementation and Simulation of Half Bridge Series Resonant Inverter in Zero Voltage Switchingwhite_lonelinessNoch keine Bewertungen

- Power Electronics Lab Simulation Project ReportDokument5 SeitenPower Electronics Lab Simulation Project ReportMaha RaufNoch keine Bewertungen

- Transformer Based Resonant DC Inverter For Brushless DC Motor Drive SystemDokument7 SeitenTransformer Based Resonant DC Inverter For Brushless DC Motor Drive SystemStudents Xerox ChidambaramNoch keine Bewertungen

- Proposal of A Soft-Switching Single-PhaseDokument7 SeitenProposal of A Soft-Switching Single-Phaseayie55Noch keine Bewertungen

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Bewertung: 2.5 von 5 Sternen2.5/5 (3)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Noch keine Bewertungen

- Power Electronics Applied to Industrial Systems and Transports, Volume 3: Switching Power SuppliesVon EverandPower Electronics Applied to Industrial Systems and Transports, Volume 3: Switching Power SuppliesNoch keine Bewertungen

- Efficient and Secure Biometric Image Stegnography Using Discrete Wavelet TransformDokument4 SeitenEfficient and Secure Biometric Image Stegnography Using Discrete Wavelet TransformMohit SnggNoch keine Bewertungen

- Battle Field Speech Enhancement Using An Efficient Unbiased Adaptive Filtering TechniqueDokument5 SeitenBattle Field Speech Enhancement Using An Efficient Unbiased Adaptive Filtering Techniqueeditor9891Noch keine Bewertungen

- Reduction of THD in Power Systems Using STATCOMDokument5 SeitenReduction of THD in Power Systems Using STATCOMeditor9891Noch keine Bewertungen

- Modeling and Simulation of PV Array and Its Performance Enhancement Using MPPT (P&O) TechniqueDokument8 SeitenModeling and Simulation of PV Array and Its Performance Enhancement Using MPPT (P&O) Techniqueeditor9891Noch keine Bewertungen

- HP LJ P2035 P2055 PartslistDokument21 SeitenHP LJ P2035 P2055 PartslistИгорь ТимошевскийNoch keine Bewertungen

- Siemens 4wire AnalogDokument24 SeitenSiemens 4wire AnalogIvan BevandaNoch keine Bewertungen

- Cripto LibDokument374 SeitenCripto LibAlexandre SantosNoch keine Bewertungen

- Lect. 9: Multithreading: - Dynamic Out-Of-Order Scheduling - PrefetchingDokument12 SeitenLect. 9: Multithreading: - Dynamic Out-Of-Order Scheduling - PrefetchingbalramkinageNoch keine Bewertungen

- ABREVIAÇÕES-Design Terms AbbreviationsDokument18 SeitenABREVIAÇÕES-Design Terms AbbreviationsPedro DutraNoch keine Bewertungen

- HandwritingDokument21 SeitenHandwritingGabi NesNoch keine Bewertungen

- HDCP On HDMI Test Application and Product Capability For ATC Rev SDokument17 SeitenHDCP On HDMI Test Application and Product Capability For ATC Rev SmateusgbritoNoch keine Bewertungen

- CASE Computer-Aided Software Engineering ASSIGNMENTDokument5 SeitenCASE Computer-Aided Software Engineering ASSIGNMENTZubaidahNoch keine Bewertungen

- Engineering Consumable Stock Card SampleDokument4 SeitenEngineering Consumable Stock Card SampleMyla Mech EngrNoch keine Bewertungen

- iRC1021 - iRC1021i Basic Operation Guide PDFDokument494 SeiteniRC1021 - iRC1021i Basic Operation Guide PDFbisocpaulNoch keine Bewertungen

- Revision Sheet Class 4Dokument5 SeitenRevision Sheet Class 4PPNoch keine Bewertungen

- COD - Unit-3 - N - 4 - PPT AJAY KumarDokument93 SeitenCOD - Unit-3 - N - 4 - PPT AJAY KumarAjay KumarNoch keine Bewertungen

- JBC CompactDokument3 SeitenJBC CompactJuan Dila CruzNoch keine Bewertungen

- Design of Analog & Mixed Mode Vlsi Circuits 6 (Compatibility Mode)Dokument44 SeitenDesign of Analog & Mixed Mode Vlsi Circuits 6 (Compatibility Mode)rahul_agarwal_15Noch keine Bewertungen

- Manual SKF TK Sa 40 PDFDokument432 SeitenManual SKF TK Sa 40 PDFDouglas CarrascoNoch keine Bewertungen

- DLD Lab 1Dokument5 SeitenDLD Lab 1tm tigerNoch keine Bewertungen

- MES Module 4Dokument27 SeitenMES Module 4Suraj S NeelagarNoch keine Bewertungen

- 5 Superhero Queries SQL Server 2008Dokument4 Seiten5 Superhero Queries SQL Server 2008Krishnakant joshiNoch keine Bewertungen

- Chapter 03 ARM MPU SubsystemDokument12 SeitenChapter 03 ARM MPU SubsystemkzillaNoch keine Bewertungen

- Media Tools ManualDokument70 SeitenMedia Tools Manualalextrek01Noch keine Bewertungen

- Arduino v2Dokument68 SeitenArduino v2sadekNoch keine Bewertungen

- Testing ToolsDokument5 SeitenTesting ToolsbhpNoch keine Bewertungen

- He Xi DecimalDokument147 SeitenHe Xi DecimalJoeandLaura Walk To VegasNoch keine Bewertungen

- CompressionDokument46 SeitenCompressionSujay KumarNoch keine Bewertungen

- DNS-320 Datasheet US PDFDokument3 SeitenDNS-320 Datasheet US PDFdio39saiNoch keine Bewertungen

- XBKPDokument88 SeitenXBKPMark LettermanNoch keine Bewertungen

- Harmonic and Transient Overvoltage Analysis in Arc Furnace Power SystemsDokument7 SeitenHarmonic and Transient Overvoltage Analysis in Arc Furnace Power SystemsElafanNoch keine Bewertungen