Beruflich Dokumente

Kultur Dokumente

RFG50N06, RFP50N06, RF1S50N06SM: 50A, 60V, 0.022 Ohm, N-Channel Power Mosfets Features

Hochgeladen von

Ana Beronica FabriniOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

RFG50N06, RFP50N06, RF1S50N06SM: 50A, 60V, 0.022 Ohm, N-Channel Power Mosfets Features

Hochgeladen von

Ana Beronica FabriniCopyright:

Verfügbare Formate

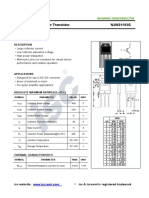

RFG50N06, RFP50N06, RF1S50N06SM

Data Sheet July 1999 File Number

3575.4

50A, 60V, 0.022 Ohm, N-Channel Power MOSFETs

These N-Channel power MOSFETs are manufactured using the MegaFET process. This process, which uses feature sizes approaching those of LSI integrated circuits gives optimum utilization of silicon, resulting in outstanding performance. They were designed for use in applications such as switching regulators, switching converters, motor drivers, and relay drivers. These transistors can be operated directly from integrated circuits. Formerly developmental type TA49018.

Features

50A, 60V rDS(ON) = 0.022 Temperature Compensating PSPICE Model Peak Current vs Pulse Width Curve UIS Rating Curve 175oC Operating Temperature

Symbol

D

Ordering Information

PART NUMBER RFG50N06 RFP50N06 RF1S50N06SM PACKAGE TO-247 TO-220AB TO-263AB BRAND RFG50N06 RFP50N06 F1S50N06

S G

NOTE: When ordering, use the entire part number. Add the suffix, 9A, to obtain the TO-263AB variant in tape and reel, i.e. RF1S50N06SM9A.

Packaging

JEDEC STYLE TO-247

SOURCE DRAIN GATE DRAIN (BOTTOM SIDE METAL) DRAIN (FLANGE)

JEDEC TO-220AB

SOURCE DRAIN GATE

JEDEC TO-263AB

DRAIN (FLANGE) GATE SOURCE

4-467

CAUTION: These devices are sensitive to electrostatic discharge; follow proper ESD Handling Procedures. PSPICE is a registered trademark of MicroSim Corporation. http://www.intersil.com or 407-727-9207 | Copyright Intersil Corporation 1999

RFG50N06, RFP50N06, RF1S50N06SM

Absolute Maximum Ratings

TC = 25oC, Unless Otherwise Specied RFG50N06, RFP50N06 RF1S50N06SM 60 60 20 50 (Figure 5) (Figure 6, 14, 15) 131 0.877 -55 to 175 300 260 UNITS V V V A

Drain to Source Voltage (Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . VDSS Drain to Gate Voltage (RGS = 20k) (Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . VDGR Gate to Source Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . VGS Continuous Drain Current (Figure 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .ID Pulsed Drain Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . IDM Pulsed Avalanche Rating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . EAS Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . PD Linear Derating Factor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Operating and Storage Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . TJ, TSTG Maximum Temperature for Soldering Leads at 0.063in (1.6mm) from Case for 10s. . . . . . . . . . . . . . . . . . . . . . . . . . . . TL Package Body for 10s, see Techbrief 334 . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Tpkg

W W/oC oC

oC oC

CAUTION: Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specication is not implied.

NOTE: 1. TJ = 25oC to 150oC.

Electrical Specications

PARAMETER

TC = 25oC, Unless Otherwise Specied SYMBOL BVDSS VGS(TH) IDSS TEST CONDITIONS ID = 250A, VGS = 0V (Figure 11) VGS = VDS, ID = 250A (Figure 10) VDS = 60V, VGS = 0V VGS = 20V ID = 50A, VGS = 10V (Figures 9) VDD = 30V, ID = 50A RL = 0.6, VGS = 10V RGS = 3.6 (Figure 13) TC = 25oC TC = 150oC MIN 60 2 VGS = 0 to 20V VGS = 0 to 10V VGS = 0 to 2V VDD = 48V, ID = 50A, RL = 0.96 Ig(REF) = 1.45mA (Figure 13) (Figure 3) TO-247 TO-220, TO-263 TYP 12 55 37 13 125 67 3.7 2020 600 200 MAX 4 1 50 100 0.022 95 75 150 80 4.5 1.14 30 62 UNITS V V A A nA ns ns ns ns ns ns nC nC nC pF pF pF

oC/W oC/W oC/W

Drain to Source Breakdown Voltage Gate to Source Threshold Voltage Zero Gate Voltage Drain Current

Gate to Source Leakage Current Drain to Source On Resistance Turn-On Time Turn-On Delay Time Rise Time Turn-Off Delay Time Fall Time Turn-Off Time Total Gate Charge Gate Charge at 10V Threshold Gate Charge Input Capacitance Output Capacitance Reverse Transfer Capacitance Thermal Resistance Junction to Case Thermal Resistance Junction to Ambient

IGSS rDS(ON) tON td(ON) tr td(OFF) tf tOFF Qg(TOT) Qg(10) Qg(TH) CISS COSS CRSS RJC RJA

VDS = 25V, VGS = 0V f = 1MHz (Figure 12)

Source to Drain Diode Specications

PARAMETER Source to Drain Diode Voltage Reverse Recovery Time SYMBOL VSD trr ISD = 50A ISD = 50A, dISD/dt = 100A/s TEST CONDITIONS MIN TYP MAX 1.5 125 UNITS V ns

4-468

RFG50N06, RFP50N06, RF1S50N06SM Typical Performance Curves

1.2 POWER DISSIPATION MULTIPLIER 1.0 ID , DRAIN CURRENT (A) 0.8 0.6 0.4 0.2 0 0 25 50 75 100 125 TC , CASE TEMPERATURE (oC) 150 175

Unless Otherwise Specied

60 50 40 30 20 10 0 25 50 75 100 125 150 175 TC , CASE TEMPERATURE (oC)

FIGURE 1. NORMALIZED POWER DISSIPATION vs CASE TEMPERATURE

FIGURE 2. MAXIMUM CONTINUOUS DRAIN CURRENT vs CASE TEMPERATURE

2 1 THERMAL IMPEDANCE 0.5 0.2 0.1 0.1 0.05 0.02 0.01 SINGLE PULSE 0.01 -5 10 10-4 10-3 10-2 10-1 t1 , RECTANGULAR PULSE DURATION (s) t2 NOTES: DUTY FACTOR: D = t1/t2 PEAK TJ = PDM x ZJC x RJC + TC 100 101 t1 PDM

ZJC, NORMALIZED

FIGURE 3. NORMALIZED MAXIMUM TRANSIENT THERMAL IMPEDANCE

400

TJ = MAX RATED SINGLE PULSE TC = 25oC IDM , PEAK CURRENT (A)

103

FOR TEMPERATURES ABOVE 25oC DERATE PEAK CURRENT CAPABILITY AS FOLLOWS: VGS = 20V 175 T C I = I 25 ----------------------- 150

ID , DRAIN CURRENT (A)

100 100s 1ms 10 OPERATION IN THIS AREA MAY BE LIMITED BY rDS(ON) VDSS(MAX) = 60V 1 10 VDS , DRAIN TO SOURCE VOLTAGE (V) 10ms 100ms DC 100

VGS = 10V 102 TRANSCONDUCTANCE MAY LIMIT CURRENT IN THIS REGION 40 10-3 10-2 10-1 100 101 102 t, PULSE WIDTH (ms) 103 104 TC = 25oC

FIGURE 4. FORWARD BIAS SAFE OPERATING AREA

FIGURE 5. PEAK CURRENT CAPABILITY

4-469

RFG50N06, RFP50N06, RF1S50N06SM Typical Performance Curves

300 IAS, AVALANCHE CURRENT (A)

Unless Otherwise Specied (Continued)

125 VGS = 10V

STARTING TJ = 25oC

ID , DRAIN CURRENT (A)

100

100

VGS = 8V

PULSE DURATION = 80s DUTY CYCLE = 0.5% MAX TC = 25oC VGS = 7V

75

10

STARTING TJ = 150oC If R = 0 tAV = (L) (IAS) / (1.3 RATED BVDSS - VDD)

50

VGS = 6V VGS = 5V VGS = 4V

25

1 0.01

If R 0 tAV = (L/R) ln [(IAS*R) / (1.3 RATED BVDSS - VDD) + 1] 0.1 1 10

0 0 1.5 3.0 4.5 6.0 7.5 VDS , DRAIN TO SOURCE VOLTAGE (V)

tAV, TIME IN AVALANCHE (ms)

NOTE: Refer to Intersil Application Notes 9321 and 9322. FIGURE 6. UNCLAMPED INDUCTIVE SWITCHING CAPABILITY FIGURE 7. SATURATION CHARACTERISTICS

125

NORMALIZED DRAIN TO SOURCE ON RESISTANCE

ID, DRAIN CURRENT (A)

100

PULSE DURATION = 80s DUTY CYCLE = 0.5% MAX VDD = 15V

-55oC

25oC

2.5

2.0

PULSE DURATION = 80s DUTY CYCLE = 0.5% MAX VGS = 10V, ID = 50A

175oC 75

1.5

50

1.0

25

0.5

0 0 1 2 3 4 5 6 7 8 9 10 VGS , GATE TO SOURCE VOLTAGE (V)

0 -80

-40

40

80

120

160

200

TJ , JUNCTION TEMPERATURE (oC)

FIGURE 8. TRANSFER CHARACTERISTICS

FIGURE 9. NORMALIZED DRAIN TO SOURCE ON RESISTANCE vs JUNCTION TEMPERATURE

2.0 NORMALIZED DRAIN TO SOURCE BREAKDOWN VOLTAGE VGS = VDS, ID = 250A NORMALIZED GATE THRESHOLD VOLTAGE 1.5

2.0 ID = 250A 1.5

1.0

1.0

0.5

0.5

0 -80

-40

40

80

120

160

200

0 -80

-40

40

80

120

160

200

TJ , JUNCTION TEMPERATURE (oC)

TJ , JUNCTION TEMPERATURE (oC)

FIGURE 10. NORMALIZED GATE THRESHOLD VOLTAGE vs JUNCTION TEMPERATURE

FIGURE 11. NORMALIZED DRAIN TO SOURCE BREAKDOWN VOLTAGE vs JUNCTION TEMPERATURE

4-470

RFG50N06, RFP50N06, RF1S50N06SM Typical Performance Curves

4000 VDS , DRAIN TO SOURCE VOLTAGE (V) VGS = 0V, f = 1MHz CISS = CGS + CGD CRSS = CGD COSS = CDS + CGD CISS 2000

Unless Otherwise Specied (Continued)

60 VDD = BVDSS 45 VDD = BVDSS 7.5 10 VGS , GATE TO SOURCE VOLTAGE (V)

C, CAPACITANCE (pF)

3000

30 0.75 BVDSS 0.50 BVDSS 15 0.75 BVDSS 0.50 BVDSS

5.0

1000

COSS CRSS

0.25 BVDSS 0.25 BVDSS RL = 1.2 Ig(REF) = 1.45mA VGS = 10V 20 Ig(REF) Ig(ACT) t, TIME (s) 80 Ig(REF) Ig(ACT)

2.5

0 0 5 10 15 20 25 VDS , DRAIN TO SOURCE VOLTAGE (V)

NOTE: Refer to Intersil Application Notes AN7254 and AN7260. FIGURE 12. CAPACITANCE vs DRAIN TO SOURCE VOLTAGE FIGURE 13. NORMALIZED SWITCHING WAVEFORMS FOR CONSTANT GATE CURRENT

Test Circuits and Waveforms

VDS BVDSS L VARY tP TO OBTAIN REQUIRED PEAK IAS VGS DUT tP RG IAS VDD tP VDS VDD

0V

IAS 0.01

0 tAV

FIGURE 14. UNCLAMPED ENERGY TEST CIRCUIT

FIGURE 15. UNCLAMPED ENERGY WAVEFORMS

tON VDS VDS VGS RL

+

tOFF td(OFF) tr tf 90%

td(ON)

90%

DUT RGS VGS

VDD

10% 90%

10%

VGS 0 10%

50% PULSE WIDTH

50%

FIGURE 16. SWITCHING TIME TEST CIRCUIT

FIGURE 17. SWITCHING WAVEFORMS

4-471

RFG50N06, RFP50N06, RF1S50N06SM Test Circuits and Waveforms

VDS RL VDD VDS VGS = 20V VGS

+

(Continued)

Qg(TOT)

Qg(10) VDD VGS VGS = 2V 0 Qg(TH) Ig(REF) 0 VGS = 10V

DUT Ig(REF)

FIGURE 18. GATE CHARGE TEST CIRCUIT

FIGURE 19. GATE CHARGE WAVEFORMS

4-472

RFG50N06, RFP50N06, RF1S50N06SM PSPICE Electrical Model

.SUBCKT RFP50N06 2 1 3 REV 2/22/93

*NOM TEMP = 25oC

CA 12 8 3.68e-9 CB 15 14 3.625e-9 CIN 6 8 1.98e-9

5

DBODY 7 5 DBDMOD DBREAK 5 11DBKMOD DPLCAP 10 5 DPLCAPMOD EBREAK 11 7 17 18 64.59 EDS 14 8 5 8 1 EGS 13 8 6 8 1 ESG 6 10 6 8 1 EVTO 20 6 18 8 1 IT 8 17 1

10

ESG + GATE 1 LGATE 9 20 RGATE EVTO + 18 8 6 8

DPLCAP 16

RDRAIN DBREAK

DRAIN 2 LDRAIN

VTO

MOS2 21 MOS1 11 17 EBREAK 18 RSOURCE +

DBODY

RIN

CIN 8

7 LSOURCE 3 SOURCE 18 RVTO

S1A

S2A 14 13 S2B 13 CB 14 + 5 EDS 8 IT 15 17 RBREAK

LDRAIN 2 5 1e-9 LGATE 1 9 5.65e-9 LSOURCE 3 7 4.13e-9 MOS1 16 6 8 8 MOSMOD M=0.99 MOS2 16 21 8 8 MOSMOD M=0.01 RBREAK 17 18 RBKMOD 1 RDRAIN 5 16 RDSMOD 1e-4 RGATE 9 20 0.690 RIN 6 8 1e9 RSOURCE 8 7 RDSMOD 12e-3 RVTO 18 19 RVTOMOD 1 S1A 6 12 13 8 S1AMOD S1B 13 12 13 8 S1BMOD S2A 6 15 14 13 S2AMOD S2B 13 15 14 13 S2BMOD VBAT 8 19 DC 1 VTO 21 6 0.678

CA

12

13 8 S1B

19 VBAT +

+ EGS 6 - 8

.MODEL DBDMOD D (IS=9.85e-13 RS=4.91e-3 TRS1=2.07e-3 TRS2=2.51e-7 CJO=2.05e-9 TT=4.33e-8) .MODEL DBKMOD D (RS=1.98e-1 TRS1=2.35E-4 TRS2=-3.83e-6) .MODEL DPLCAPMOD D (CJO=1.42e-9 IS=1e-30 N=10) .MODEL MOSMOD NMOS (VTO=3.65 KP=35 IS=1e-30 N=10 TOX=1 L=1u W=1u) .MODEL RBKMOD RES (TC1=1.23e-3 TC2=-2.34e-7) .MODEL RDSMOD RES (TC1=5.01e-3 TC2=1.49e-5) .MODEL RVTOMOD RES (TC1=-5.03e-3 TC2=-5.16e-6) .MODEL S1AMOD VSWITCH (RON=1e-5 ROFF=0.1 VON=-6.75 VOFF=-2.5) .MODEL S1BMOD VSWITCH (RON=1e-5 ROFF=0.1 VON=-2.5 VOFF=-6.75) .MODEL S2AMOD VSWITCH (RON=1e-5 ROFF=0.1 VON=-2.7 VOFF=2.3) .MODEL S2BMOD VSWITCH (RON=1e-5 ROFF=0.1 VON=2.3 VOFF=-2.7) .ENDS NOTE: For further discussion of the PSPICE model consult A New PSPICE Sub-Circuit for the Power MOSFET Featuring Global Temperature Options; authors, William J. Hepp and C. Frank Wheatley.

4-473

RFG50N06, RFP50N06, RF1S50N06SM

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certication.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com

Sales Ofce Headquarters

NORTH AMERICA Intersil Corporation P. O. Box 883, Mail Stop 53-204 Melbourne, FL 32902 TEL: (407) 724-7000 FAX: (407) 724-7240 EUROPE Intersil SA Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium TEL: (32) 2.724.2111 FAX: (32) 2.724.22.05 ASIA Intersil (Taiwan) Ltd. 7F-6, No. 101 Fu Hsing North Road Taipei, Taiwan Republic of China TEL: (886) 2 2716 9310 FAX: (886) 2 2715 3029

4-474

This datasheet has been downloaded from: www.DatasheetCatalog.com Datasheets for electronic components.

Das könnte Ihnen auch gefallen

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- IGBTs BasicsDokument10 SeitenIGBTs BasicsTomas HuerdoNoch keine Bewertungen

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (587)

- PAMANTASAN NG LUNGSOD NG MAYNILA Experiment No.1Dokument12 SeitenPAMANTASAN NG LUNGSOD NG MAYNILA Experiment No.1ManuelitoBorjaNoch keine Bewertungen

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (894)

- Project Report On Infra Red Remote ControlDokument19 SeitenProject Report On Infra Red Remote ControlDIPAK VINAYAK SHIRBHATE88% (8)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- 809PET Silicon Carbide MOSFETs IGBT PDFDokument5 Seiten809PET Silicon Carbide MOSFETs IGBT PDFkbdkishoreNoch keine Bewertungen

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- Full Introduction About IC Packages Types and FunctionsDokument17 SeitenFull Introduction About IC Packages Types and FunctionsjackNoch keine Bewertungen

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- 4 LedDokument88 Seiten4 Ledmoaiz quraishiNoch keine Bewertungen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Semiconductor Electronics - Materials, Devices and Simple CircuitsDokument25 SeitenSemiconductor Electronics - Materials, Devices and Simple CircuitsVinay SinghNoch keine Bewertungen

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Optimizing The Efficiency of Solar Cells Based On Gaas: Electronics Department, University of Batna, AlgeriaDokument8 SeitenOptimizing The Efficiency of Solar Cells Based On Gaas: Electronics Department, University of Batna, AlgeriaSubhadip MondalNoch keine Bewertungen

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Irg4Pc50Udpbf: Insulated Gate Bipolar Transistor With Ultrafast Soft Recovery Diode Ultrafast Copack IgbtDokument11 SeitenIrg4Pc50Udpbf: Insulated Gate Bipolar Transistor With Ultrafast Soft Recovery Diode Ultrafast Copack IgbtVíctor Josemaria Rivero DunoNoch keine Bewertungen

- Gate Questions On MosfetDokument16 SeitenGate Questions On MosfetEsakkiPonniah100% (1)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- 212 EE203 Chapter4Dokument104 Seiten212 EE203 Chapter4Ammar AlmobyiedNoch keine Bewertungen

- PhotodiodeDokument24 SeitenPhotodiodechefroyale.23100% (1)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- EEC124 Practical ManualDokument27 SeitenEEC124 Practical ManualSamuel DavidNoch keine Bewertungen

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- Magnetic Random Access Memory (MRAM)Dokument21 SeitenMagnetic Random Access Memory (MRAM)Scott Backster ClarckNoch keine Bewertungen

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2219)

- Department of Software Engineering: Lab1: Familiarization of Basic Gates and Digital IcsDokument14 SeitenDepartment of Software Engineering: Lab1: Familiarization of Basic Gates and Digital IcsMuhammad RehanNoch keine Bewertungen

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- PJ4N3KDW PanJitInternationalDokument3 SeitenPJ4N3KDW PanJitInternationalcindy nindiNoch keine Bewertungen

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- IRFPG50 International RectifierDokument8 SeitenIRFPG50 International RectifierDionatan RangelNoch keine Bewertungen

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (265)

- Homework 2Dokument4 SeitenHomework 2sissishinyNoch keine Bewertungen

- NJW 21193 GDokument2 SeitenNJW 21193 GAgung KurniandraNoch keine Bewertungen

- Basics For NumericalsDokument23 SeitenBasics For NumericalsTara VishinNoch keine Bewertungen

- JFETsDokument78 SeitenJFETsLai Yon Peng100% (2)

- Vlsi in PDFDokument9 SeitenVlsi in PDFnatureheaplerNoch keine Bewertungen

- EE 3105 AssignmentDokument2 SeitenEE 3105 AssignmentKarlo Miranda MacadangdangNoch keine Bewertungen

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- Electrical Properties of MaterialsDokument4 SeitenElectrical Properties of MaterialsOzan YıldızNoch keine Bewertungen

- Question Bank BEEE FinalDokument183 SeitenQuestion Bank BEEE Finalgadepranjali04Noch keine Bewertungen

- MOSFET Design Considerations ExplainedDokument2 SeitenMOSFET Design Considerations ExplainedabcNoch keine Bewertungen

- Han 2020Dokument13 SeitenHan 2020PC MNoch keine Bewertungen

- Transformable Junctionless Transistor (T-JLT)Dokument6 SeitenTransformable Junctionless Transistor (T-JLT)Rakesh KumarNoch keine Bewertungen

- Development of ALD HfZrOx With TDEAH TDEAZ and H2O (Dehydroxylation)Dokument6 SeitenDevelopment of ALD HfZrOx With TDEAH TDEAZ and H2O (Dehydroxylation)che woei chinNoch keine Bewertungen

- Mosfet DFP2N60Dokument11 SeitenMosfet DFP2N60israe2Noch keine Bewertungen

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (119)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)