Beruflich Dokumente

Kultur Dokumente

Cache

Hochgeladen von

Edwind MartínezCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Cache

Hochgeladen von

Edwind MartínezCopyright:

Verfügbare Formate

SISTEMA DE MEMORIA CACH

Memoria DRAM barata pero lenta Aade ciclos de espera (wait states) Memoria SRAM ms rpida, consume ms energa Permite acceso en 0 WS En general no es posible utilizar solamente SRAM Solucin: Utilizar principalmente DRAM Incorporar una menor cantidad de SRAM Guarda copias de la memoria principal

datos Memoria DRAM principal SRAM (CACHE)

direcciones

PROCESADOR

Control. cach

SISTEMA DE MEMORIA CACH

Principio de localidad Programas construidos sobre bucles repetitivos. Localidad temporal:

El programa tiende a utilizar la informacin que ha utilizado ms recientemente.

Localidad espacial:

El programa tiende a utilizar la informacin que se encuentra en posiciones de memoria cercanas o incluso adyacentes.

Primer acceso

Instr. 1

Lectura en DRAM Actualiz. cach Lectura en DRAM Actualiz. cach Lectura en DRAM Actualiz. cach Lectura en DRAM Actualiz. cach Lectura en DRAM Actualiz. cach Lectura en DRAM Actualiz. cach Lectura en DRAM Actualiz. cach Lectura en DRAM Actualiz. cach

Segundo acceso y subsiguientes

Lectura en cach Lectura en cach Lectura en cach Lectura en cach Lectura en cach Lectura en cach Lectura en cach Lectura en cach

Instr. n

...

SISTEMA DE MEMORIA CACH Rendimiento de la cach Aciertos R(%) = Accesos a memoria

100

Normalmente R ~ 85-95%

Coherencia de la cach

Acceso a memoria Fallos de consistencia Bsqueda en la cach Multiprocesadores Acceso directo a memoria (DMA) Otros bus master

Acierto? SI Lectura en cach

NO

Lectura en DRAM

Actualizac. de la cach

FIN

SISTEMA DE MEMORIA CACH Elementos del sistema de memoria cach

Memoria rpida (SRAM) Lgica de gestin de la cach Directorio de la cach

SRAM

DIRECCIONES

SRAM

W/R# CE

DATOS

Acceso rpido

Directorio de cach

0 1 2 ... 0 1 2 ...

Direccin del bus comparada con todas las del directorio

Direcciones

Datos

SISTEMA DE MEMORIA CACH

Clasificacin de los sistemas de cach Criterio Tipos Look-through (en serie) Look-aside (en paralelo) Arquitectura De 1 nivel De varios niveles nica Separada write-through buffered write-through write-back Vaciado de la cach Vigilancia del bus Forzada por software Totalmente asociativa De correspondencia directa Asociativa de dos vas Asociativa de cuatro vas, etc

Poltica de escritura

Protocolo de control de coherencia

Organizacin

SISTEMA DE MEMORIA CACH

Arquitectura look-through (en serie)

PROCESADOR

Ventajas: Acceso simultneo por parte de los bus master. Reduccin en el tiempo de utilizacin del bus. Pueden conseguirse escrituras con 0 WS usando escritura retrasada. Inconvenientes:

Bus Master 1 Bus Master 1

CACH BUFFER

Memoria principal

Acceso a memoria principal ralentizado. Penalizacin de bsqueda. Mayor dificultad de diseo

SISTEMA DE MEMORIA CACH

Arquitectura look-aside (en paralelo)

PROCESADOR

Ventajas: Lectura en DRAM ms rpida. No hay penalizacin de bsqueda. Simplicidad de diseo

CACH

Inconvenientes: No se reduce la utilizacin del bus. Acceso simultneo a cach y DRAM. Todos los accesos inicial una lectura en DRAM. Tiempo de precarga. No es posible operaciones simultneas de bus master. Memoria principal

Bus Master 1 Bus Master 1

SISTEMA DE MEMORIA CACH

Arquitectura de un solo nivel y de varios niveles

PROCESADOR PROCESADOR Cach de nivel 1

CACH

Cach de nivel 2

Memoria principal

Bus Master 1 Bus Master 1

Memoria principal

Bus Master 1 Bus Master 1

Tamao de las memorias

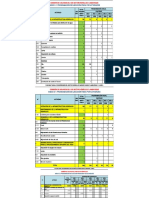

Tamao 1 Kb aciertos 41 % 73 % 81 % 86 % 88 % 89 %

Primera cach pequea Segunda cach mayor

8 Kb 16 Kb 32 Kb 64 Kb 128 Kb

SISTEMA DE MEMORIA CACH

Cach nica y cach separada

Ejecucin de una instruccin

Fetch

Decod

Ejec

Mem

Cach

Sistema de cach nica

direcciones Procesador

datos

Cach de instrucciones Sistema de cach separada

Cach de datos

direcciones

datos Procesador

SISTEMA DE MEMORIA CACH

Polticas de escritura en la cach

Prdidas de coherencia con la cach producidas por: Cach modificada, pero no DRAM (Escritura en cach no actualizada) DRAM modificada pero no cach (Escritura en DRAM por parte de un bus master)

Poltica write through

Cada escritura en cach se pasa a DRAM Muy simple Efectiva en todos los casos Lenta, debe accederse a DRAM en todos los accesos.

Poltica write through con buffer

Cada escritura se realiza slo en cach Se actualiza la DRAM en el ciclo siguiente Si hay dos escrituras seguidas, se retrasa la segunda Otros bus master son detenidos hasta la actualizacin segn los casos

Poltica write back

Cada escritura se realiza slo en cach y se marca como modificada La DRAM no se actualiza Si un bus master necesita leer, se ve si esa direccin est actualizada y se actualiza si no. Muy complicada de implementar

SISTEMA DE MEMORIA CACH

Interaccin entre los bus-master y la cach (Control de coherencia) Control de coherencia mediante vigilancia del bus

1. Bus master intenta escribir en DRAM a) en write-through basta invalidar la lnea de cach b) en write-back: Se aborta el ciclo de bus Se vuelca la lnea entera de cach a DRAM Se reinicia el ciclo de bus 2. El bus master lee una posicin de memoria en DRAM Solamente en caso de poltica write back se realiza un ciclo de bus similar al caso anterior.

Control de coherencia mediante vaciado de cach

Apropiada en polticas write-through. Cada vez que un bus master intenta escribir en RAM se invalida la cach completa. Muy exagerado, funciona bien siempre. Apropiado si hay pocos accesos de los bus master.

Control de coherencia mediante software

El Sistema Operativo tiene el control de los perifricos Pueden organizarse los accesos para que no haya problemas de coherencia Ms rpido que el control por hardware.

SISTEMA DE MEMORIA CACH

Organizacin de la cach Totalmente asociativa

Cualquier direccin de DRAM puede copiarse en cualquier direccin de cach Se necesita leer todo el directorio en cada acceso

Datos 4 Direccin de datos 3 Direccin de datos 1 Direccin de datos 4 Direccin de datos 2 Datos 3 Datos 3 Datos 1 Datos 4 Datos 2

Directorio de la cach

Cach

De correspondencia directa

DRAM dividia en pginas Slo se lee una direccin cada vez

Datos 2 Datos 1

Pgina n Datos 4 Datos 3 Pgina n-1 Pgina 0 Pgina n Datos 3 Datos 2 Datos 4 Pgina n-1 Pgina 0

MEMORIA DRAM MEMORIA DRAM

Directorio de la cach

Cach

Datos 2 Datos 1

SISTEMA DE MEMORIA CACH

Organizacin de la cach Asociativa de 2 vas, 4 vas, etc...

Es una solucin intermedia DRAM dividida en pginas Varias opciones en cach Se realiza una lectura por cada entrada Se utiliza el algoritmo LRU

Datos 6 Datos 5 Pgina 3 Datos 6 Datos 5

Pgina 3

Pgina 0 Pgina 0

Datos 2 Datos 1

Datos 3 Datos 2 Datos 1

Pgina 0

Directorios de la cach

Cach

Pgina 1

Pgina 2 Pgina 0

Datos 4 Datos 3

Pgina 2

Datos 4

Pgina 3

Pgina 4

Pgina n

SISTEMA DE MEMORIA CACH

Regiones de memoria no cacheable Dispositivos de E/S Regiones de RAM especiales: Memoria de pantalla Buffer de una tarjeta de red Zonas de RAM ficticia Dispositivos incluidos en mapa RAM Entrada NCA# Desactivacin de cach Momentos en que se est comprobando la RAM Entrada #FLUSH

Das könnte Ihnen auch gefallen

- Contrato Servicios ITDokument7 SeitenContrato Servicios ITEdwind MartínezNoch keine Bewertungen

- Ejemplo deDokument1 SeiteEjemplo deEdwind MartínezNoch keine Bewertungen

- Algoritmo en ExcelDokument12 SeitenAlgoritmo en ExcelCarlos Aníbal PetrivNoch keine Bewertungen

- Conceptos Bsicos de Javascript Con Ejemplos PDFDokument44 SeitenConceptos Bsicos de Javascript Con Ejemplos PDFmclobelyNoch keine Bewertungen

- Clase 02 El AlfabetoDokument33 SeitenClase 02 El AlfabetoEdwind MartínezNoch keine Bewertungen

- Analisis Matricial de EstructurasDokument31 SeitenAnalisis Matricial de EstructurasdiallodeNoch keine Bewertungen

- ADALINE y MADALINE: Redes neuronales pionerasDokument8 SeitenADALINE y MADALINE: Redes neuronales pionerasEnrique Villegas MedinaNoch keine Bewertungen

- Las Máquinas de Soporte Vectorial (SVMS)Dokument6 SeitenLas Máquinas de Soporte Vectorial (SVMS)Pablo Velarde AlvaradoNoch keine Bewertungen

- Analisis Matricial de EstructurasDokument31 SeitenAnalisis Matricial de EstructurasdiallodeNoch keine Bewertungen

- 1-Introduccion MSNET1.1Dokument22 Seiten1-Introduccion MSNET1.1Edwind MartínezNoch keine Bewertungen

- Manual de Hojas de Estilos PDFDokument25 SeitenManual de Hojas de Estilos PDFCarlos Figueroa100% (1)

- Manual JqueryDokument62 SeitenManual JqueryFrancisco Javier CastilloNoch keine Bewertungen

- Java MVCDokument24 SeitenJava MVCeloyediNoch keine Bewertungen

- Pilas ColasDokument31 SeitenPilas ColasAidee84Noch keine Bewertungen

- AC-Transparencias PCIDokument34 SeitenAC-Transparencias PCIEdwind MartínezNoch keine Bewertungen

- 185 Convocatoria 18 01 12 2Dokument209 Seiten185 Convocatoria 18 01 12 2Edwind MartínezNoch keine Bewertungen

- Estructuras DinamicasDokument53 SeitenEstructuras DinamicasRocío Arias Morales100% (1)

- Conectadores Premoldeados. para Redes de Distribución SubterráneaDokument6 SeitenConectadores Premoldeados. para Redes de Distribución SubterráneaRodrigo SantosNoch keine Bewertungen

- Placa BaseDokument3 SeitenPlaca BaseyoworNoch keine Bewertungen

- Man Info 2008Dokument56 SeitenMan Info 2008Diego Alejandro SilvaNoch keine Bewertungen

- Practica 7 (Ondas Guiadas)Dokument8 SeitenPractica 7 (Ondas Guiadas)Xavier LunacyNoch keine Bewertungen

- NumeradorDisplayDokument8 SeitenNumeradorDisplayGabrielNoch keine Bewertungen

- Análisis de potencia en circuitos de CADokument12 SeitenAnálisis de potencia en circuitos de CALaura Milena ParraNoch keine Bewertungen

- M580 Proactec 2015 - Schneider ElectricDokument40 SeitenM580 Proactec 2015 - Schneider Electricalio0oNoch keine Bewertungen

- Conversión DAC PIC18f4550Dokument3 SeitenConversión DAC PIC18f4550camilaNoch keine Bewertungen

- Caracterizacion de Un Opamp 741Dokument4 SeitenCaracterizacion de Un Opamp 741KaarrlozzNoch keine Bewertungen

- Calculos electricosDokument46 SeitenCalculos electricosHENRY GUSTAVO PAUTRAT EGOAVILNoch keine Bewertungen

- Manual Automotriz ComputadorasDokument25 SeitenManual Automotriz ComputadorasBarrikelo Cash BerryNoch keine Bewertungen

- Consulta N-1 Amplificador-OperacionalDokument5 SeitenConsulta N-1 Amplificador-OperacionalangelNoch keine Bewertungen

- ECT sensor: funcionamiento y diagnóstico del sensor de temperatura del refrigeranteDokument19 SeitenECT sensor: funcionamiento y diagnóstico del sensor de temperatura del refrigeranteFausto LojaNoch keine Bewertungen

- 1 Tipos y Componentes de Una Red PDFDokument19 Seiten1 Tipos y Componentes de Una Red PDFAlexito Mendoza RoblesNoch keine Bewertungen

- Clemas de ConexiónDokument20 SeitenClemas de ConexiónJorch Chavez TorresNoch keine Bewertungen

- 02 Biomédico EETT MaraDokument51 Seiten02 Biomédico EETT MaraKatherine Lucero Cabello LopezNoch keine Bewertungen

- Informe Iee Antena Log-PeriodicaDokument6 SeitenInforme Iee Antena Log-PeriodicaNathy Niama67% (3)

- Actividad I Del Módulo IIDokument7 SeitenActividad I Del Módulo IIRebeca RodríguezNoch keine Bewertungen

- Ingeniería de telecomunicaciones: campos de acciónDokument6 SeitenIngeniería de telecomunicaciones: campos de acciónJose Hidalgo Silva100% (1)

- Guia 4 de Tecnologia e Informatica Grado Sexto.Dokument3 SeitenGuia 4 de Tecnologia e Informatica Grado Sexto.Olivo Samir Sanchez AlvearNoch keine Bewertungen

- 150.996 - Manuale Power Tronic Advance - SPA - ED.08 - 2013Dokument27 Seiten150.996 - Manuale Power Tronic Advance - SPA - ED.08 - 2013Mauricio AriasNoch keine Bewertungen

- Aplicacion de Triac y ExplicacionDokument5 SeitenAplicacion de Triac y ExplicacionRuth DuranNoch keine Bewertungen

- Código de Destello - CumminsDokument9 SeitenCódigo de Destello - CumminsGuillermo MartinezNoch keine Bewertungen

- Problemas Prototipicos Sobre Dispositivos EléctricosDokument4 SeitenProblemas Prototipicos Sobre Dispositivos EléctricosLuis gallegosNoch keine Bewertungen

- RUCKUS H510 Data Sheet - SpanishDokument5 SeitenRUCKUS H510 Data Sheet - SpanishJessica GonzálezNoch keine Bewertungen

- TRIACDokument11 SeitenTRIACandrexxxoNoch keine Bewertungen

- Consulta Sobre CapacitoresDokument4 SeitenConsulta Sobre CapacitoresGeraldine RomeroNoch keine Bewertungen

- PDMI (1) para ComiteDokument4 SeitenPDMI (1) para ComiteCarlos SanchezNoch keine Bewertungen

- Catalogo SsdielectDokument84 SeitenCatalogo SsdielectClaudio BordonesNoch keine Bewertungen

- EPIC Installation Manual EspDokument61 SeitenEPIC Installation Manual EspVer GhomNoch keine Bewertungen