Beruflich Dokumente

Kultur Dokumente

Intel Microprocessor

Hochgeladen von

Lissa JusohOriginalbeschreibung:

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Intel Microprocessor

Hochgeladen von

Lissa JusohCopyright:

Verfügbare Formate

The 4-bit processors

Intel 4004: first single-chip microprocessor

Introduced November 15, 1971 Clock rate 740 kHz[1] 0.07 MIPS Bus Width 4 bits (multiplexed address/data due to limited pins) PMOS Number of Transistors 2,300 at 10 m Addressable Memory 640 bytes Program Memory 4 KB (4 KB) One of the earliest Commercial Microprocessors (cf. Four Phase Systems AL1, F14 CADC) Originally designed to be used in Busicom calculator

MCS-4 Family:

4004-CPU 4001-ROM & 4 Bit Port 4002-RAM & 4 Bit Port 4003-10 Bit Shift Register 4008-Memory+I/O Interface 4009-Memory+I/O Interface

Intel 4040

MCS-40 Family:

4040-CPU 4101-1024-bit (256 4) Static RAM with separate I/O 4201-4 MHz Clock Generator 4207-General Purpose Byte I/O Port 4209-General Purpose Byte I/O Port 4211-General Purpose Byte I/O Port 4265-Programmable General Purpose I/O Device 4269-Programmable Keyboard Display Device 4289-Standard Memory Interface for MCS-4/40 4308-8192-bit (1024 8) ROM w/ 4-bit I/O Ports 4316-16384-bit (2048 8) Static ROM 4702-2048-bit (256 8) EPROM 48015.185 MHz Clock Generator Crystal for 4004/4201A or 4040/4201A

The 8-bit processors

8008

Introduced April 1, 1972 Clock rate 500 kHz (80081: 800 kHz) 0.05 MIPS Bus Width 8 bits (multiplexed address/data due to limited pins) Enhancement load PMOS logic

Number of Transistors 3,500 at 10 m Addressable memory 16 KB Typical in early 8 bit microcomputers, dumb terminals, general calculators, bottling machines Developed in tandem with 4004 Originally intended for use in the Datapoint 2200 microcomputer Key volume deployment in Texas Instruments 742 microcomputer in >3,000 Ford dealerships

8080

Introduced April 1, 1974 Clock rate 2 MHz (very rare 8080B: 3 MHz) 0.64 MIPS Bus Width 8 bits data, 16 bits address Enhancement load NMOS logic Number of Transistors 6,000 Assembly language downwards compatible with 8008. Addressable memory 64 KB Up to 10X the performance of the 8008 Used in the Altair 8800, Traffic light controller, cruise missile Required six support chips versus 20 for the 8008

8085

Introduced March 1976 Clock rate 3 MHz [2] 0.37 MIPS Bus Width 8 bits data, 16 bits address Depletion load NMOS logic Number of Transistors 6,500 at 3 m Binary compatible downwards with the 8080. Used in Toledo scales. Also was used as a computer peripheral controller modems, harddisks,printers, etc... CMOS 80C85 in Mars Sojourner, Radio Shack Model 100 portable. High level of integration, operating for the first time on a single 5 volt power supply, from 12 volts previously. Also featured serial I/O,3 maskable interrupts,1 Non-maskable interrupt,1 externally expandable interrupt w/[8259],status,DMA.

MCS-85 Family:

8155-RAM+ 3 I/O Ports+Timer "Active Low CS" 8185-SRAM 8202-Dynamic RAM Controller 8203-Dynamic RAM Controller 8205-1 Of 8 Binary Decoder 8206-Error Detection & Correction Unit 8207-DRAM Controller 8210-TTL To MOS Shifter & High Voltage Clock Driver 8216-4 Bit Parallel Bidirectional Bus Driver 8219-Bus Controller 8222-Dynamic RAM Refresh Controller 8226-4 Bit Parallel Bidirectional Bus Driver 8232-Floating Point Processor

8237-DMA Controller 8251-Communication Controller 8253-Programmable Interval Timer 8254-Programmable Interval Timer 8255-Programmable Peripheral Interface 8256-Multifunction Support Controller 8257-DMA Controller 8259-Programmable Interrupt Controller 8271-Programmable Floppy Disk Controller 8272-Single/Double Density Floppy Disk Controller 8273-Programmable HDLC/SDLC Protocol Controller 8274-Multi-Protocol Serial Controller 8275-CRT Controller 8276-Small System CRT Controller 8279-KeyBoard/Display Controller 8283-8-bit Inverting Latch with Output Buffer 8291-GPIB Talker/Listener 8292-GPIB Controller 8293-GPIB Transceiver 8294-Data Encryption/Decryption Unit+1 O/P Port 8295-Dot Matrix Printer Controller 8296-GPIB Transceiver 8297-GPIB Transceiver 8355-16,384-bit (2048 8) ROM with I/O 8755-EPROM+2 I/O Ports

Microcontrollers

They are ICs with CPU,RAM,ROM (or PROM or EPROM),I/O Ports,Timers & Interrupts

Intel 8048

Single accumulator Harvard architecture

MCS-48 family:

8020-Single-Component 8-Bit Microcontroller 8021-Single-Component 8-Bit Microcontroller 8022-Single-Component 8-Bit Microcontroller With On Chip A/D Converter 8035-Single-Component 8-Bit Microcontroller 8039-Single-Component 8-Bit Microcontroller 8040-Single-Component 8-Bit Microcontroller 8041-Universal Peripheral Interface 8-Bit Slave Microcontroller 8641-Universal Peripheral Interface 8-Bit Slave Microcontroller 8741-Universal Peripheral Interface 8-Bit Slave Microcontroller 8042-Universal Peripheral Interface 8-Bit Slave Microcontroller 8742-Universal Peripheral Interface 8-Bit Slave Microcontroller 8243-Input/Output Expander 8048-Single-Component 8-Bit Microcontroller 8048-Single-Component 8-Bit Microcontroller 8748-Single-Component 8-Bit Microcontroller 8049-Single-Component 8-Bit Microcontroller

8048-Single-Component 8-Bit Microcontroller 8749-Single-Component 8-Bit Microcontroller 8050-Single-Component 8-Bit Microcontroller

Intel 8051

Single accumulator Harvard architecture

MCS-51 Family:

8031-8-Bit Control-Oriented Microcontroller 8032-8-Bit Control-Oriented Microcontroller 8044-High Performance 8-Bit Microcontroller 8344-High Performance 8-Bit Microcontroller 8744-High Performance 8-Bit Microcontroller 8051-8-Bit Control-Oriented Microcontroller 8052-8-Bit Control-Oriented Microcontroller 8054-8-Bit Control-Oriented Microcontroller 8058-8-Bit Control-Oriented Microcontroller 8351-8-Bit Control-Oriented Microcontroller 8352-8-Bit Control-Oriented Microcontroller 8354-8-Bit Control-Oriented Microcontroller 8358-8-Bit Control-Oriented Microcontroller 8751-8-Bit Control-Oriented Microcontroller 8752-8-Bit Control-Oriented Microcontroller 8754-8-Bit Control-Oriented Microcontroller 8758-8-Bit Control-Oriented Microcontroller 80151-8-Bit Control-Oriented Microcontroller 83151-8-Bit Control-Oriented Microcontroller 87151-8-Bit Control-Oriented Microcontroller 80152-8-Bit Control-Oriented Microcontroller 83152-8-Bit Control-Oriented Microcontroller 80251-8-Bit Control-Oriented Microcontroller 87251-8-Bit Control-Oriented Microcontroller

MCS-96 Family

8094-16-Bit Microcontroller (48-Pin ROMLess Without A/D) 8095-16-Bit Microcontroller (48-Pin ROMLess With A/D) 8096-16-Bit Microcontroller (68-Pin ROMLess Without A/D) 8097-16-Bit Microcontroller (68-Pin ROMLess With A/D) 8394-16-Bit Microcontroller (48-Pin With ROM Without A/D) 8395-16-Bit Microcontroller (48-Pin With ROM With A/D) 8396-16-Bit Microcontroller (68-Pin With ROM Without A/D)] 8397-16-Bit Microcontroller (68-Pin With ROM With A/D) 8794-16-Bit Microcontroller (48-Pin With EROM Without A/D) 8795-16-Bit Microcontroller (48-Pin With EROM With A/D) 8796-16-Bit Microcontroller (68-Pin With EROM Without A/D) 8797-16-Bit Microcontroller (68-Pin With EROM With A/D) 8098-16-Bit Microcontroller 8398-16-Bit Microcontroller 8798-16-Bit Microcontroller

80196-16-Bit Microcontroller 83196-16-Bit Microcontroller 87196-16-Bit Microcontroller 80296-16-Bit Microcontroller

The bit-slice processor

3000 Family

Intel D3002.

Introduced 3rd Qtr, 1974 Members of the family

3001-Microcontrol Unit 3002-2-bit Arithmetic Logic Unit slice 3003-Look-ahead Carry Generator 3205-High-performance 1 Of 8 Binary Decoder 3207-Quad Bipolar-to-MOS Level Shifter and Driver 3208-Hex Sense Amp and Latch for MOS Memories 3210-TTL-to-MOS Level Shifter and High Voltage Clock Driver 3211-ECL-to-MOS Level Shifter and High Voltage Clock Driver 3212-Multimode Latch Buffer 3214-Interrupt Control Unit 3216-Parallel,Inverting Bi-Directional Bus Driver 3222-Refresh Controller for 4K NMOS DRAMs 3226-Parallel,Inverting Bi-Directional Bus Driver 3232-Address Multiplexer and Refresh Counter for 4K DRAMs 3242-Address Multiplexer and Refresh Counter for 16K DRAMs 3245-Quad Bipolar TTL-to-MOS Level Shifter and Driver for 4K 3246-Quad Bipolar ECL-to-MOS Level Shifter and Driver for 4K 3404-High-performance 6-bit Latch 3408-Hex Sense Amp and Latch for MOS Memories

Bus Width 2-n bits data/address (depending on number of slices used)

The 16-bit processors: origin of x86

8086

Introduced June 8, 1978 Clock rates:

o o o

4.77 MHz with 0.33 MIPS[2] 8 MHz with 0.66 MIPS 10 MHz with 0.75 MIPS

The memory is divided into odd and even banks. It accesses both the banks simultaneuosly in order to read 16 bit of data in one clock cycle.

Bus Width 16 bits data, 20 bits address Number of Transistors 29,000 at 3 m Addressable memory 1 megabyte Up to 10X the performance of 8080 (typically lower) Used in portable computing, and in the IBM PS/2 Model 25 and Model 30. Also used in the AT&T PC6300 / Olivetti M24, a popular IBM PC-compatible (predating the IBM PS/2 line.)

Used segment registers to access more than 64 KB of data at once, which many programmers complained made their work excessively difficult.

8088

Introduced June 1, 1979 Clock rates:

o o

4.77 MHz with 0.33 MIPS 8 MHz with 0.75 MIPS [2]

Internal architecture 16 bits External bus Width 8 bits data, 20 bits address Number of Transistors 29,000 at 3 m Addressable memory 1 megabyte Identical to 8086 except for its 8 bit external bus (hence an 8 instead of a 6 at the end) Used in IBM PCs and PC clones

MCS-86 Family

8086-CPU 8088-CPU 8087-Math Coprocessor 8089-Programmable DMA Coprocessor 8208-Dynamic RAM Controller 8284-Clock Generator & Driver 8286-Octal Bus Transceiver 8287-Octal Bus Transceiver 8288-Bus Controller 8289-Bus Arbiter 80130-iRMX 86 Operating System Processors 80186-CPU 80188-CPU 80286-CPU 80287-Math-Coprocessor 82050-Communication Controller 82062-Winchester Disk Controller 82064-Floppy Disk Controller 82091-Advanced Integrated Peripheral 82188-Bus Controller 82288-Bus Controller

82389-Message Passing Coprocessor 82503-Dual Serial Transceiver 82510-Communication Controller 82530-Serial Communication Controller 82577-PCI LAN Controller 82586-IEEE 802.3 EtherNET LAN CoProcessor 82596-LAN-CoProcessor 82720-Graphics Display Controller 82730-Text Coprocessor 80386-CPU 80387-Math-CoProcessor

80186

Introduced 1982 Clock rates

o

6 MHz with > 1 MIPS

Number of Transistors 29,000 at 2 m Included two timers, a DMA controller, and an interrupt controller on the chip in addition to the processor (These were at fixed addresses which differed from the IBM PC, making it impossible to build a 100% PC-compatible computer around the 80186.)

Added a few opcodes and exceptions to the 8086 design; otherwise identical instruction set to 8086 and 8088. Used mostly in embedded applications controllers, point-of-sale systems, terminals, and the like Used in several non-PC-Compatible MS-DOS computers including RM Nimbus, Tandy 2000 Later renamed the iAPX 186

80188

A version of the 80186 with an 8-bit external data bus Later renamed the iAPX 188

80286

Introduced February 1, 1982 Clock rates:

o o o o

6 MHz with 0.9 MIPS 8 MHz, 10 MHz with 1.5 MIPS 12.5 MHz with 2.66 MIPS 16 MHz, 20 MHz and 25 MHz available.

Bus Width: 16 bit data, 24 bit address. Included memory protection hardware to support multitasking operating systems with per-process address space Number of Transistors 134,000 at 1.5 m Addressable memory 16 MB (16 MB) Added protected-mode features to 8086 with essentially the same instruction set 3-6X the performance of the 8086 Widely used in IBM-PC AT and AT clones contemporary to it

32-bit processors: the non-x86 microprocessors

iAPX 432

Introduced January 1, 1981 as Intel's first 32-bit microprocessor Multi-chip CPU; Intel's first 32-bit microprocessor Object/capability architecture Microcoded operating system primitives One terabyte virtual address space Hardware support for fault tolerance Two-chip General Data Processor (GDP), consists of 43201 and 43202 43203 Interface Processor (IP) interfaces to I/O subsystem 43204 Bus Interface Unit (BIU) simplifies building multiprocessor systems 43205 Memory Control Unit (MCU) Architecture and execution unit internal data paths 32 bit Clock rates:

o o o

5 MHz 7 MHz 8 MHz

i960 aka 80960

Introduced April 5, 1988 RISC-like 32-bit architecture Predominantly used in embedded systems Evolved from the capability processor developed for the BiiN joint venture with Siemens Many variants identified by two-letter suffixes.

80386SX (chronological entry)

Introduced June 16, 1988 See main entry

80376 (chronological entry)

Introduced January 16, 1989 See main entry

i860 aka 80860

Introduced February 27, 1989 RISC 32/64-bit architecture, with floating point pipeline characteristics very visible to programmer Used in the Intel iPSC/860 Hypercube parallel supercomputer mid-life kicker in the i870 processor (primarily a speed bump, some refinement/extension of instruction set) Used in the Intel Delta massively parallel supercomputer prototype, emplaced at California Institute of Technology Used in the Intel Paragon massively parallel supercomputer, emplaced at Sandia National Laboratory

XScale

Introduced August 23, 2000 32-bit RISC microprocessor based on the ARM architecture Many variants, such as the PXA2xx applications processors, IOP3xx I/O processors and IXP2xxx and IXP4xx network processors.

32-bit processors: the 80386 range

80386DX

Introduced October 17, 1985 Clock rates:

o o o o

16 MHz with 5 to 6 MIPS 20 MHz with 6 to 7 MIPS, introduced February 16, 1987 25 MHz with 8.5 MIPS, introduced April 4, 1988 33 MHz with 11.4 MIPS (9.4 SPECint92 on Compaq/i 16K L2), introduced April 10, 1989

Bus Width 32 bit data, 32 bit address Number of Transistors 275,000 at 1 m Addressable memory 4 GB (4 GB) Virtual memory 64 TB (64 TiB) First x86 chip to handle 32-bit data sets Reworked and expanded memory protection support including paged virtual memory and virtual-86 mode, features required at the time by Xenix and Unix. This memory capability spurred the development and availability of OS/2 and is a fundamental requirement for modern operating systems like Linux, Vista, and Mac OS.

Used in Desktop computing

80960 (i960) (chronological entry)

Introduced April 5, 1988 See main entry

80386SX

Introduced June 16, 1988 Clock rates:

o o o o

16 MHz with 2.5 MIPS 20 MHz with 2.5 MIPS, introduced January 25, 1989 25 MHz with 2.7 MIPS, introduced January 25, 1989 33 MHz with 2.9 MIPS, introduced October 26, 1992

Internal architecture 32 bits External data bus width 16 bits External address bus width 24 bits Number of Transistors 275,000 at 1 m Addressable memory 16 MB Virtual memory 32 GB Narrower buses enable low-cost 32-bit processing Used in entry-level desktop and portable computing No Math Co-Processor No commercial Software used for protected mode or virtual storage for many years

80376

The Intel i376 is an embedded version of the i386SX.

Introduced January 16, 1989; Discontinued June 15, 2001 Variant of 386SX intended for embedded systems No "real mode", starts up directly in "protected mode" Replaced by much more successful 80386EX from 1994

80860 (i860) (chronological entry)

Introduced February 27, 1989 See main entry

80486DX (chronological entry)

Introduced April 10, 1989 See main entry

80386SL

Introduced October 15, 1990 Clock rates:

o o

20 MHz with 4.21 MIPS 25 MHz with 5.3 MIPS, introduced September 30, 1991

Internal architecture 32 bits External bus width 16 bits Number of Transistors 855,000 at 1 m Addressable memory 4 GB Virtual memory 1 TB First chip specifically made for portable computers because of low power consumption of chip Highly integrated, includes cache, bus, and memory controllers

10

80486SX/DX2/SL, Pentium, 80486DX4 (chronological entries)

Introduced 19911994 See main entries

80386EX

Introduced August 1994 Variant of 80386SX intended for embedded systems Static core, i.e. may run as slowly (and thus, power efficiently) as desired, down to full halt On-chip peripherals:

o o o o o o o

Clock and power mgmt Timers/counters Watchdog timer Serial I/O units (sync and async) and parallel I/O DMA RAM refresh JTAG test logic

Significantly more successful than the 80376 Used aboard several orbiting satellites and microsatellites Used in NASA's FlightLinux project

32-bit processors: the 80486 range

80486DX

Introduced April 10, 1989 Clock rates:

o o o

25 MHz with 20 MIPS (16.8 SPECint92, 7.40 SPECfp92) 33 MHz with 27 MIPS (22.4 SPECint92 on Micronics M4P 128 KB L2), introduced May 7, 1990 50 MHz with 41 MIPS (33.4 SPECint92, 14.5 SPECfp92 on Compaq/50L 256 KB L2), introduced June 24, 1991

Bus Width 32 bits Number of Transistors 1.2 million at 1 m; the 50 MHz was at 0.8 m Addressable memory 4 GB Virtual memory 1 TB Level 1 cache of 8 KB on chip Math coprocessor on chip 50X performance of the 8088 Used in Desktop computing and servers Family 4 model 3

80386SL (chronological entry)

Introduced October 15, 1990 See main entry

80486SX

11

Introduced April 22, 1991 Clock rates:

o o o o

16 MHz with 13 MIPS 20 MHz with 16.5 MIPS, introduced September 16, 1991 25 MHz with 20 MIPS (12 SPECint92), introduced September 16, 1991 33 MHz with 27 MIPS (15.86 SPECint92), introduced September 21, 1992

Bus Width 32 bits Number of Transistors 1.185 million at 1 m and 900,000 at 0.8 m Addressable memory 4 GB Virtual memory 1 TB Identical in design to 486DX but without math coprocessor. The first version was an 80486DX with disabled mathco in the chip and different pin configuration. If the user needed math co capabilities, he must add 487SX which was actually an 486DX with different pin configuration to prevent the user from installing a 486DX instead of 487SX, so with this configuration 486SX+487SX you had 2 identical CPU's with only 1 turned on

Used in low-cost entry to 486 CPU desktop computing Upgradable with the Intel OverDrive processor Family 4 model 2

80486DX2

Introduced March 3, 1992

Runs at twice the speed of the external bus (FSB).

Clock rates:

o o o o

40 MHz 50 MHz 66 MHz 100 MHz (This was only made a short time due to high failure rates.)

80486SL

Introduced November 9, 1992 Clock rates:

o o o

20 MHz with 15.4MIPS 25 MHz with 19 MIPS 33 MHz with 25 MIPS

Bus Width 32 bits Number of Transistors 1.4 million at 0.8 m Addressable memory 4 GB Virtual memory 1 TB Used in notebook computers Family 4 model 3

Pentium (chronological entry)

Introduced March 22, 1993 See main entry

80486DX4

12

Introduced March 7, 1994 Clock rates:

o o

75 MHz with 53 MIPS (41.3 SPECint92, 20.1 SPECfp92 on Micronics M4P 256 KB L2) 100 MHz with 70.7 MIPS (54.59 SPECint92, 26.91 SPECfp92 on Micronics M4P 256 KB L2)

Number of Transistors 1.6 million at 0.6 m Bus width 32 bits Addressable memory 4 GB Virtual memory 64 TB Pin count 168 PGA Package, 208 sq ftP Package Used in high performance entry-level desktops and value notebooks Family 4 model 8

32-bit processors: P5 microarchitecture

Original Pentium

Bus width 64 bits System bus clock rate 60 or 66 MHz Address bus 32 bits Addressable Memory 4 GB Virtual Memory 64 TB Superscalar architecture Runs on 5 volts Used in desktops 16 KB of L1 cache P5 0.8 m process technology

o o o o o o

Introduced March 22, 1993 Number of transistors 3.1 million Socket 4 273 pin PGA processor package Package dimensions 2.16" 2.16" Family 5 model 1 Variants

60 MHz with 100 MIPS (70.4 SPECint92, 55.1 SPECfp92 on Xpress 256 KB L2) 66 MHz with 112 MIPS (77.9 SPECint92, 63.6 SPECfp92 on Xpress 256 KB L2)

P54 0.6 m process technology

o o o

Socket 5 296/320 pin PGA package Number of transistors 3.2 million Variants

75 MHz Introduced October 10, 1994 90, 100 MHz Introduced March 7, 1994

P54CQS 0.35 m process technology

o o o

Socket 5 296/320 pin PGA package Number of transistors 3.2 million Variants

120 MHz Introduced March 27, 1995

P54CS 0.35 m process technology

o o o o o

Number of transistors 3.3 million 90 mm die size Family 5 model 2 Variants Socket 5 296/320 pin PGA package

133 MHz Introduced June 12, 1995

13

150, 166 MHz Introduced January 4, 1996

Socket 7 296/321 pin PGA package

200 MHz Introduced June 10, 1996

Pentium with MMX Technology

P55C 0.35 m process technology

o o o o o o o o

Introduced January 8, 1997 Intel MMX (instruction set) support Socket 7 296/321 pin PGA (pin grid array) package 32 KB L1 cache Number of transistors 4.5 million System bus clock rate 66 MHz Basic P55C is family 5 model 4, mobile are family 5 model 7 and 8 Variants

166, 200 MHz Introduced January 8, 1997 233 MHz Introduced June 2, 1997 133 MHz (Mobile) 166, 266 MHz (Mobile) Introduced January 12, 1998 200, 233 MHz (Mobile) Introduced September 8, 1997 300 MHz (Mobile) Introduced January 7, 1999

32-bit processors: P6/Pentium M microarchitecture

Pentium Pro

Introduced November 1, 1995 Precursor to Pentium II and III Primarily used in server systems Socket 8 processor package (387 pins) (Dual SPGA) Number of transistors 5.5 million Family 6 model 1 0.6 m process technology

o o o o

16 KB L1 cache 256 KB integrated L2 cache 60 MHz system bus clock rate Variants

150 MHz

0.35 m process technology, or 0.35 m CPU with 0.6 m L2 cache

o o o o

Number of transistors 5.5 million 512 KB or 256 KB integrated L2 cache 60 or 66 MHz system bus clock rate Variants

166 MHz (66 MHz bus clock rate, 512 KB 0.35 m cache) Introduced November 1, 1995 180 MHz (60 MHz bus clock rate, 256 KB 0.6 m cache) Introduced November 1, 1995 200 MHz (66 MHz bus clock rate, 256 KB 0.6 m cache) Introduced November 1, 1995 200 MHz (66 MHz bus clock rate, 512 KB 0.35 m cache) Introduced November 1, 1995 200 MHz (66 MHz bus clock rate, 1 MB 0.35 m cache) Introduced August 18, 1997

Pentium II

14

Introduced May 7, 1997 Pentium Pro with MMX and improved 16-bit performance 242-pin Slot 1 (SEC) processor package Slot 1 Number of transistors 7.5 million 32 KB L1 cache 512 KB bandwidth external L2 cache The only Pentium II that did not have the L2 cache at bandwidth of the core was the Pentium II 450 PE. Klamath 0.35 m process technology (233, 266, 300 MHz)

o o o

66 MHz system bus clock rate Family 6 model 3 Variants

233, 266, 300 MHz Introduced May 7, 1997

Deschutes 0.25 m process technology (333, 350, 400, 450 MHz)

o o o o

Introduced January 26, 1998 66 MHz system bus clock rate (333 MHz variant), 100 MHz system bus clock rate for all models after Family 6 model 5 Variants

333 MHz Introduced January 26, 1998 350, 400 MHz Introduced April 15, 1998 450 MHz Introduced August 24, 1998 233, 266 MHz (Mobile) Introduced April 2, 1998 333 MHz Pentium II Overdrive processor for Socket 8 Introduced August 10, 1998; Engineering Sample Photo

300 MHz (Mobile) Introduced September 9, 1998 333 MHz (Mobile)

Celeron (Pentium II-based)

Covington 0.25 m process technology

o o o o o o o o

Introduced April 15, 1998 242-pin Slot 1 SEPP (Single Edge Processor Package) Number of transistors 7.5 million 66 MHz system bus clock rate Slot 1 32 KB L1 cache No L2 cache Variants

266 MHz Introduced April 15, 1998 300 MHz Introduced June 9, 1998

Mendocino 0.25 m process technology

o o o o o o o o o

Introduced August 24, 1998 242-pin Slot 1 SEPP (Single Edge Processor Package), Socket 370 PPGA package Number of transistors 19 million 66 MHz system bus clock rate Slot 1, Socket 370 32 KB L1 cache 128 KB integrated cache Family 6 model 6 Variants

300, 333 MHz Introduced August 24, 1998 366, 400 MHz Introduced January 4, 1999

15

433 MHz Introduced March 22, 1999 466 MHz 500 MHz Introduced August 2, 1999 533 MHz Introduced January 4, 2000 266 MHz (Mobile) 300 MHz (Mobile) 333 MHz (Mobile) Introduced April 5, 1999 366 MHz (Mobile) 400 MHz (Mobile) 433 MHz (Mobile) 450 MHz (Mobile) Introduced February 14, 2000 466 MHz (Mobile) 500 MHz (Mobile) Introduced February 14, 2000

Pentium II Xeon (chronological entry)

Introduced June 29, 1998 See main entry

Pentium III

Katmai 0.25 m process technology

o o o o o o o o o

Introduced February 26, 1999 Improved PII, i.e. P6-based core, now including Streaming SIMD Extensions (SSE) Number of transistors 9.5 million 512 KB bandwidth L2 External cache 242-pin Slot 1 SECC2 (Single Edge Contact cartridge 2) processor package System Bus clock rate 100 MHz, 133 MHz (B-models) Slot 1 Family 6 model 7 Variants

450, 500 MHz Introduced February 26, 1999 550 MHz Introduced May 17, 1999 600 MHz Introduced August 2, 1999 533, 600 MHz Introduced (133 MHz bus clock rate) September 27, 1999

Coppermine 0.18 m process technology

o o o o

Introduced October 25, 1999 Number of transistors 28.1 million 256 KB Advanced Transfer L2 Cache (Integrated) 242-pin Slot-1 SECC2 (Single Edge Contact cartridge 2) processor package, 370-pin FC-PGA (Flip-chip pin grid array) package

o o o o

System Bus clock rate 100 MHz (E-models), 133 MHz (EB models) Slot 1, Socket 370 Family 6 model 8 Variants

500 MHz (100 MHz bus clock rate) 533 MHz 550 MHz (100 MHz bus clock rate) 600 MHz 600 MHz (100 MHz bus clock rate) 650 MHz (100 MHz bus clock rate) Introduced October 25, 1999

16

667 MHz Introduced October 25, 1999 700 MHz (100 MHz bus clock rate) Introduced October 25, 1999 733 MHz Introduced October 25, 1999 750, 800 MHz (100 MHz bus clock rate) Introduced December 20, 1999 850 MHz (100 MHz bus clock rate) Introduced March 20, 2000 866 MHz Introduced March 20, 2000 933 MHz Introduced May 24, 2000 1000 MHz Introduced March 8, 2000 (Not widely available at time of release) 1100 MHz 1133 MHz (first version recalled, later re-released) 400, 450, 500 MHz (Mobile) Introduced October 25, 1999 600, 650 MHz (Mobile) Introduced January 18, 2000 700 MHz (Mobile) Introduced April 24, 2000 750 MHz (Mobile) Introduced June 19, 2000 800, 850 MHz (Mobile) Introduced September 25, 2000 900, 1000 MHz (Mobile) Introduced March 19, 2001

Tualatin 0.13 m process technology

o o o o o o o o o

Introduced July 2001 Number of transistors 28.1 million 32 KB L1 cache 256 KB or 512 KB Advanced Transfer L2 cache (Integrated) 370-pin FC-PGA2 (Flip-chip pin grid array) package 133 MHz system bus clock rate Socket 370 Family 6 model 11 Variants

1133 MHz (256 KB L2) 1133 MHz (512 KB L2) 1200 MHz 1266 MHz (512 KB L2) 1333 MHz 1400 MHz (512 KB L2)

Pentium II and III Xeon

PII Xeon

o

Variants

400 MHz Introduced June 29, 1998 450 MHz (512 KB L2 Cache) Introduced October 6, 1998 450 MHz (1 MB and 2 MB L2 Cache) Introduced January 5, 1999

PIII Xeon

o o o o o o o o o o

Introduced October 25, 1999 Number of transistors: 9.5 million at 0.25 m or 28 million at 0.18 m L2 cache is 256 KB, 1 MB, or 2 MB Advanced Transfer Cache (Integrated) Processor Package Style is Single Edge Contact Cartridge (S.E.C.C.2) or SC330 System Bus clock rate 133 MHz (256 KB L2 cache) or 100 MHz (1 2 MB L2 cache) System Bus Width 64 bit Addressable memory 64 GB Used in two-way servers and workstations (256 KB L2) or 4- and 8-way servers (1 2 MB L2) Family 6 model 10 Variants

500 MHz (0.25 m process) Introduced March 17, 1999

17

550 MHz (0.25 m process) Introduced August 23, 1999 600 MHz (0.18 m process, 256 KB L2 cache) Introduced October 25, 1999 667 MHz (0.18 m process, 256 KB L2 cache) Introduced October 25, 1999 733 MHz (0.18 m process, 256 KB L2 cache) Introduced October 25, 1999 800 MHz (0.18 m process, 256 KB L2 cache) Introduced January 12, 2000 866 MHz (0.18 m process, 256 KB L2 cache) Introduced April 10, 2000 933 MHz (0.18 m process, 256 KB L2 cache) 1000 MHz (0.18 m process, 256 KB L2 cache) Introduced August 22, 2000 700 MHz (0.18 m process, 1 2 MB L2 cache) Introduced May 22, 2000

Celeron (Pentium III Coppermine-based)

Coppermine-128, 0.18 m process technology

o o o o o o o o o

Introduced March, 2000 Streaming SIMD Extensions (SSE) Socket 370, FC-PGA processor package Number of transistors 28.1 million 66 MHz system bus clock rate, 100 MHz system bus clock rate from January 3, 2001 32 kB L1 cache 128 kB Advanced Transfer L2 cache Family 6 model 8 Variants

533 MHz 566 MHz 600 MHz 633, 667, 700 MHz Introduced June 26, 2000 733, 766 MHz Introduced November 13, 2000 800 MHz Introduced January 3, 2001 850 MHz Introduced April 9, 2001 900 MHz Introduced July 2, 2001 950, 1000, 1100 MHz Introduced August 31, 2001 550 MHz (Mobile) 600, 650 MHz (Mobile) Introduced June 19, 2000 700 MHz (Mobile) Introduced September 25, 2000 750 MHz (Mobile) Introduced March 19, 2001 800 MHz (Mobile) 850 MHz (Mobile) Introduced July 2, 2001 600 MHz (LV Mobile) 500 MHz (ULV Mobile) Introduced January 30, 2001 600 MHz (ULV Mobile)

XScale (chronological entry)

Introduced August 23, 2000 See main entry

Pentium 4 (not 4EE, 4E, 4F), Itanium, P4-based Xeon, Itanium 2 (chronological entries)

Introduced April 2000 July 2002

18

See main entries

Celeron (Pentium III Tualatin-based)

Tualatin Celeron 0.13 m process technology

o o o o o o

32 KB L1 cache 256 KB Advanced Transfer L2 cache 100 MHz system bus clock rate Socket 370 Family 6 model 11 Variants

1.0 GHz 1.1 GHz 1.2 GHz 1.3 GHz 1.4 GHz

Pentium M

Banias 0.13 m process technology

o o o o o o o o o o

Introduced March 2003 64 KB L1 cache 1 MB L2 cache (integrated) Based on Pentium III core, with SSE2 SIMD instructions and deeper pipeline Number of transistors 77 million Micro-FCPGA, Micro-FCBGA processor package Heart of the Intel mobile Centrino system 400 MHz Netburst-style system bus Family 6 model 9 Variants

900 MHz (Ultra low voltage) 1.0 GHz (Ultra low voltage) 1.1 GHz (Low voltage) 1.2 GHz (Low voltage) 1.3 GHz 1.4 GHz 1.5 GHz 1.6 GHz 1.7 GHz

Dothan 0.09 m (90 nm) process technology

o o o o o o o o

Introduced May 2004 2 MB L2 cache 140 million transistors Revised data prefetch unit 400 MHz Netburst-style system bus 21W TDP Family 6 model 13 Variants

1.00 GHz (Pentium M 723) (Ultra low voltage, 5W TDP) 1.10 GHz (Pentium M 733) (Ultra low voltage, 5W TDP) 1.20 GHz (Pentium M 753) (Ultra low voltage, 5W TDP) 1.30 GHz (Pentium M 718) (Low voltage, 10W TDP)

19

1.40 GHz (Pentium M 738) (Low voltage, 10W TDP) 1.50 GHz (Pentium M 758) (Low voltage, 10W TDP) 1.60 GHz (Pentium M 778) (Low voltage, 10W TDP) 1.40 GHz (Pentium M 710) 1.50 GHz (Pentium M 715) 1.60 GHz (Pentium M 725) 1.70 GHz (Pentium M 735) 1.80 GHz (Pentium M 745) 2.00 GHz (Pentium M 755) 2.10 GHz (Pentium M 765)

Dothan 533 0.09 m (90 nm) process technology

o o o

Introduced Q1 2005 Same as Dothan except with a 533 MHz NetBurst-style system bus and 27W TDP Variants

1.60 GHz (Pentium M 730) 1.73 GHz (Pentium M 740) 1.86 GHz (Pentium M 750) 2.00 GHz (Pentium M 760) 2.13 GHz (Pentium M 770) 2.26 GHz (Pentium M 780)

Stealey 0.09 m (90 nm) process technology

o o o

Introduced Q2 2007 512 KB L2, 3W TDP Variants

600 MHz (A100) 800 MHz (A110)

Celeron M

Banias-512 0.13 m process technology

o o o o o o o

Introduced March 2003 64 KB L1 cache 512 KB L2 cache (integrated) SSE2 SIMD instructions No SpeedStep technology, is not part of the 'Centrino' package Family 6 model 9 Variants

310 1.20 GHz 320 1.30 GHz 330 1.40 GHz 340 1.50 GHz

Dothan-1024 90 nm process technology

o o o o o

64 KB L1 cache 1 MB L2 cache (integrated) SSE2 SIMD instructions No SpeedStep technology, is not part of the 'Centrino' package Variants

350 1.30 GHz 350J 1.30 GHz, with Execute Disable bit 360 1.40 GHz 360J 1.40 GHz, with Execute Disable bit 370 1.50 GHz, with Execute Disable bit

20

Family 6, Model 13, Stepping 8[3]

380 1.60 GHz, with Execute Disable bit 390 1.70 GHz, with Execute Disable bit

Yonah-1024 65 nm process technology

o o o o o

64 KB L1 cache 1 MB L2 cache (integrated) SSE3 SIMD instructions, 533 MHz front-side bus, execute-disable bit No SpeedStep technology, is not part of the 'Centrino' package Variants

410 1.46 GHz 420 1.60 GHz, 423 1.06 GHz (ultra low voltage) 430 1.73 GHz 440 1.86 GHz 443 1.20 GHz (ultra low voltage) 450 2.00 GHz

Intel Core

Yonah 0.065 m (65 nm) process technology

o o o o o o o

Introduced January 2006 533/667 MHz front side bus 2 MB (Shared on Duo) L2 cache SSE3 SIMD instructions 31W TDP (T versions) Family 6, Model 14 Variants:

Intel Core Duo T2700 2.33 GHz Intel Core Duo T2600 2.16 GHz Intel Core Duo T2500 2 GHz Intel Core Duo T2450 2 GHz Intel Core Duo T2400 1.83 GHz Intel Core Duo T2300 1.66 GHz Intel Core Duo T2050 1.6 GHz Intel Core Duo T2300e 1.66 GHz Intel Core Duo T2080 1.73 GHz Intel Core Duo L2500 1.83 GHz (Low voltage, 15W TDP) Intel Core Duo L2400 1.66 GHz (Low voltage, 15W TDP) Intel Core Duo L2300 1.5 GHz (Low voltage, 15W TDP) Intel Core Duo U2500 1.2 GHz (Ultra low voltage, 9W TDP) Intel Core Solo T1350 1.86 GHz (533 FSB) Intel Core Solo T1300 1.66 GHz Intel Core Solo T1200 1.5 GHz [4]

Dual-Core Xeon LV

Sossaman 0.065 m (65 nm) process technology

o o o o o

Introduced March 2006 Based on Yonah core, with SSE3 SIMD instructions 667 MHz frontside bus 2 MB Shared L2 cache Variants

21

2.0 GHz

32-bit processors: NetBurst microarchitecture

Pentium 4

0.18 m process technology (1.40 and 1.50 GHz)

o o o o o o o

Introduced November 20, 2000 L2 cache was 256 KB Advanced Transfer Cache (Integrated) Processor Package Style was PGA423, PGA478 System Bus clock rate 400 MHz SSE2 SIMD Extensions Number of Transistors 42 million Used in desktops and entry-level workstations

0.18 m process technology (1.7 GHz)

o o

Introduced April 23, 2001 See the 1.4 and 1.5 chips for details

0.18 m process technology (1.6 and 1.8 GHz)

o o o o o

Introduced July 2, 2001 See 1.4 and 1.5 chips for details Core Voltage is 1.15 volts in Maximum Performance Mode; 1.05 volts in Battery Optimized Mode Power <1 watt in Battery Optimized Mode Used in full-size and then light mobile PCs

0.18 m process technology Willamette (1.9 and 2.0 GHz)

o o

Introduced August 27, 2001 See 1.4 and 1.5 chips for details

Family 15 model 1 Pentium 4 (2 GHz, 2.20 GHz)

o

Introduced January 7, 2002

Pentium 4 (2.4 GHz)

o

Introduced April 2, 2002

0.13 m process technology Northwood A (1.7, 1.8, 1.9, 2, 2.2, 2.4, 2.5, 2.6, 2.8(OEM),3.0(OEM) GHz)

o o o o

Improved branch prediction and other microcodes tweaks 512 KB integrated L2 cache Number of transistors 55 million 400 MHz system bus.

Family 15 model 2 0.13 m process technology Northwood B (2.26, 2.4, 2.53, 2.66, 2.8, 3.06 GHz)

o

533 MHz system bus. (3.06 includes Intel's hyper threading technology).

0.13 m process technology Northwood C (2.4, 2.6, 2.8, 3.0, 3.2, 3.4 GHz)

o o

800 MHz system bus (all versions include Hyper Threading) 6500 to 10000 MIPS

Itanium (chronological entry)

Introduced 2001 See main entry

Xeon

22

Official designation now Xeon, i.e. not "Pentium 4 Xeon" Xeon 1.4, 1.5, 1.7 GHz

o o o o o o

Introduced May 21, 2001 L2 cache was 256 KB Advanced Transfer Cache (Integrated) Processor Package Style was Organic Land Grid Array 603 (OLGA 603) System Bus clock rate 400 MHz SSE2 SIMD Extensions Used in high-performance and mid-range dual processor enabled workstations

Xeon 2.0 GHz and up to 3.6 GHz

o

Introduced September 25, 2001

Itanium 2 (chronological entry)

Introduced July 2002 See main entry

Mobile Pentium 4-M

0.13 m process technology 55 million transistors cache L2 512 KB BUS a 400 MHz Supports up to 1 GB of DDR 266 MHz Memory Supports ACPI 2.0 and APM 1.2 System Power Management 1.3 V 1.2 V (SpeedStep) Power: 1.2 GHz 20.8 W, 1.6 GHz 30 W, 2.6 GHz 35 W Sleep Power 5 W (1.2 V) Deeper Sleep Power = 2.9 W (1.0 V)

o o o o o o o o o o o

1.40 GHz 23 April 2002 1.50 GHz 23 April 2002 1.60 GHz 4 March 2002 1.70 GHz 4 March 2002 1.80 GHz 23 April 2002 1.90 GHz 24 June 2002 2.00 GHz 24 June 2002 2.20 GHz 16 September 2002 2.40 GHz 14 January 2003 2.50 GHz 16 April 2003 2.60 GHz 11 June 2003

Pentium 4 EE

Introduced September 2003 EE = "Extreme Edition" Built from the Xeon's "Gallatin" core, but with 2 MB cache-

Pentium 4E

23

Introduced February 2004 built on 0.09 m (90 nm) process technology Prescott (2.4A, 2.8, 2.8A, 3.0, 3.2, 3.4, 3.6, 3.8) 1 MB L2 cache 533 MHz system bus (2.4A and 2.8A only) Number of Transistors 125 million on 1 MB Models Number of Transistors 169 million on 2 MB Models 800 MHz system bus (all other models) Hyper-Threading support is only available on CPUs using the 800 MHz system bus. The processor's integer instruction pipeline has been increased from 20 stages to 31 stages, which theoretically allows for even greater bandwidth.

7500 to 11000 MIPS LGA 775 versions are in the 5xx series (32-bit) and 5x1 series (with Intel 64) The 6xx series has 2 MB L2 cache and Intel 64

Pentium 4F

Introduced Spring 2004 same core as 4E, "Prescott" 3.23.6 GHz starting with the D0 stepping of this processor, Intel 64 64-bit extensions has also been incorporated

64-bit processors: IA-64

New instruction set, not at all related to x86. Before the feature was eliminated (Montecito, July 2006) IA-64 processors supported 32-bit x86 in hardware, but slowly (see its 2001 market reception and 2006 architectural changes).[dubious discuss]

Itanium

Code name Merced Family 0x07 Released May 29, 2001 733 MHz and 800 MHz 2MB cache all recalled and replaced by Itanium-II

Itanium 2

Family 0x1F Released July 2002 900 MHz 1.6 GHz McKinley 900 MHz 1.5MB cache, Model 0x0 McKinley 1 GHz, 3MB cache, Model 0x0 Deerfield 1 GHz, 1.5MB cache, Model 0x1 Madison 1.3 GHz, 3MB cache, Model 0x1 Madison 1.4 GHz, 4MB cache, Model 0x1 Madison 1.5 GHz, 6MB cache, Model 0x1 Madison 1.67 GHz, 9MB cache, Model 0x1 Hondo 1.4 GHz, 4MB cache, dual core MCM, Model 0x1

64-bit processors: Intel 64 NetBurst microarchitecture

24

Intel Extended Memory 64 Technology Mostly compatible with AMD's AMD64 architecture Introduced Spring 2004, with the Pentium 4F (D0 and later P4 steppings)

Pentium 4F

Prescott-2M built on 0.09 m (90 nm) process technology 2.83.8 GHz (model numbers 6x0) Introduced February 20, 2005 Same features as Prescott with the addition of:o o o

2 MB cache Intel 64bit Enhanced Intel SpeedStep Technology (EIST)

Cedar Mill built on 0.065 m (65 nm) process technology 3.03.6 (model numbers 6x1) Introduced January 16, 2006 die shrink of Prescott-2M Same features as Prescott-2M Family 15 Model 4

Pentium D

Main article: List of Intel Pentium D microprocessors

Dual-core microprocessor No Hyper-Threading 800(4200) MHz front side bus LGA 775 (Socket T)

Smithfield 90 nm process technology (2.663.2 GHz)

o o o o o o o o o

Introduced May 26, 2005 2.663.2 GHz (model numbers 805840) Number of Transistors 230 million 1 MB 2 (non-shared, 2 MB total) L2 cache Cache coherency between cores requires communication over the FSB Performance increase of 60% over similarly clocked Prescott 2.66 GHz (533 MHz FSB) Pentium D 805 introduced December 2005 Contains 2x Prescott dies in one package Family 15 Model 4

Presler 65 nm process technology (2.83.6 GHz)

o o o o o

Introduced January 16, 2006 2.83.6 GHz (model numbers 915960) Number of Transistors 376 million 2 MB 2 (non-shared, 4 MB total) L2 cache Contains 2x Cedar Mill dies in one package

Pentium Extreme Edition

Dual-core microprocessor Enabled Hyper-Threading

25

800(4200) MHz front side bus

Smithfield 90 nm process technology (3.2 GHz)

o

Variants

Pentium 840 EE 3.20 GHz (2 1 MB L2)

Presler 65 nm process technology (3.46, 3.73)

o o

2 MB 2 (non-shared, 4 MB total) L2 cache Variants

Pentium 955 EE 3.46 GHz, 1066 MHz front side bus Pentium 965 EE 3.73 GHz, 1066 MHz front side bus

Xeon

Nocona

o

Introduced 2004

Irwindale

o

Introduced 2004

Cranford

o o

Introduced April 2005 MP version of Nocona

Potomac

o o

Introduced April 2005 Cranford with 8 MB of L3 cache

Paxville DP (2.8 GHz)

o o o o

Introduced October 10, 2005 Dual-core version of Irwindale, with 4 MB of L2 Cache (2 MB per core) 2.8 GHz 800 MT/s front side bus

Paxville MP 90 nm process (2.67 3.0 GHz)

o o o o o

Introduced November 1, 2005 Dual-Core Xeon 7000 series MP-capable version of Paxville DP 2 MB of L2 Cache (1 MB per core) or 4 MB of L2 (2 MB per core) 667 MT/s FSB or 800 MT/s FSB

Dempsey 65 nm process (2.67 3.73 GHz)

o o o o o o

Introduced May 23, 2006 Dual-Core Xeon 5000 series MP version of Presler 667 MT/s or 1066 MT/s FSB 4 MB of L2 Cache (2 MB per core) LGA 771 (Socket J).

Tulsa 65 nm process (2.5 3.4 GHz)

o

Introduced August 29, 2006

26

o o o

Dual-Core Xeon 7100-series Improved version of Paxville MP 667 MT/s or 800 MT/s FSB

64-bit processors: Intel 64 Core microarchitecture

Xeon

Woodcrest 65 nm process technology

o o o o o o o o o o

Server and Workstation CPU (SMP support for dual CPU system) Introduced June 26, 2006 Dual-Core Intel VT-x, multiple OS support EIST (Enhanced Intel SpeedStep Technology) in 5140, 5148LV, 5150, 5160 Execute Disable Bit TXT, enhanced security hardware extensions SSSE3 SIMD instructions iAMT2 (Intel Active Management Technology), remotely manage computers Variants

Xeon 5160 3.00 GHz (4 MB L2, 1333 MHz FSB, 80 W) Xeon 5150 2.66 GHz (4 MB L2, 1333 MHz FSB, 65 W) Xeon 5140 2.33 GHz (4 MB L2, 1333 MHz FSB, 65 W) Xeon 5130 2.00 GHz (4 MB L2, 1333 MHz FSB, 65 W) Xeon 5120 1.86 GHz (4 MB L2, 1066 MHz FSB, 65 W) Xeon 5110 1.60 GHz (4 MB L2, 1066 MHz FSB, 65 W) Xeon 5148LV 2.33 GHz (4 MB L2, 1333 MHz FSB, 40 W) Low Voltage Edition

Clovertown 65 nm process technology

o o o o o o o o o o

Server and Workstation CPU (SMP support for dual CPU system) Introduced December 13, 2006 Quad Core Intel VT-x, multiple OS support EIST (Enhanced Intel SpeedStep Technology) in E5365, L5335 Execute Disable Bit TXT, enhanced security hardware extensions SSSE3 SIMD instructions iAMT2 (Intel Active Management Technology), remotely manage computers Variants

Xeon X5355 2.66 GHz (24 MB L2, 1333 MHz FSB, 105 W) Xeon E5345 2.33 GHz (24 MB L2, 1333 MHz FSB, 80 W) Xeon E5335 2.00 GHz (24 MB L2, 1333 MHz FSB, 80 W) Xeon E5320 1.86 GHz (24 MB L2, 1066 MHz FSB, 65 W) Xeon E5310 1.60 GHz (24 MB L2, 1066 MHz FSB, 65 W) Xeon L5320 1.86 GHz (24 MB L2, 1066 MHz FSB, 50 W)-- Low Voltage Edition

Intel Core 2

Conroe 65 nm process technology

o o o

Desktop CPU (SMP support restricted to 2 CPUs) Two cores on one die Introduced July 27, 2006

27

o o o o o o o o o o

SSSE3 SIMD instructions Number of Transistors: 291 Million 64 KB of L1 cache per core (32+32 KB 8-way) Intel VT-x, multiple OS support TXT, enhanced security hardware extensions Execute Disable Bit EIST (Enhanced Intel SpeedStep Technology) iAMT2 (Intel Active Management Technology), remotely manage computers LGA 775 Variants

Core 2 Duo E6850 3.00 GHz (4 MB L2, 1333 MHz FSB) Core 2 Duo X6800 2.93 GHz (4 MB L2, 1066 MHz FSB) Core 2 Duo E6750 2.67 GHz (4 MB L2, 1333 MHz FSB) Core 2 Duo E6700 2.67 GHz (4 MB L2, 1066 MHz FSB) Core 2 Duo E6600 2.40 GHz (4 MB L2, 1066 MHz FSB) Core 2 Duo E6550 2.33 GHz (4 MB L2, 1333 MHz FSB) Core 2 Duo E6420 2.13 GHz (4 MB L2, 1066 MHz FSB) Core 2 Duo E6400 2.13 GHz (2 MB L2, 1066 MHz FSB) Core 2 Duo E6320 1.86 GHz (4 MB L2, 1066 MHz FSB) Family 6, Model 15, Stepping 6 Core 2 Duo E6300 1.86 GHz (2 MB L2, 1066 MHz FSB)

Conroe XE 65 nm process technology

o o o o o

Desktop Extreme Edition CPU (SMP support restricted to 2 CPUs) Introduced July 27, 2006 same features as Conroe LGA 775 Variants

Core 2 Extreme X6800 2.93 GHz (4 MB L2, 1066 MHz FSB)

Allendale 65 nm process technology

o o o o o o o o o o o

Desktop CPU (SMP support restricted to 2 CPUs) Two CPUs on one die Introduced January 21, 2007 SSSE3 SIMD instructions Number of Transistors 167 Million TXT, enhanced security hardware extensions Execute Disable Bit EIST (Enhanced Intel SpeedStep Technology) iAMT2 (Intel Active Management Technology), remotely manage computers LGA 775 Variants

Core 2 Duo E4700 2.60 GHz (2 MB L2, 800 MHz FSB) Core 2 Duo E4600 2.40 GHz (2 MB L2, 800 MHz FSB) Core 2 Duo E4500 2.20 GHz (2 MB L2, 800 MHz FSB) Core 2 Duo E4400 2.00 GHz (2 MB L2, 800 MHz FSB) Core 2 Duo E4300 1.80 GHz (2 MB L2, 800 MHz FSB) Family 6, Model 15, Stepping 2

Merom 65 nm process technology

o o o o

Mobile CPU (SMP support restricted to 2 CPUs) Introduced July 27, 2006 Family 6, Model 15 same features as Conroe

28

o o

Socket M / Socket P Variants

Core 2 Duo T7800 2.60 GHz (4 MB L2, 800 MHz FSB) (Santa Rosa platform) Core 2 Duo T7700 2.40 GHz (4 MB L2, 800 MHz FSB) Core 2 Duo T7600 2.33 GHz (4 MB L2, 667 MHz FSB) Core 2 Duo T7500 2.20 GHz (4 MB L2, 800 MHz FSB) Core 2 Duo T7400 2.16 GHz (4 MB L2, 667 MHz FSB) Core 2 Duo T7300 2.00 GHz (4 MB L2, 800 MHz FSB) Core 2 Duo T7250 2.00 GHz (2 MB L2, 800 MHz FSB) Core 2 Duo T7200 2.00 GHz (4 MB L2, 667 MHz FSB) Core 2 Duo T7100 1.80 GHz (2 MB L2, 800 MHz FSB) Core 2 Duo T5600 1.83 GHz (2 MB L2, 667 MHz FSB) Family 6, Model 15, Stepping 6 Core 2 Duo T5550 1.83 GHz (2 MB L2, 667 MHz FSB, no VT) Core 2 Duo T5500 1.66 GHz (2 MB L2, 667 MHz FSB, no VT) Core 2 Duo T5470 1.60 GHz (2 MB L2, 800 MHz FSB, no VT) Core 2 Duo T5450 1.66 GHz (2 MB L2, 667 MHz FSB, no VT) Core 2 Duo T5300 1.73 GHz (2 MB L2, 533 MHz FSB, no VT) Core 2 Duo T5270 1.40 GHz (2 MB L2, 800 MHz FSB, no VT) Core 2 Duo T5250 1.50 GHz (2 MB L2, 667 MHz FSB, no VT) Core 2 Duo T5200 1.60 GHz (2 MB L2, 533 MHz FSB, no VT) Core 2 Duo L7500 1.60 GHz (4 MB L2, 800 MHz FSB) (Low Voltage) Core 2 Duo L7400 1.50 GHz (4 MB L2, 667 MHz FSB) (Low Voltage) Core 2 Duo L7300 1.40 GHz (4 MB L2, 800 MHz FSB) (Low Voltage) Core 2 Duo L7200 1.33 GHz (4 MB L2, 667 MHz FSB) (Low Voltage) Core 2 Duo U7700 1.33 GHz (2 MB L2, 533 MHz FSB) (Ultra Low Voltage) Core 2 Duo U7600 1.20 GHz (2 MB L2, 533 MHz FSB) (Ultra Low Voltage) Core 2 Duo U7500 1.06 GHz (2 MB L2, 533 MHz FSB) (Ultra Low Voltage)

Kentsfield 65 nm process technology

o o o o o o o o

Two dual-core cpu dies in one package. Desktop CPU Quad Core (SMP support restricted to 4 CPUs) Introduced December 13, 2006 same features as Conroe but with 4 CPU Cores Number of Transistors 586 Million LGA 775 Family 6, Model 15, Stepping 11 Variants

Core 2 Extreme QX6850 3 GHz (24 MB L2 Cache, 1333 MHz FSB) Core 2 Extreme QX6800 2.93 GHz (24 MB L2 Cache, 1066 MHz FSB) (April 9, 2007) Core 2 Extreme QX6700 2.66 GHz (24 MB L2 Cache, 1066 MHz FSB) (November 14, 2006) Core 2 Quad Q6700 2.66 GHz (24 MB L2 Cache, 1066 MHz FSB) (July 22, 2007) Core 2 Quad Q6600 2.40 GHz (24 MB L2 Cache, 1066 MHz FSB) (January 7, 2007)

Wolfdale 45 nm process technology

o o

Die shrink of Conroe Same features as Conroe with the addition of:

50% more cache, 6 MB as opposed to 4 MB Intel Trusted Execution Technology SSE4 SIMD instructions

o o

Number of Transistors 410 Million Variants

Core 2 Duo E8600 3.33 GHz (6 MB L2, 1333 MHz FSB)

29

Core 2 Duo E8500 3.16 GHz (6 MB L2, 1333 MHz FSB) Core 2 Duo E8400 3.00 GHz (6 MB L2, 1333 MHz FSB) Core 2 Duo E8300 2.83 GHz (6 MB L2, 1333 MHz FSB) Core 2 Duo E8200 2.66 GHz (6 MB L2, 1333 MHz FSB) Core 2 Duo E8190 2.66 GHz (6 MB L2, 1333 MHz FSB, no TXT, no VT)

Wolfdale-3M 45 nm process technology

o o

Intel Trusted Execution Technology Variants

Core 2 Duo E7600 3.06 GHz (3 MB L2, 1066 MHz FSB) Core 2 Duo E7500 2.93 GHz (3 MB L2, 1066 MHz FSB) Core 2 Duo E7400 2.80 GHz (3 MB L2, 1066 MHz FSB) Core 2 Duo E7300 2.66 GHz (3 MB L2, 1066 MHz FSB) Core 2 Duo E7200 2.53 GHz (3 MB L2, 1066 MHz FSB)

Yorkfield 45 nm process technology

o o o o o o

Quad core CPU Die shrink of Kentsfield Contains 2x Wolfdale dual core dies in one package Same features as Wolfdale Number of Transistors 820 Million Variants

Core 2 Extreme QX9770 3.20 GHz (26 MB L2, 1600 MHz FSB) Core 2 Extreme QX9650 3.00 GHz (26 MB L2, 1333 MHz FSB) Core 2 Quad Q9650 3 GHz (26 MB L2, 1333 MHz FSB) Core 2 Quad Q9550 2.83 GHz (26 MB L2, 1333 MHz FSB, 95W TDP) Core 2 Quad Q9550s 2.83 GHz (26 MB L2, 1333 MHz FSB, 65W TDP) Core 2 Quad Q9450 2.66 GHz (26 MB L2, 1333 MHz FSB, 95W TDP) Core 2 Quad Q9505 2.83 GHz (23 MB L2, 1333 MHz FSB, 95W TDP) Core 2 Quad Q9505s 2.83 GHz (23 MB L2, 1333 MHz FSB, 65W TDP) Core 2 Quad Q9500 2.83 GHz (23 MB L2, 1333 MHz FSB, 95W TDP, no TXT) Core 2 Quad Q9400 2.66 GHz (23 MB L2, 1333 MHz FSB, 95W TDP) Core 2 Quad Q9400s 2.66 GHz (23 MB L2, 1333 MHz FSB, 65W TDP) Core 2 Quad Q9300 2.50 GHz (23 MB L2, 1333 MHz FSB, 95W TDP) Core 2 Quad Q8400 2.66 GHz (22 MB L2, 1333 MHz FSB, 95W TDP) Core 2 Quad Q8400s 2.66 GHz (22 MB L2, 1333 MHz FSB, 65W TDP) Core 2 Quad Q8300 2.50 GHz (22 MB L2, 1333 MHz FSB, 95W TDP) Core 2 Quad Q8300s 2.50 GHz (22 MB L2, 1333 MHz FSB, 65W TDP) Core 2 Quad Q8200 2.33 GHz (22 MB L2, 1333 MHz FSB, 95W TDP) Core 2 Quad Q8200s 2.33 GHz (22 MB L2, 1333 MHz FSB, 65W TDP) Core 2 Quad Q7600 2.70 GHz (21 MB L2, 800 MHz FSB, no SSE4) (no Q7600 at http://ark.intel.com/ProductCollection.aspx?familyID=28398)

Intel Core2 Quad Mobile Processor Family 45 nm process technology

o o

Quad core CPU Variants

Core 2 Quad Q9100 2.26 GHz (26 MB L2, 1066 MHz FSB, 45W TDP) Core 2 Quad Q9000 2.00 GHz (23 MB L2, 1066 MHz FSB, 45W TDP)

Pentium Dual Core

30

Allendale 65 nm process technology

o o o o o o o o o

Desktop CPU (SMP support restricted to 2 CPUs) Two cores on one die Introduced January 21, 2007 SSSE3 SIMD instructions Number of Transistors 167 Million TXT, enhanced security hardware extensions Execute Disable Bit EIST (Enhanced Intel SpeedStep Technology) Variants

Intel Pentium E2220 2.40 GHz (1 MB L2, 800 MHz FSB) Intel Pentium E2200 2.20 GHz (1 MB L2, 800 MHz FSB) Intel Pentium E2180 2.00 GHz (1 MB L2, 800 MHz FSB) Intel Pentium E2160 1.80 GHz (1 MB L2, 800 MHz FSB) Intel Pentium E2140 1.60 GHz (1 MB L2, 800 MHz FSB)

Wolfdale-3M 45 nm process technology

o o o o o o o o o o o

Intel Pentium E6800 3.33 GHz (2 MB L2,1066 MHz FSB) Intel Pentium E6700 3.20 GHz (2 MB L2,1066 MHz FSB) Intel Pentium E6600 3.06 GHz (2 MB L2,1066 MHz FSB) Intel Pentium E6500 2.93 GHz (2 MB L2,1066 MHz FSB) Intel Pentium E6300 2.80 GHz (2 MB L2,1066 MHz FSB) Intel Pentium E5700 3.00 GHz (2 MB L2, 800 MHz FSB) Intel Pentium E5500 2.80 GHz (2 MB L2, 800 MHz FSB) Intel Pentium E5400 2.70 GHz (2 MB L2, 800 MHz FSB) Intel Pentium E5300 2.60 GHz (2 MB L2, 800 MHz FSB) Intel Pentium E5200 2.50 GHz (2 MB L2, 800 MHz FSB) Intel Pentium E2210 2.20 GHz (1 MB L2, 800 MHz FSB)

Celeron

Allendale 65 nm process technology

o

Variants

Intel Celeron E1600 2.40 GHz (512 KB L2, 800 MHz FSB) Intel Celeron E1500 2.20 GHz (512 KB L2, 800 MHz FSB) Intel Celeron E1400 2.00 GHz (512 KB L2, 800 MHz FSB) Intel Celeron E1300 1.80 GHz (512 KB L2, 800 MHz FSB) (Exist?) Intel Celeron E1200 1.60 GHz (512 KB L2, 800 MHz FSB)

Wolfdale-3M 45 nm process technology

o

Variants

Intel Celeron E3500 2.70 GHz (1 MB L2, 800 MHz FSB) Intel Celeron E3400 2.60 GHz (1 MB L2, 800 MHz FSB) Intel Celeron E3300 2.50 GHz (1 MB L2, 800 MHz FSB) Intel Celeron E3200 2.40 GHz (1 MB L2, 800 MHz FSB)

Conroe-L 65 nm process technology

o

Variants

Intel Celeron 450 2.20 GHz (512 KB L2, 800 MHz FSB) Intel Celeron 440 2.00 GHz (512 KB L2, 800 MHz FSB) Intel Celeron 430 1.80 GHz (512 KB L2, 800 MHz FSB) Intel Celeron 420 1.60 GHz (512 KB L2, 800 MHz FSB) Intel Celeron 220 1.20 GHz (512 KB L2, 533 MHz FSB)

Conroe-CL 65 nm process technology

31

o o

LGA 771 package Variants

Intel Celeron 445 1.87 GHz (512 KB L2, 1066 MHz FSB)

Celeron M

Merom-L 65 nm process technology

o o o o o

64 KB L1 cache 1 MB L2 cache (integrated) SSE3 SIMD instructions, 533 MHz front-side bus, execute-disable bit, 64-bit No SpeedStep technology, is not part of the 'Centrino' package Variants

520 1.60 GHz 530 1.73 GHz 540 1.86 GHz 550 2.00 GHz 560 - 2.13 GHz

32-bit processors: Intel 32 Intel Atom

TODO: http://ark.intel.com/ProductCollection.aspx?familyId=29035

64-bit processors: Intel 64 Nehalem microarchitecture

Intel Pentium

Clarkdale 32 nm process technology

o o o o o o o

2 physical cores/2 threads 3 MB L3 cache Introduced January 2010 Socket 1156 LGA 2-channels DDR3 Integrated HD GPU Variants

G6950 - 2.8 GHz (No HyperThreading)[5] G6960 - 2.933 GHz (No HyperThreading)

Core i3

Clarkdale 32 nm process technology

o o o o o o o o o

2 physical cores/4 threads 64 Kb L1 cache 512 Kb L2 cache 4 MB L3 cache Introduced January, 2010 Socket 1156 LGA 2-channels DDR3 Integrated HD GPU Variants

530 2.93 GHz Hyper-Threading 540 3.06 GHz Hyper-Threading

32

550 3.2 GHz Hyper-Threading 560 3.33 GHz Hyper-Threading

Core i5

Lynnfield 45 nm process technology

o o o o o o o o o

4 physical cores 32+32 Kb (per core) L1 cache 256 Kb (per core) L2 cache 8 MB common L3 cache Introduced September 8, 2009 Family 6 Model E (Ext. Model 1E) Socket 1156 LGA 2-channels DDR3 Variants

750S 2.40 GHz/3.20 GHz Turbo Boost 750 2.66 GHz/3.20 GHz Turbo Boost 760 2.80 GHz/3.33 GHz Turbo Boost

Clarkdale 32 nm process technology

o o o o o o o o o o

2 physical cores/4 threads 64 Kb L1 cache 512 Kb L2 cache 4 MB L3 cache Introduced January, 2010 Socket 1156 LGA 2-channels DDR3 Integrated HD GPU AES Support Variants

650/655K 3.2 GHz Hyper-Threading Turbo Boost 660/661 3.33 GHz Hyper-Threading Turbo Boost 670 3.46 GHz Hyper-Threading Turbo Boost 680 3.60 GHz Hyper-Threading Turbo Boost

Core i7

Bloomfield 45 nm process technology

o o o o o o o o o o o o

4 physical cores 256 KB L2 cache 8 MB L3 cache Front side bus replaced with QuickPath up to 6.4GT/s Hyper-Threading is again included. This had previously been removed at the introduction of Core line 781 million transistors Intel Turbo Boost Technology TDP 130W Introduced November 17, 2008 Socket 1366 LGA 3-channels DDR3 Variants

975 (extreme edition) 3.33 GHz/3.60 GHz Turbo Boost

33

965 (extreme edition) 3.20 GHz/3.46 GHz Turbo Boost 960 - 3.20 GHz/3.46 GHz Turbo Boost 950 3.06 GHz/3.33 GHz Turbo Boost 940 2.93 GHz/3.20 GHz Turbo Boost 930 2.80 GHz/3.06 GHz Turbo Boost 920 2.66 GHz/2.93 GHz Turbo Boost

Lynnfield 45 nm process technology

o o o o o o o o o

4 physical cores 256 KB L2 cache 8 MB L3 cache No QuickPath, instead compatible with slower DMI interface Hyper-Threading is included Introduced September 8, 2009 Socket 1156 LGA 2-channels DDR3 Variants

880 3.06 GHz/3.73 GHz Turbo Boost (TDP 95W) 870/875K 2.93 GHz/3.60 GHz Turbo Boost (TDP 95W) 870S 2.67 GHz/3.60 GHz Turbo Boost (TDP 82W) 860 2.80 GHz/3.46 GHz Turbo Boost (TDP 95W) 860S 2.53 GHz/3.46 GHz Turbo Boost (TDP 82W)

TODO: Westmere

Gulftown 32 nm process technology

o o o o o o o o o o

6 physical cores 256 KB L2 cache 12 MB L3 cache Front side bus replaced with QuickPath up to 6.4GT/s Hyper-Threading is included Intel Turbo Boost Technology Socket 1366 LGA TDP 130W Introduced 16 March 2010 Variants

990X Extreme Edition - 3.46 GHz/3.73 GHz Turbo Boost 980X Extreme Edition - 3.33 GHz/3.60 GHz Turbo Boost 970 - 3.20 GHz/3.46 GHz Turbo Boost

Intel Core i7 Mobile Processor Family 45 nm process technology

o o o o

4 physical cores Hyper-Threading is included Intel Turbo Boost Technology Variants

940XM Extreme Edition - 2.13 GHz/3.33 GHz Turbo Boost (8 MB L3, TDP 55W) 920XM Extreme Edition - 2.00 GHz/3.20 GHz Turbo Boost (8 MB L3, TDP 55W) 840QM - 1.86 GHz/3.20 GHz Turbo Boost (8 MB L3, TDP 45W) 820QM - 1.73 GHz/3.06 GHz Turbo Boost (8 MB L3, TDP 45W) 740QM - 1.73 GHz/2.93 GHz Turbo Boost (6 MB L3, TDP 45W) 720QM - 1.60 GHz/2.80 GHz Turbo Boost (6 MB L3, TDP 45W)

Xeon

34

Gainestown 45 nm process technology

o o o o o o o o

Same processor dies as Bloomfield 256 KB L2 cache 8 MB L3 cache, 4MB may be disabled QuickPath up to 6.4GT/s Hyper-Threading is included in some models 781 million transistors Introduced March 29, 2009 Variants

W5590, W5580, X5570, X5560, X5550, E5540, E5530, L5530, E5520, L5520, L5518 4 Cores, 8 MB L3 cache, HT

E5506, L5506, E5504 4 cores, 4 MB L3 cache, no HT L5508, E5502, E5502 2 cores, 4 MB L3 cache, no HT

35

Das könnte Ihnen auch gefallen

- Microprocessors & their Operating Systems: A Comprehensive Guide to 8, 16 & 32 Bit Hardware, Assembly Language & Computer ArchitectureVon EverandMicroprocessors & their Operating Systems: A Comprehensive Guide to 8, 16 & 32 Bit Hardware, Assembly Language & Computer ArchitectureBewertung: 1 von 5 Sternen1/5 (1)

- List of Intel MicroprocessorsDokument61 SeitenList of Intel Microprocessorsfireball993Noch keine Bewertungen

- Intel CpusDokument37 SeitenIntel Cpus我叫政揚UwUNoch keine Bewertungen

- List of Intel Microprocessors: Participate in The World's Largest Photo Competition and Help Improve Wikipedia!Dokument52 SeitenList of Intel Microprocessors: Participate in The World's Largest Photo Competition and Help Improve Wikipedia!Atul YadavNoch keine Bewertungen

- The Evolution of Microprocessor From 4-Bits To 64-Bits. (Info-Graphics)Dokument43 SeitenThe Evolution of Microprocessor From 4-Bits To 64-Bits. (Info-Graphics)Abhi Sharma100% (1)

- Introduction To 8086Dokument91 SeitenIntroduction To 8086sayyanNoch keine Bewertungen

- Intel 4004Dokument2 SeitenIntel 4004Johnedel RosalesNoch keine Bewertungen

- Intel 8086 Microprocessor FamilyDokument3 SeitenIntel 8086 Microprocessor FamilyMusabbir Adnan TamimNoch keine Bewertungen

- MicroprocessorDokument12 SeitenMicroprocessorMishalNoch keine Bewertungen

- INTEL MicroprocessorDokument75 SeitenINTEL MicroprocessorFrank MosesNoch keine Bewertungen

- EC6504 Microprocessor and Microcontroller Lecture Notes All 5 UnitsDokument633 SeitenEC6504 Microprocessor and Microcontroller Lecture Notes All 5 Unitsgokulchandru82% (22)

- Intel Microprocessor Chapter 01Dokument86 SeitenIntel Microprocessor Chapter 01Muhammad AwaisNoch keine Bewertungen

- x-86 FamilyDokument14 Seitenx-86 FamilyPrince VegetaNoch keine Bewertungen

- Microprocessor Architectures: 1.1 Intel 1.2 MotorolaDokument14 SeitenMicroprocessor Architectures: 1.1 Intel 1.2 MotorolabharadwajrohanNoch keine Bewertungen

- Chapter 1 Part1 PDFDokument49 SeitenChapter 1 Part1 PDFtesfayebbNoch keine Bewertungen

- Unit - I: Department of Ece 1Dokument11 SeitenUnit - I: Department of Ece 1Su YeeNoch keine Bewertungen

- EE AC10 IntroductionDokument6 SeitenEE AC10 IntroductionJosh'z LlamesNoch keine Bewertungen

- Micro Controller Archtecture ProgrammingDokument94 SeitenMicro Controller Archtecture ProgrammingyayavaramNoch keine Bewertungen

- Introduction To Microprocessor & MicrocomputersDokument33 SeitenIntroduction To Microprocessor & MicrocomputersDileepmk85Noch keine Bewertungen

- Full MPMCDokument632 SeitenFull MPMCsujaganesan2009Noch keine Bewertungen

- Features of 8086 MicroprocessorDokument6 SeitenFeatures of 8086 MicroprocessoradityafirodaNoch keine Bewertungen

- Microapps/ Part 2-Bus Width: PIC 8-BIT (PIC10F206) FeaturesDokument5 SeitenMicroapps/ Part 2-Bus Width: PIC 8-BIT (PIC10F206) FeaturesAkinwumi OluwatosinNoch keine Bewertungen

- ARCHITECHTURE of 8085Dokument35 SeitenARCHITECHTURE of 8085Aakash GargNoch keine Bewertungen

- Unit 4 Introduction To Microcontroller 8051aDokument105 SeitenUnit 4 Introduction To Microcontroller 8051anitishNoch keine Bewertungen

- MP QabankDokument81 SeitenMP QabankPreethamkumarms PreethamNoch keine Bewertungen

- The X86 Microprocessor: ObjectivesDokument32 SeitenThe X86 Microprocessor: Objectivespapikhu36100% (4)

- MicropDokument5 SeitenMicropNaza RenkoNoch keine Bewertungen

- 8085 MicroprocessorDokument16 Seiten8085 MicroprocessorVinay FelixNoch keine Bewertungen

- Pc-Ee 602Dokument19 SeitenPc-Ee 602Koustav SahaNoch keine Bewertungen

- Microprocessor Engineering PDFDokument68 SeitenMicroprocessor Engineering PDFumairNoch keine Bewertungen

- Introduction To Microprocessors: SubtopicsDokument4 SeitenIntroduction To Microprocessors: SubtopicsJimboy RengelNoch keine Bewertungen

- U 4Dokument19 SeitenU 4AkankshaNoch keine Bewertungen

- 4thsem Microprocessor Notes PDFDokument148 Seiten4thsem Microprocessor Notes PDFVishal SharmaNoch keine Bewertungen

- Microprocessor, Microcomputer and Assembly LanguageDokument48 SeitenMicroprocessor, Microcomputer and Assembly LanguageKristine AbanadorNoch keine Bewertungen

- Module 4 - CODokument10 SeitenModule 4 - COAnnabelleNoch keine Bewertungen

- MicroprocessorsDokument25 SeitenMicroprocessorsMohammad ArifNoch keine Bewertungen

- MM Module1 Cse Notes PDFDokument56 SeitenMM Module1 Cse Notes PDFPrajwal S MNoch keine Bewertungen

- Lesson 1 - Evolution of Microprocessor PDFDokument59 SeitenLesson 1 - Evolution of Microprocessor PDFFrancis del RosarioNoch keine Bewertungen

- The Intel Microprocessors: Architecture, Programming, and Interfacing - 6 Ed.Dokument75 SeitenThe Intel Microprocessors: Architecture, Programming, and Interfacing - 6 Ed.Suhas GhantaNoch keine Bewertungen

- Evolution of MicroprocessorsDokument22 SeitenEvolution of MicroprocessorsGoutham KrishNoch keine Bewertungen

- Chapter 1Dokument52 SeitenChapter 1mtnkhNoch keine Bewertungen

- Microprocessor vs. MicrocontrollersDokument53 SeitenMicroprocessor vs. MicrocontrollersArgie Omaga HuindaNoch keine Bewertungen

- The X86 Microprocessor & Alp: Microprocessors and MicrocontrollersDokument56 SeitenThe X86 Microprocessor & Alp: Microprocessors and MicrocontrollersNaveen NNoch keine Bewertungen

- Lecture 8Dokument103 SeitenLecture 8Akshaya ZantyeNoch keine Bewertungen

- MM Module1 CseDokument137 SeitenMM Module1 CseAnonymous ivcUHwjChENoch keine Bewertungen

- What Is RouterboardDokument35 SeitenWhat Is Routerboardnic123456456Noch keine Bewertungen

- The Intel 8086 Processor: Josh Broome Dave Overstrom Jonathan Kagarise Christopher LindsayDokument14 SeitenThe Intel 8086 Processor: Josh Broome Dave Overstrom Jonathan Kagarise Christopher LindsayKim S KevohNoch keine Bewertungen

- Advanced Computer Architecture (ACA) /lecture: LV64-446, Module MV5.1Dokument101 SeitenAdvanced Computer Architecture (ACA) /lecture: LV64-446, Module MV5.1fahadned5717Noch keine Bewertungen

- Mpi Unit 1Dokument22 SeitenMpi Unit 1sree ramyaNoch keine Bewertungen

- and Pentium MicroprocessorsDokument37 Seitenand Pentium Microprocessorsgayathrishiv91100% (1)

- RB 411 ArDokument1 SeiteRB 411 ArHoa Tong DucNoch keine Bewertungen

- Arif MP Assig.Dokument25 SeitenArif MP Assig.Satyam KumarNoch keine Bewertungen

- MPMC Mod-1Dokument32 SeitenMPMC Mod-1Syeda AfreenNoch keine Bewertungen

- 8086Dokument33 Seiten8086navydevilzNoch keine Bewertungen

- Microprocessor and Assembly Language: LECTURE-3-THE 80X86 MicroprocessorDokument47 SeitenMicroprocessor and Assembly Language: LECTURE-3-THE 80X86 MicroprocessorIqraNoch keine Bewertungen

- MicroproprocessorsDokument28 SeitenMicroproprocessorsDhealine JusayanNoch keine Bewertungen

- Unit-3 MicroprocessorDokument32 SeitenUnit-3 MicroprocessorWhite chilliesNoch keine Bewertungen

- MicroprocessorDokument212 SeitenMicroprocessorraji30Noch keine Bewertungen

- 4Bcs504: Microprocessors: Module-I: IntroductionDokument60 Seiten4Bcs504: Microprocessors: Module-I: IntroductionDr. Parameswaran TNoch keine Bewertungen

- Windows Server 2003Dokument4 SeitenWindows Server 2003Lissa JusohNoch keine Bewertungen

- Windows Server 2003Dokument4 SeitenWindows Server 2003Lissa JusohNoch keine Bewertungen

- Windows Server 2003Dokument4 SeitenWindows Server 2003Lissa JusohNoch keine Bewertungen

- Windows Server 2003Dokument4 SeitenWindows Server 2003Lissa JusohNoch keine Bewertungen

- Dynamic Host Configuration Protocol - 1Dokument34 SeitenDynamic Host Configuration Protocol - 1Lissa JusohNoch keine Bewertungen

- Chapter 1 ServerDokument5 SeitenChapter 1 ServerLissa JusohNoch keine Bewertungen

- Service Manual: Viewsonic Vp2030B-1Dokument83 SeitenService Manual: Viewsonic Vp2030B-1MikhailNoch keine Bewertungen

- EM63B165TS - Rev 2.0Dokument53 SeitenEM63B165TS - Rev 2.0silva_marcosrNoch keine Bewertungen

- 5S - Excellence Assessment PDFDokument2 Seiten5S - Excellence Assessment PDFAshokNoch keine Bewertungen

- TDB013 ManualDokument9 SeitenTDB013 ManualKALILNoch keine Bewertungen

- PLC BasicsDokument20 SeitenPLC BasicsTalha_Gujjar_4662Noch keine Bewertungen

- Altezza Auto Mirror ClosureDokument7 SeitenAltezza Auto Mirror ClosureChard CharlesNoch keine Bewertungen

- Real Time Audio Signal Processing SystemtDokument24 SeitenReal Time Audio Signal Processing SystemtradhikasontakayNoch keine Bewertungen

- Multiscan Maintance Vs - (Espanish)Dokument22 SeitenMultiscan Maintance Vs - (Espanish)Javier Flores100% (2)

- Installing WinFWDCal Version 2Dokument1 SeiteInstalling WinFWDCal Version 2German Cruz RNoch keine Bewertungen

- BGA Rework Station User Manual: Beijing TECHNICAN CO.,LtdDokument18 SeitenBGA Rework Station User Manual: Beijing TECHNICAN CO.,LtdAlterpc PcNoch keine Bewertungen

- Akai 1420 1421 2020 2021 2120 2121 Finlux mp2 SCH PDFDokument9 SeitenAkai 1420 1421 2020 2021 2120 2121 Finlux mp2 SCH PDFJose LuisNoch keine Bewertungen

- Numerical Methods in Sci and EngDokument109 SeitenNumerical Methods in Sci and EngAshokan KelothNoch keine Bewertungen

- Fujitsu Lifebook Ah530 (Quanta FH5 Discrete)Dokument42 SeitenFujitsu Lifebook Ah530 (Quanta FH5 Discrete)Artur Schmidt0% (1)

- DaVinci Resolve 12 Configuration GuideDokument68 SeitenDaVinci Resolve 12 Configuration GuideexportcompNoch keine Bewertungen

- Subaru Eh Engines Eh36 Eh41 PartsDokument28 SeitenSubaru Eh Engines Eh36 Eh41 PartsMutu DanielNoch keine Bewertungen

- ORION NJE 4000 Non Linear Junction Detector Manual PDFDokument35 SeitenORION NJE 4000 Non Linear Junction Detector Manual PDFWaranNoch keine Bewertungen

- Plano Maquina de Bloques CetaramDokument17 SeitenPlano Maquina de Bloques CetaramLuis Ollarves100% (1)

- Qui Robinez, StrengthDokument3 SeitenQui Robinez, StrengthNikolasMavresisNoch keine Bewertungen

- Linux Command LineDokument56 SeitenLinux Command LinePranesh SathyanarayanNoch keine Bewertungen

- Manufacturing Equipment: Industrial Robotics - Introduction Industrial Robotics - IntroductionDokument42 SeitenManufacturing Equipment: Industrial Robotics - Introduction Industrial Robotics - IntroductionpiyushaaquaNoch keine Bewertungen

- Rakesh Kumar Kardam: - Filter H (T) Y (T) S (T) +N (T)Dokument6 SeitenRakesh Kumar Kardam: - Filter H (T) Y (T) S (T) +N (T)Deepak SankhalaNoch keine Bewertungen

- Mikroc Dspic Manual v100 PDFDokument782 SeitenMikroc Dspic Manual v100 PDFJezreel Martinez GonzalezNoch keine Bewertungen

- Manual ENG Dell Wireless Mouse Wm126Dokument16 SeitenManual ENG Dell Wireless Mouse Wm126kuttanmolutyNoch keine Bewertungen

- E 50Dokument71 SeitenE 50Ruído AudiovisuaisNoch keine Bewertungen

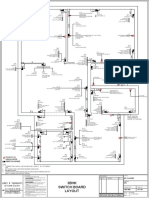

- Switch Board Layout Plan (MR - Dalbeer)Dokument1 SeiteSwitch Board Layout Plan (MR - Dalbeer)Vipin chandraNoch keine Bewertungen

- Xl4600 UserDokument27 SeitenXl4600 UserJoško ListešNoch keine Bewertungen

- Mca2010 SLM Unit 01Dokument15 SeitenMca2010 SLM Unit 01amritrathourNoch keine Bewertungen

- FOR Approval Specification: 32.0" Wxga TFT LCD TitleDokument29 SeitenFOR Approval Specification: 32.0" Wxga TFT LCD TitleVenera Segunda ManoNoch keine Bewertungen

- Aa Lisa SpecificationDokument19 SeitenAa Lisa SpecificationBartek BanterNoch keine Bewertungen

- 7ss60xx Manual A3 V031101 en PDFDokument136 Seiten7ss60xx Manual A3 V031101 en PDFcc_bauNoch keine Bewertungen

- CompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)Von EverandCompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)Bewertung: 5 von 5 Sternen5/5 (1)

- Unlock Any Roku Device: Watch Shows, TV, & Download AppsVon EverandUnlock Any Roku Device: Watch Shows, TV, & Download AppsNoch keine Bewertungen

- Computer Science: A Concise IntroductionVon EverandComputer Science: A Concise IntroductionBewertung: 4.5 von 5 Sternen4.5/5 (14)

- Chip War: The Quest to Dominate the World's Most Critical TechnologyVon EverandChip War: The Quest to Dominate the World's Most Critical TechnologyBewertung: 4.5 von 5 Sternen4.5/5 (227)

- Chip War: The Fight for the World's Most Critical TechnologyVon EverandChip War: The Fight for the World's Most Critical TechnologyBewertung: 4.5 von 5 Sternen4.5/5 (82)

- CompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Von EverandCompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Bewertung: 5 von 5 Sternen5/5 (2)

- iPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XVon EverandiPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XBewertung: 3 von 5 Sternen3/5 (2)

- Hacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxVon EverandHacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxNoch keine Bewertungen

- Amazon Web Services (AWS) Interview Questions and AnswersVon EverandAmazon Web Services (AWS) Interview Questions and AnswersBewertung: 4.5 von 5 Sternen4.5/5 (3)

- iPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsVon EverandiPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsBewertung: 5 von 5 Sternen5/5 (1)

- How to Jailbreak Roku: Unlock Roku, Roku Stick, Roku Ultra, Roku Express, Roku TV with Kodi Step by Step GuideVon EverandHow to Jailbreak Roku: Unlock Roku, Roku Stick, Roku Ultra, Roku Express, Roku TV with Kodi Step by Step GuideBewertung: 1 von 5 Sternen1/5 (1)

- Programming with STM32: Getting Started with the Nucleo Board and C/C++Von EverandProgramming with STM32: Getting Started with the Nucleo Board and C/C++Bewertung: 3.5 von 5 Sternen3.5/5 (3)

- iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]Von EverandiPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]Bewertung: 5 von 5 Sternen5/5 (1)

- CompTIA A+ Complete Practice Tests: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Von EverandCompTIA A+ Complete Practice Tests: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Noch keine Bewertungen

- Patterns in the Machine: A Software Engineering Guide to Embedded DevelopmentVon EverandPatterns in the Machine: A Software Engineering Guide to Embedded DevelopmentBewertung: 5 von 5 Sternen5/5 (1)

- Windows 10 Mastery: The Complete User Guide to Learn Windows 10 from Beginner to ExpertVon EverandWindows 10 Mastery: The Complete User Guide to Learn Windows 10 from Beginner to ExpertBewertung: 3.5 von 5 Sternen3.5/5 (6)

- Amazon Echo Manual Guide : Top 30 Hacks And Secrets To Master Amazon Echo & Alexa For Beginners: The Blokehead Success SeriesVon EverandAmazon Echo Manual Guide : Top 30 Hacks And Secrets To Master Amazon Echo & Alexa For Beginners: The Blokehead Success SeriesNoch keine Bewertungen

- CompTIA A+ Certification All-in-One Exam Guide, Eleventh Edition (Exams 220-1101 & 220-1102)Von EverandCompTIA A+ Certification All-in-One Exam Guide, Eleventh Edition (Exams 220-1101 & 220-1102)Bewertung: 5 von 5 Sternen5/5 (2)

- How To Market Mobile Apps: Your Step By Step Guide To Marketing Mobile AppsVon EverandHow To Market Mobile Apps: Your Step By Step Guide To Marketing Mobile AppsNoch keine Bewertungen

- Raspberry Pi | 101: The Beginner’s Guide with Basics on Hardware, Software, Programming & ProjecVon EverandRaspberry Pi | 101: The Beginner’s Guide with Basics on Hardware, Software, Programming & ProjecNoch keine Bewertungen

![iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]](https://imgv2-2-f.scribdassets.com/img/audiobook_square_badge/728318688/198x198/f3385cbfef/1714737415?v=1)