Beruflich Dokumente

Kultur Dokumente

9A12301 Digital Logic Design & Computer Organization

Hochgeladen von

sivabharathamurthyOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

9A12301 Digital Logic Design & Computer Organization

Hochgeladen von

sivabharathamurthyCopyright:

Verfügbare Formate

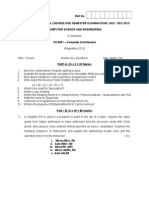

Code: 9A12301

1

(Common to Computer Science & Systems Engineering, and Information Technology)

II B.Tech I Semester (R09) Regular & Supplementary Examinations, November 2011 DIGITAL LOGIC DESIGN & COMPUTER ORGANIZATION Time: 3 hours Answer any FIVE questions All questions carry equal marks ***** 1 (a) (b) 2 3 4 Explain the operation of a computer. Convert the following numbers with the indicated bases to decimal: (4310)5, (198)12, (16.5)16, (26.24)8. Design a Modulo-12 up Synchronous counter Using T-Flip Flops and draw the Circuit diagram? Explain about the two ways to achieve a BCD Counter using a Counter with Parallel Load? Show the hardware to be used for the addition and subtraction of two decimal numbers in Signed-magnitude representation. Indicate how an overflow is detected. Explain with the help of an example, how data is accessed from memory location Write an ALP program that can evaluate the expression AXB+CXD in a single accumulator Processor Explain about the organization of the control unit which allow conditional branching in micro program with a neat diagram. Explain, how microinstruction is executed in micro programmed control with examples? List the specifications of floppy disks and magnetic disks What is meant by disc access time? What is meant by SCSI bus? How are interrupts enabled and disabled? How are multiple interrupts handled? How are vector interrupts implemented in processors? ***** Max Marks: 70

5 (a) (b) 6 (a) (b) 7 (a) (b) 8 (a) (b) (c)

Code: 9A12301

2

(Common to Computer Science & Systems Engineering, and Information Technology)

II B.Tech I Semester (R09) Regular & Supplementary Examinations, November 2011 DIGITAL LOGIC DESIGN & COMPUTER ORGANIZATION Time: 3 hours Answer any FIVE questions All questions carry equal marks ***** 1 (a) (b) 2 (a) (b) 3 (a) (b) 4 (a) (b) 5 (a) (b) 6 With the help of diagram, explain about interrupt cycle execution. Explain about IA-32 architecture supported addressing modes with examples. Explain, how a complete instruction is executed with the help of example. Explain about the control sequence for an unconditional branch instruction. Explain the characteristics of some common memory technologies. List the key characteristics of memory system and explain in brief. Write in detail the procedure to explain how processors software checks each of the I/O devices. Draw and explain the block diagram of I/O interface. Write short notes on (i) Error detecting codes, (ii) Error correcting codes. Give the detailed procedure to detect and correct a single error in a message. Using K-map determine the minimal expression for the following function with m (0, 2, 3, 4, 6, 7, 8, 12, 14, 15, 16, 18, 19, 20, 22, MAXTERMS and MINTERMS F = Max Marks: 70

23, 24, 28). 7 (a) (b) 8 (a) (b) Explain about the Following Serial Transfer in 4-bit shift Registers. Binary Ripple Counter. Draw the block diagram of BCD adder and explain in detail. A mode control input determines whether the digit is complemented or not. What is the advantage of using this code over BCD? *****

Code: 9A12301

3

(Common to Computer Science & Systems Engineering, and Information Technology)

II B.Tech I Semester (R09) Regular & Supplementary Examinations, November 2011 DIGITAL LOGIC DESIGN & COMPUTER ORGANIZATION Time: 3 hours Answer any FIVE questions All questions carry equal marks ***** 1 (a) (b) (c) (d) 2 (a) (b) 3 (a) (b) 4 5 (a) (b) 6 (a) (b) 7 (a) (b) 8 (a) (b) Convert the following numbers: 10101100111.0101 to Base 10. (153.513)10 = ( )8. Find (3250 - 72532)10 using 10's complement. Given that (292)10 = (1204)b determine `b'. Convert the following SOP equation into its POS form. G = XY 1 Z X 1YZ 1 . 1 1 Reduce the following Boolean expressions to three literals. A C ABC AC . What is a decoder? Draw the circuit of 3-to-8 line decoder with the help of a truth table. Describe the working of a 4-bit shift left register with a timing diagram. Derive an algorithm in flow chart form for adding and subtracting two fixed- point binary numbers when negative numbers are in signed-1s complement representation. What do you mean by memory capacity? Explain various addressing modes with the help of examples. Discuss on the single bus organization of the processor unit. Define Micro instruction. Discuss the Internal structure of 64X1 DRAM with help of a sketch. Explain the Timing diagram of the READ and WRITE cycle of Dynamic RAM. Explain with the help of neat sketch the single bus structure and multiple bus structure to connect I/O devices to a computer. Explain the different types of signal transfers that take place during CPU communication. ***** Max Marks: 70

Code: 9A12301

4

(Common to Computer Science & Systems Engineering, and Information Technology)

II B.Tech I Semester (R09) Regular & Supplementary Examinations, November 2011 DIGITAL LOGIC DESIGN & COMPUTER ORGANIZATION Time: 3 hours Answer any FIVE questions All questions carry equal marks ***** 1 (a) (b) 2 (a) (b) 3 (a) (b) 4 (a) (b) 5 (a) (b) 6 (a) (b) 7 8 Briefly explain about Big-endian and Little-endian Assignments. Explain, how loop instructions are executed in computer? Explain with the help of a neat sketch how the data transfer between the registers and common bus takes place. Draw the figure of the implementation of one bit register and explain. Draw and explain the organizations of ROM and PROM. Explain the difference between EPROM and EEPROM Discuss the various I/O interfacing techniques. Discuss the programmed I/O. What are Self complementing codes? Give examples. Write the procedure for constructing Hamming codes. Construct hamming codes for the decimal numbers 1,4, 8. Differentiate Latch and flip-flop. Explain the construction of S-R Latch. Construct a D-Latch and explain its operation. Implement the following functions using PAL and PLA F1 = m(2,3,4,7,8,11) , F2 = m(1,3,5,7,9,11,13,15). Explain with the help of neat block diagram high performance addition and multiplication operation. ***** . Max Marks: 70

Das könnte Ihnen auch gefallen

- Instructions For Installing The Fatemi FontDokument2 SeitenInstructions For Installing The Fatemi Font25931733% (3)

- OstepDokument643 SeitenOstepParikshit DiwanNoch keine Bewertungen

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxVon EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxBewertung: 4 von 5 Sternen4/5 (1)

- Oracle Database 12c Certified Master Exam (OCM) : DurationDokument3 SeitenOracle Database 12c Certified Master Exam (OCM) : DurationSWATINoch keine Bewertungen

- Shri Ramdeobaba College of Engineering andDokument18 SeitenShri Ramdeobaba College of Engineering andAditya BelekarNoch keine Bewertungen

- OSY 22516chapter1Dokument12 SeitenOSY 22516chapter12008 AvadhutNoch keine Bewertungen

- 9A12301 Digital Logic Design and Computer OrganizationDokument4 Seiten9A12301 Digital Logic Design and Computer OrganizationsivabharathamurthyNoch keine Bewertungen

- R5210505 Computer OrganizaionDokument1 SeiteR5210505 Computer OrganizaionsivabharathamurthyNoch keine Bewertungen

- 9A15501 System ProgrammingDokument4 Seiten9A15501 System ProgrammingsivabharathamurthyNoch keine Bewertungen

- 9A04401 Switching Theory & Logic DesignDokument4 Seiten9A04401 Switching Theory & Logic DesignsivabharathamurthyNoch keine Bewertungen

- 21 - 2011 - Dec - R09 - STLDDokument8 Seiten21 - 2011 - Dec - R09 - STLDvasuvlsiNoch keine Bewertungen

- 9A04306 Digital Logic DesignDokument4 Seiten9A04306 Digital Logic DesignsivabharathamurthyNoch keine Bewertungen

- 9A05704 Advanced Computer ArchitectureDokument4 Seiten9A05704 Advanced Computer ArchitecturesivabharathamurthyNoch keine Bewertungen

- 9A04401 Switching Theory and Logic DesignDokument4 Seiten9A04401 Switching Theory and Logic DesignsivabharathamurthyNoch keine Bewertungen

- RR310201 Computer OrganizationDokument1 SeiteRR310201 Computer OrganizationsivabharathamurthyNoch keine Bewertungen

- 9A04504 Digital IC Applications6Dokument4 Seiten9A04504 Digital IC Applications6subbuNoch keine Bewertungen

- R7411004 PC Based InstrumentationDokument1 SeiteR7411004 PC Based InstrumentationsivabharathamurthyNoch keine Bewertungen

- Jntuworld: R07 Set No. 2Dokument7 SeitenJntuworld: R07 Set No. 2Kasarla Shiva SjNoch keine Bewertungen

- STLD 2009 RegularDokument4 SeitenSTLD 2009 RegularrangerNoch keine Bewertungen

- 9A05406 Computer OrganizationDokument4 Seiten9A05406 Computer OrganizationsivabharathamurthyNoch keine Bewertungen

- End Term Examination: Paper Code: BBA - 107 Subject: Computer Fundamentals Paper IDDokument5 SeitenEnd Term Examination: Paper Code: BBA - 107 Subject: Computer Fundamentals Paper IDshivscribd1Noch keine Bewertungen

- Ca 13Dokument3 SeitenCa 13krishnasankar95Noch keine Bewertungen

- Computer OrganizationDokument1 SeiteComputer OrganizationsubbuNoch keine Bewertungen

- Rr310403-Digital Ic ApplicationsDokument1 SeiteRr310403-Digital Ic ApplicationssivabharathamurthyNoch keine Bewertungen

- NR Set No. 2Dokument4 SeitenNR Set No. 2adddataNoch keine Bewertungen

- VI Sem, Jan, Feb 2005Dokument4 SeitenVI Sem, Jan, Feb 2005Veeresh NicolyteNoch keine Bewertungen

- 9A15502 Digital System DesignDokument4 Seiten9A15502 Digital System Designsivabharathamurthy100% (1)

- Switching Theory and Logic DesignDokument8 SeitenSwitching Theory and Logic DesignVenkat ChadalavadaNoch keine Bewertungen

- 2019 20 COA Mid PaperDokument2 Seiten2019 20 COA Mid PaperDoraemon हिंदीNoch keine Bewertungen

- Jntuworld: R07 Set No. 2Dokument4 SeitenJntuworld: R07 Set No. 2Ram KrishnaNoch keine Bewertungen

- (Nov-11) (EUREE-504) : Unit-IiiDokument1 Seite(Nov-11) (EUREE-504) : Unit-IiiAnand KalNoch keine Bewertungen

- CS-64 Bachelor in Computer Applications Term-End Examination December, 2009 CS-64Dokument4 SeitenCS-64 Bachelor in Computer Applications Term-End Examination December, 2009 CS-64Prince AroraNoch keine Bewertungen

- RA 9A15501 System ProgrammingDokument1 SeiteRA 9A15501 System ProgrammingsivabharathamurthyNoch keine Bewertungen

- R7310404 Digital IC ApplicationsDokument1 SeiteR7310404 Digital IC ApplicationssivabharathamurthyNoch keine Bewertungen

- Instructions: 1. This Examination Consists of FIVE Questions 2. Answer Question ONE (COMPULSORY) and Any Other TWO QuestionsDokument5 SeitenInstructions: 1. This Examination Consists of FIVE Questions 2. Answer Question ONE (COMPULSORY) and Any Other TWO QuestionsNjoro officialNoch keine Bewertungen

- Digital Nov 07Dokument6 SeitenDigital Nov 07skssushNoch keine Bewertungen

- r5410207 Vlsi DesignDokument1 Seiter5410207 Vlsi DesignsivabharathamurthyNoch keine Bewertungen

- 21 - 2010 - Nov - R09 - STLDDokument8 Seiten21 - 2010 - Nov - R09 - STLDvasuvlsiNoch keine Bewertungen

- 07a3ec03 SwitchingthoeryandlogicdesignDokument8 Seiten07a3ec03 SwitchingthoeryandlogicdesignVijay KumarNoch keine Bewertungen

- DLD GTU Question Bank: Chapter-1 Binary SystemDokument5 SeitenDLD GTU Question Bank: Chapter-1 Binary Systemnirav34Noch keine Bewertungen

- R5210505 Computer OrganizationDokument1 SeiteR5210505 Computer OrganizationsivabharathamurthyNoch keine Bewertungen

- Embedded System DesignDokument2 SeitenEmbedded System DesignNipun JainNoch keine Bewertungen

- 9A04504 Digital IC ApplicationsDokument1 Seite9A04504 Digital IC ApplicationssubbuNoch keine Bewertungen

- 07a80305 ComputerorganizationandarchitectureDokument8 Seiten07a80305 ComputerorganizationandarchitectureSharanya ThirichinapalliNoch keine Bewertungen

- 9A04706 Digital Design Through Verilog HDL PDFDokument4 Seiten9A04706 Digital Design Through Verilog HDL PDFTayyabunnissa BegumNoch keine Bewertungen

- FocqpDokument2 SeitenFocqprangarajantrNoch keine Bewertungen

- Control Systems Question PapersDokument76 SeitenControl Systems Question Paperssatyakar_vvkNoch keine Bewertungen

- Mca 1 Sem Computer Organization and Architecture Kca105 2022Dokument1 SeiteMca 1 Sem Computer Organization and Architecture Kca105 2022kimog66911Noch keine Bewertungen

- R7310201-Computer System OrganizationDokument4 SeitenR7310201-Computer System OrganizationsivabharathamurthyNoch keine Bewertungen

- R5 221901 Computer OrganizationDokument1 SeiteR5 221901 Computer OrganizationsivabharathamurthyNoch keine Bewertungen

- In Computers, Subtraction Is Generally Carried Out byDokument2 SeitenIn Computers, Subtraction Is Generally Carried Out byatul211988Noch keine Bewertungen

- CDDokument8 SeitenCDPrasad BobyNoch keine Bewertungen

- Following Paper ID and Roll No. To Be Filled in Your Answer Book)Dokument3 SeitenFollowing Paper ID and Roll No. To Be Filled in Your Answer Book)Param WassonNoch keine Bewertungen

- 22323-2019-Winter-Question-Paper (Msbte Study Resources)Dokument3 Seiten22323-2019-Winter-Question-Paper (Msbte Study Resources)Parth patkarNoch keine Bewertungen

- SS07A4041 Digital IC ApplicationsDokument1 SeiteSS07A4041 Digital IC ApplicationsMahaboob SubahanNoch keine Bewertungen

- Code: 07A4041 B.Tech III Year I Semester (R07) Supplementary Examinations June 2015Dokument1 SeiteCode: 07A4041 B.Tech III Year I Semester (R07) Supplementary Examinations June 2015subbuNoch keine Bewertungen

- Campusexpress - Co.in: Set No. 1Dokument8 SeitenCampusexpress - Co.in: Set No. 1skssushNoch keine Bewertungen

- R7410505 Embedded SystemsDokument1 SeiteR7410505 Embedded SystemssivabharathamurthyNoch keine Bewertungen

- AprMay 2012 (R10)Dokument38 SeitenAprMay 2012 (R10)Rajesh ViswanadhamNoch keine Bewertungen

- II B.Tech II Semester, Regular Examinations, April - 2012 Switching Theory and Logic DesignDokument8 SeitenII B.Tech II Semester, Regular Examinations, April - 2012 Switching Theory and Logic Design142545Noch keine Bewertungen

- RT 21053112016Dokument4 SeitenRT 21053112016RaunaqNoch keine Bewertungen

- 07A4EC09 SWITCHINGTHEORYANDLOGICDESIGNfrDokument8 Seiten07A4EC09 SWITCHINGTHEORYANDLOGICDESIGNfrObula ReddyNoch keine Bewertungen

- Assignments CSE211Dokument4 SeitenAssignments CSE211Raghav JhanjeeNoch keine Bewertungen

- R7210504 Digital Logic DesignDokument1 SeiteR7210504 Digital Logic DesignsivabharathamurthyNoch keine Bewertungen

- SSC Social Textbook (AP)Dokument100 SeitenSSC Social Textbook (AP)sivabharathamurthyNoch keine Bewertungen

- R7410506 Mobile ComputingDokument1 SeiteR7410506 Mobile ComputingsivabharathamurthyNoch keine Bewertungen

- 9A13701 Robotics and AutomationDokument4 Seiten9A13701 Robotics and AutomationsivabharathamurthyNoch keine Bewertungen

- 07A4EC01 Environmental StudiesDokument1 Seite07A4EC01 Environmental StudiessivabharathamurthyNoch keine Bewertungen

- Control Systems (CS) Notes As Per JntuaDokument203 SeitenControl Systems (CS) Notes As Per Jntuasivabharathamurthy100% (3)

- R5410201 Neural Networks & Fuzzy LogicDokument1 SeiteR5410201 Neural Networks & Fuzzy LogicsivabharathamurthyNoch keine Bewertungen

- R7312301 Transport Phenomena in BioprocessesDokument1 SeiteR7312301 Transport Phenomena in BioprocessessivabharathamurthyNoch keine Bewertungen

- R7310406 Digital CommunicationsDokument1 SeiteR7310406 Digital CommunicationssivabharathamurthyNoch keine Bewertungen

- R7311006 Process Control InstrumentationDokument1 SeiteR7311006 Process Control InstrumentationsivabharathamurthyNoch keine Bewertungen

- Code: R7311306: (Electronics & Control Engineering)Dokument1 SeiteCode: R7311306: (Electronics & Control Engineering)sivabharathamurthyNoch keine Bewertungen

- 9A03505 Heat TransferDokument4 Seiten9A03505 Heat TransfersivabharathamurthyNoch keine Bewertungen

- 9A05707 Software Project ManagementDokument4 Seiten9A05707 Software Project ManagementsivabharathamurthyNoch keine Bewertungen

- R7311506 Operating SystemsDokument1 SeiteR7311506 Operating SystemssivabharathamurthyNoch keine Bewertungen

- R7310106 Engineering GeologyDokument1 SeiteR7310106 Engineering GeologysivabharathamurthyNoch keine Bewertungen

- R7311205 Distributed DatabasesDokument1 SeiteR7311205 Distributed DatabasessivabharathamurthyNoch keine Bewertungen

- 9A14503 Principles of Machine DesignDokument8 Seiten9A14503 Principles of Machine DesignsivabharathamurthyNoch keine Bewertungen

- 9A21506 Mechanisms & Mechanical DesignDokument8 Seiten9A21506 Mechanisms & Mechanical DesignsivabharathamurthyNoch keine Bewertungen

- R7310206 Linear Systems AnalysisDokument1 SeiteR7310206 Linear Systems AnalysissivabharathamurthyNoch keine Bewertungen

- R5310204 Power ElectronicsDokument1 SeiteR5310204 Power ElectronicssivabharathamurthyNoch keine Bewertungen

- 9A10505 Principles of CommunicationsDokument4 Seiten9A10505 Principles of CommunicationssivabharathamurthyNoch keine Bewertungen

- 9A15502 Digital System DesignDokument4 Seiten9A15502 Digital System Designsivabharathamurthy100% (1)

- 9A23501 Heat Transfer in BioprocessesDokument4 Seiten9A23501 Heat Transfer in BioprocessessivabharathamurthyNoch keine Bewertungen

- R7411509 Distributed DatabasesDokument1 SeiteR7411509 Distributed DatabasessivabharathamurthyNoch keine Bewertungen

- 9A02505 Electrical Machines-IIIDokument4 Seiten9A02505 Electrical Machines-IIIsivabharathamurthyNoch keine Bewertungen

- 9A04504 Digital IC ApplicationsDokument4 Seiten9A04504 Digital IC ApplicationssivabharathamurthyNoch keine Bewertungen

- R7412311 Metabolic EngineeringDokument1 SeiteR7412311 Metabolic EngineeringsivabharathamurthyNoch keine Bewertungen

- R7411307 Instrumentation & Control in Manufacturing SystemsDokument1 SeiteR7411307 Instrumentation & Control in Manufacturing SystemssivabharathamurthyNoch keine Bewertungen

- R7411510 Neural NetworksDokument1 SeiteR7411510 Neural NetworkssivabharathamurthyNoch keine Bewertungen

- R7412310 Nano BiotechnologyDokument1 SeiteR7412310 Nano BiotechnologysivabharathamurthyNoch keine Bewertungen

- R7411306 Robotics & AutomationDokument1 SeiteR7411306 Robotics & AutomationsivabharathamurthyNoch keine Bewertungen

- Alfresco Explorer Groups and RolesDokument11 SeitenAlfresco Explorer Groups and RolesPaul SarazinNoch keine Bewertungen

- Universe User GuideDokument102 SeitenUniverse User GuidePatrick HalleyNoch keine Bewertungen

- Configuratie LaptopDokument111 SeitenConfiguratie LaptopAlex GrigorasNoch keine Bewertungen

- The New Generation of Automated Blood Component Separators: Compomat G5Dokument2 SeitenThe New Generation of Automated Blood Component Separators: Compomat G5Putri NurNoch keine Bewertungen

- Nse8 811Dokument51 SeitenNse8 811lakis lalakis888Noch keine Bewertungen

- 4 Quarter Grade 9 TLE CSS (Computer System Servicing) Internet ProtocolsDokument8 Seiten4 Quarter Grade 9 TLE CSS (Computer System Servicing) Internet ProtocolsSERVEN GAMINGNoch keine Bewertungen

- Infoblox CLI Guide: NIOS 6.1 For Infoblox Network Core Services AppliancesDokument118 SeitenInfoblox CLI Guide: NIOS 6.1 For Infoblox Network Core Services AppliancesPriyanto UkiNoch keine Bewertungen

- Installing and Using Cuckoo Malware Analysis SandboxDokument30 SeitenInstalling and Using Cuckoo Malware Analysis SandboxThinh Tran VanNoch keine Bewertungen

- Windows Installation Neo4jDokument6 SeitenWindows Installation Neo4jmoisendiaye245Noch keine Bewertungen

- I.mx Yocto Project User's Guide LinuxDokument20 SeitenI.mx Yocto Project User's Guide Linuxparvathie santhoshNoch keine Bewertungen

- How To Use Tools PDFDokument67 SeitenHow To Use Tools PDFRose GutierrezNoch keine Bewertungen

- Differences Between Enterprise, Standard Edition 2 On Oracle 12.2Dokument9 SeitenDifferences Between Enterprise, Standard Edition 2 On Oracle 12.2baraka08Noch keine Bewertungen

- Brochure Vlsi DesignDokument2 SeitenBrochure Vlsi DesignAshlin AarthiNoch keine Bewertungen

- MB Manual Ga-H55n-Usb3 eDokument96 SeitenMB Manual Ga-H55n-Usb3 eproneaxNoch keine Bewertungen

- Route Redistribution: Unit 4&5 MCQDokument11 SeitenRoute Redistribution: Unit 4&5 MCQAshwin GiriNoch keine Bewertungen

- The Real-Time APIsDokument42 SeitenThe Real-Time APIsWallie BillingsleyNoch keine Bewertungen

- NX10 Release - NotesDokument114 SeitenNX10 Release - NotesAlexisNoch keine Bewertungen

- MonitorLog - Stardock Start11 1.31Dokument7 SeitenMonitorLog - Stardock Start11 1.31immiNoch keine Bewertungen

- Basic Ansible Ad-Hoc CommandsDokument14 SeitenBasic Ansible Ad-Hoc Commandspradeep bNoch keine Bewertungen

- Comparison Study Between IPV4 & IPV6: Amer Nizar Abu AliDokument4 SeitenComparison Study Between IPV4 & IPV6: Amer Nizar Abu AliSuranga SampathNoch keine Bewertungen

- 03 Back of The Envelope EstimationDokument6 Seiten03 Back of The Envelope EstimationsrawatNoch keine Bewertungen

- Linux Vs Ubuntu CommandsDokument5 SeitenLinux Vs Ubuntu CommandsArun KumarNoch keine Bewertungen

- Cambio Placa Control KM Bizhub C3110Dokument2 SeitenCambio Placa Control KM Bizhub C3110schumi_kaiser0% (1)

- MPMC Lesson PlanDokument3 SeitenMPMC Lesson PlanASUTOSH PATNAIKNoch keine Bewertungen

- Classification of Digital ComputersDokument45 SeitenClassification of Digital ComputersGhanshyam ParmarNoch keine Bewertungen