Beruflich Dokumente

Kultur Dokumente

Cmos Logic

Hochgeladen von

xewarOriginalbeschreibung:

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Cmos Logic

Hochgeladen von

xewarCopyright:

Verfügbare Formate

Sheet 1 of 11

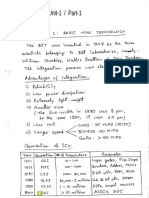

CMOS Logic In many aspects of RF design it is useful to have some knowledge of logic design, in particular PLL systems always employ some form of phase detector and sometimes a prescalar/divider. First lets re-cap on the operation of a N-type CMOS switch. Figure 1 shows the switch OFF condition ie no current flow between the drain and source. The bulk or substrate is made of lightly doped p-type silicon, which consists of positive holes (and a few negative electrons). An area of highly doped (many electrons) is deposited on the substrate in two positions to form the source and drain connections. Bridging these source and drain terminals is an area of insulating SiO2 (Silicon Dioxide) coated in metal which now forms the gate terminal. With no potential on the gate, there is no depletion region for current to flow between the drain and source terminals and so the switch is off.

Heavily doped N-type Silicon Gate Metal layer PolySilicate

0V

SiO2 Insulating Layer

Source

Drain

- - + + + + + + +

- - + Heavily doped N-type Silicon

Lightly doped p-type substrate

Figure 1 Showing the CMOS switch in the OFF condition, as there is 0V on the gate junction and there is no conducting layer under the gate to allow current to flow between the drain and source junctions. In Figure 2 the ON state is shown ie +5V is applied to the gate terminal. In this case the postive gate potential attracts electrons from the substrate causing a region of electrons formed under the gate insulation region. Current can now flow through this induced n-channel inversion region between the drain and source terminals.

Sheet 2 of 11

Gate Metal layer PolySilicate

+5V

SiO2 Insulating Layer

Source

Drain

- - +

Current flow through the Inversion

- - + Electrons attracted to area under the gate

+ + -

+ + +

Lightly doped p-type substrate

Figure 2 Showing the CMOS switch in the ON condition, as there is +5V on the gate junction. Electrons from the substrate are attracted to the area under the gate causing a conducting path between the drain and source junctions. CMOS INVERTER (NOT Gate) To form a simple inverter circuit we need to add a load resistor as shown in Figure 3.

Vcc R N-Type CMOS

Vout Vin

Figure 3 N-type CMOS FET switch with resistive load resistor. With Vin set to 0V the voltage across the gate to source junction will also be 0V. For a N-Type CMOS FET to switch the Vgs voltage needs to be > VT+VSAT, so with Vgs set to 0V the switch will be off and vout will be at Vcc (Vout will be directly connected to Vcc via the resistor R). In this case vin = lo; Vout = hi.

Sheet 3 of 11

When Vin is set to +5V (which is much greater than VT+VSAT) the CMOS Fet will be switched on and Vout will be shorted to ground making it 0V. In this case vin = hi; Vout = lo. Note that current will flow through the resistor R when the switch is ON and this is a waste of power. However, we can use a push-pull configuration using a P-type and N-type CMOS switch as shown in Figure 4.

Vcc (+5V) P-Type CMOS TR1

Vin N-Type CMOS TR2

Figure 4 Push-Pull CMOS Inverter circuit. With Vin Set to 5V (and Vcc set to 5V).

Vout

Vgs across the N-type CMOS FET (TR2) will be 5V, well above VT+VSAT and therefore TR2 will be switched ON. The Vgs across the P-type CMOS FET (TR1) will be 0V (Vcc (5V) Vin (5V)). This device requires VT+VSAT below Vcc before it switches on and so this device is OFF. With TR1 OFF and TR2 ON - Vout will be connected to 0V via TR2. With Vin Set to 0V (and Vcc set to 5V). Vgs across the N-type CMOS FET (TR2) will be 0V, below VT+VSAT and therefore TR2 will be switched OFF. The Vgs across the P-type CMOS FET (TR1) will now be ~ -5V (Vin (0V Vcc (5V)). This device requires at least VT+VSAT (~1V) below Vcc before it switches on in this case it will be nearly 5V and so this device will be switched ON. With TR1 ON and TR2 OFF - Vout will be connected to 5V (Vcc) via TR1. Note the Bulk/substrate connections (shown by the RED arrow), N-type bulk is connected to t he lowest voltage in this case 0V and the P-type connected to the highest voltage in this case Vcc (+5V).

Sheet 4 of 11

The circuit was simulated to verify operation using a 0.8um silicon-gate bulk CMOS n-well process using ADS. Figure 5 shows the ADS simulation setup using a Transient (Time domain) simulation with the inverter circuit connected to a square wave pulse generator operating at 50KHz.

VDD MOSFET_PMOS MOSFET2 Model=MOSFETM Length=L um Width=W um Vout

DT

VtPulseDT SRC2 Vlow=0 V Vhigh=5 V Delay=0 nsec Width=10 usec Period=20 usec Rout=1 Ohm

V_DC SRC1 Vdc=5.0 V

Vin

MOSFET_NMOS MOSFET1 Model=MOSFETM Length=L um Width=W um

TRANSIENT

Tran Tran1 StopTime=50 usec MaxTimeStep=250

Var Eqn

VAR VAR1 LAMBDA=0.1/L L=1 W=1

LEVEL1_Mode LEVEL1_Mode MOSFETM1 MOSFETM2 Uo=660 Vto=0.7 Uo=210 Vto=0.7 Kp=50e-6 Kp=50e-6 Gamma=0.6 Gamma=0.6 Phi=0.8 Phi=0.8 Lambda=LAMBDA Lambda=LAMBDA Pb=0.95 Pb=0.95 Cgso=220e-12 Cgso=220e-12 Cgdo=220e-12 Cgdo=220e-12 Cgbo=700e-12 Cgbo=700e-12 Cj=770e-6 Cj=560e-6 Mj=0.5 Mj=0.5 Cjsw=5e-10 Cjsw=5e-10 Mjsw=0.38 Mjsw=0.35 Tox=140e-10 Tox=150e-10 Ld=0.016 um Ld=0.015 um

Figure 5 ADS simulation setup to analyse the CMOS inverter based on 0.8um gate process. The pulse source provides a 50KHz square wave to the inverter. Note that the P-MOS device source is connected to Vcc and the N-MOS device source is connected to ground (the two drains are connected together to form the output).

Sheet 5 of 11

CMOS INVERTER (0.8um Silicon-gate bulk CMOS n-well process)

6 5 4

Vin, V

3 2 1 0 -1 0 10 20 30 40 50

time, usec

6

Vout, V

-2 0 10 20 30 40 50

time, usec

Figure 6 Resulting waveforms generated from the ADS simulation shown in figure 5, showing the inverting action. Note the overshoot appears to be a quirk of the transient simulation.

Sheet 6 of 11

CMOS NOR Gate A NOR gate can be designed by adding CMOS inverters in parallel. Figure 7 shows the circuit diagrams of a 2 NOR gate if more inputs are required more devices are added in parallel with TR3/TR4 and is series with TR1/TR2. Looking at the truth table we can see that a logic high output only occurs when A & B are low. With A & B at 0V CMOS P-type switches TR1 & TR2 will be ON connecting Vout to Vcc. Also the N-type CMOS switches TR3 & TR4 will be switched off (as Vgs =0 which is < VT+VSAT). In all other cases (where A or B are 1) one of the P type switches will be OFF and Vout will not be connected to VCC always resulting in a logic low on the output.

Vcc (+5V)

P-Type CMOS TR1 & TR2

A 0 0 1 1

B Vout 0 1 1 0 0 0 1 0

Vin A

N-Type CMOS TR3 & TR4

Vin B

Vout A+B

Figure 7 Two-Input NOR gate. To add more inputs another N-type device is added in parallel with TR3 & TR4 and another P-type device added in series with TR1 & TR2 the gates of the new devices connected together to form the new input.

Sheet 7 of 11

CMOS NAND Gate The structure of a 2-input NAND gate is the inversion of the 2-input NOR gate, ie parallel devices connected to +5V Vcc and series devices connected to ground as shown in Figure 8. The main problem with this circuit are the cumulative Vsats of the series devices. The ADS transient simulation of the NAND is shown in Figure 9 and is used as a basic building block for other more complex logic circuits eg flip-flops. The practical limit is for four devices ie 4-input NAND gate, to generate more inputs then these circuits can be cascaded as shown by a 4 input NAND using 2 off 2-input NANDS in Figure 11.

Vcc (+5V)

Vin A

P-Type CMOS TR1 & TR2

Vout = A*B Vin B N-Type CMOS TR3 & TR4

A 0 0 1 1

B Vout 0 1 1 1 0 1 1 0

Figure 8 Two-Input NAND gate. To add more inputs another P-type device is added in parallel with TR1 & TR2 and another N-type device added in series with TR3 & TR4 the gates of the new devices connected together to form the new input. One other disadvantage of this circuit is that the output impedance varies depending on the number of parallel P-type CMOS FETS are on or off. To eliminate this effect an inverter is added to the NAND output and will now form a AND gate. To restore the NAND function two inverters in series need to be added to the output of the NAND gates as shown in Figure 10.

Sheet 8 of 11

Port Vcc Num=3 MOSFET_PMOS MOSFET2 Model=MOSFETM2 Length=L um Width=W um MOSFET_PMOS MOSFET4 Model=MOSFETM2 Length=L um Width=W um

Port A Num=1 Port OUT Num=2 Port B Num=4 MOSFET_NMOS MOSFET1 Model=MOSFETM1 Length=L um Width=W um MOSFET_NMOS MOSFET3 Model=MOSFETM1 Length=L um Width=W um

LEVEL1_Model MOSFETM1 Vto=0.7 Kp=50e-6 Gamma=0.6 Phi=0.8 Lambda=LAMBDA Pb=0.95 Cgso=220e-12 Cgdo=220e-12 Cgbo=700e-12 Cj=770e-6 Mj=0.5 Cjsw=5e-10 Mjsw=0.38 Tox=140e-10 Ld=0.016 um

Uo=660

LEVEL1_Model MOSFETM2 Vto=0.7 Kp=50e-6 Gamma=0.6 Phi=0.8 Lambda=LAMBDA Pb=0.95 Cgso=220e-12 Cgdo=220e-12 Cgbo=700e-12 Cj=560e-6 Mj=0.5 Cjsw=5e-10 Mjsw=0.35 Tox=150e-10 Ld=0.015 um

Uo=210

Var Eqn

VAR VAR1 LAMBDA=0.1/L L=1 W=1

Figure 9 ADS Transient simulation setup for a 2 input NAND gate. NOTE this version is unbuffered and normally would have two inverters in series on the output.

Sheet 9 of 11

Vcc (+5V)

Vcc (+5V)

Vcc (+5V)

Vin A

P-Type CMOS TR1 & TR2

Vout = A*B

Vin B

N-Type CMOS TR3 & TR4

A*B

A*B

Figure 10 Buffered output 2-input NAND gate using CMOS inverters on the output. One inverter will realise a 2-input AND gate and another inverter is added to restore the NAND function.

Sheet 10 of 11

4-Input NAND gate using 2-Input logic gates

A

NAND

E G

NOR

B

NOT

C

NAND

H F

Figure 11 Realisation of a 4-input NAND gate using 2-input logic circuits NAND 1 A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 NAND 2 C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 NAND A*B E 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 0 NAND C*D F 1 1 1 0 1 1 1 0 1 1 1 0 1 1 1 0 NOR E+F G 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 NOT G H 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0

Table 1 Truth table for the 4-input NAND gate using 2 input logic circuits

Sheet 11 of 11

XOR Exclusive OR gate The exclusive OR gate differs from a normal OR gate in that the output is 1 if ONE of the inputs are one but not both of them. The truth table for the exclusive OR gate is shown below and the gate circuit diagram is shown in Figure 12:A 0 0 1 1 B 0 1 0 1 C 0 1 1 0

This type of gate can be used as a digital phase detector in PLL (phase locked loop) systems.

A

OR

AND

E

NAND

A 0 0 1 1

B 0 1 0 1

C 0 1 1 1

D 1 1 1 0

E 0 1 1 0

Figure 12 Showing XOR circuit and its corresponding truth table. In a PLL circuit the phase detector XOR gate is fed by two digital signals. One signal comes from the reference and the other from the VCO (voltage controlled oscillator). The operation of the XOR gate is analogous to that of an analogue multiplier and will produce a triangle wave output representing the phase error of the two input signals.

Das könnte Ihnen auch gefallen

- Lec32 CMOSImplementation PDFDokument31 SeitenLec32 CMOSImplementation PDFBom DangNoch keine Bewertungen

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsVon EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNoch keine Bewertungen

- CMOS Logic Circuits: Inverter 2 Input NOR 2 Input NAND Other FunctionsDokument23 SeitenCMOS Logic Circuits: Inverter 2 Input NOR 2 Input NAND Other FunctionsKumar Amit VermaNoch keine Bewertungen

- Unit-I VLSI & CDDokument39 SeitenUnit-I VLSI & CD21EC17- JAYA PRASAD.PNoch keine Bewertungen

- CMOS Logic FamilyDokument6 SeitenCMOS Logic FamilyAjay GeorgeNoch keine Bewertungen

- Unit 5Dokument6 SeitenUnit 5Tarun SinghalNoch keine Bewertungen

- Chapter 2 MOS Transistor TheoryDokument1 SeiteChapter 2 MOS Transistor TheoryCarlos SaavedraNoch keine Bewertungen

- Advance CMOS LogicDokument31 SeitenAdvance CMOS LogicRaja VidyaNoch keine Bewertungen

- Ec6601 Notes Rejinpaul PDFDokument47 SeitenEc6601 Notes Rejinpaul PDFDivya LakshmiNoch keine Bewertungen

- IV. Metal-Oxide Field-Effect Transistors (MOSFET) : ECE65 Lecture Notes (F. Najmabadi), Winter 2012Dokument26 SeitenIV. Metal-Oxide Field-Effect Transistors (MOSFET) : ECE65 Lecture Notes (F. Najmabadi), Winter 2012Ravi KumarNoch keine Bewertungen

- Concepts in VLSI DesignDokument59 SeitenConcepts in VLSI DesignA.K.M.TOUHIDUR RAHMANNoch keine Bewertungen

- ElectronicsDokument22 SeitenElectronicsVARSHITH REDDY JNoch keine Bewertungen

- UNIT - 1 INTRD To MOSDokument24 SeitenUNIT - 1 INTRD To MOSgnitsiceNoch keine Bewertungen

- MOS Device and Interconnects Scaling PhysicsDokument25 SeitenMOS Device and Interconnects Scaling PhysicsbashasvuceNoch keine Bewertungen

- Lec31 LogicGateCMOSDokument63 SeitenLec31 LogicGateCMOSPhamphuquynh1222Noch keine Bewertungen

- Pertemuan6 Diode AplcDokument46 SeitenPertemuan6 Diode AplcmbloexNoch keine Bewertungen

- Power MosfetsDokument11 SeitenPower MosfetsSoudip KUNDUNoch keine Bewertungen

- Module I CMOS TechnologyDokument81 SeitenModule I CMOS TechnologyAruna CTUGNoch keine Bewertungen

- Introduction to CMOS technology and logic gate fundamentalsDokument39 SeitenIntroduction to CMOS technology and logic gate fundamentalsvenkateshNoch keine Bewertungen

- Mos Transistor TheoryDokument144 SeitenMos Transistor TheorymailtolokiNoch keine Bewertungen

- Ee210 L37-40 PDFDokument89 SeitenEe210 L37-40 PDFPragyan PandeyNoch keine Bewertungen

- VLSI Design Lecture NotesDokument117 SeitenVLSI Design Lecture NotesRaji SharmiNoch keine Bewertungen

- Trasistor BasicsDokument50 SeitenTrasistor BasicsMuhammad SaadNoch keine Bewertungen

- Transistor As A Switch: Electronics and Communication Circuits Lab. Experiment #6Dokument5 SeitenTransistor As A Switch: Electronics and Communication Circuits Lab. Experiment #6Eng. Ahmad ELsamakNoch keine Bewertungen

- Vlsi Group-B Q&aDokument13 SeitenVlsi Group-B Q&aROHAN CHOWDHURYNoch keine Bewertungen

- Mos, Cmos, Transmission GatesDokument17 SeitenMos, Cmos, Transmission GatesSynthiya VinothiniNoch keine Bewertungen

- Introduction To CMOS Logic CircuitsDokument176 SeitenIntroduction To CMOS Logic CircuitsrdanwaraNoch keine Bewertungen

- Vlsi Unit-IDokument45 SeitenVlsi Unit-Isuneelanubolu7Noch keine Bewertungen

- Unit 1 Q ADokument31 SeitenUnit 1 Q AADEPOJU AyobamiNoch keine Bewertungen

- Lec 7,8 Modern CMOS TechnologyDokument43 SeitenLec 7,8 Modern CMOS TechnologyVikram MeenaNoch keine Bewertungen

- Introduction To Cmos Circuits: Unit IiDokument48 SeitenIntroduction To Cmos Circuits: Unit Iiarun14089Noch keine Bewertungen

- Chapter 2 Modern CMO PDFDokument20 SeitenChapter 2 Modern CMO PDFheNoch keine Bewertungen

- Chapter 2 Modern CMOS Technology - IDokument20 SeitenChapter 2 Modern CMOS Technology - Ifadwa badiNoch keine Bewertungen

- DCID Experiment MergedDokument94 SeitenDCID Experiment MergedSumer SainiNoch keine Bewertungen

- Zo: Transmission Lines, Reflections, and TerminationDokument9 SeitenZo: Transmission Lines, Reflections, and TerminationSiddhasen PatilNoch keine Bewertungen

- Power Mosfets: Introduction To Fet'SDokument21 SeitenPower Mosfets: Introduction To Fet'SSharth KumarNoch keine Bewertungen

- Lecture 3Dokument26 SeitenLecture 3Rashid AliNoch keine Bewertungen

- Analogue Integrated Circuit and SystemDokument13 SeitenAnalogue Integrated Circuit and SystemSaleh AlmazrouiNoch keine Bewertungen

- Final CMOS BasicsDokument23 SeitenFinal CMOS BasicsDeepak Kumar S NadigerNoch keine Bewertungen

- Nmos FabricationDokument45 SeitenNmos FabricationDr-GopalNoch keine Bewertungen

- MosfetDokument30 SeitenMosfetsakibNoch keine Bewertungen

- CMOS Subcircuit Design and AnalysisDokument80 SeitenCMOS Subcircuit Design and AnalysisashishmanyanNoch keine Bewertungen

- E3 238 Analog VLSI Circuits: Lecture 2: Review of Device CharacteristicsDokument11 SeitenE3 238 Analog VLSI Circuits: Lecture 2: Review of Device CharacteristicsaxiomNoch keine Bewertungen

- VLSI Lec 01Dokument66 SeitenVLSI Lec 01Maheen GulNoch keine Bewertungen

- Electrical properties and characteristics of MOSFET transistorsDokument36 SeitenElectrical properties and characteristics of MOSFET transistorsDebanjan DattaNoch keine Bewertungen

- Assignment FET 2Dokument3 SeitenAssignment FET 2shobanraj1995Noch keine Bewertungen

- Introduction to CMOS logic and gate designDokument45 SeitenIntroduction to CMOS logic and gate designNishanth Nish0% (1)

- Vlsi Topic2bDokument4 SeitenVlsi Topic2bsyabseeshoesNoch keine Bewertungen

- Cmos Sessional 1Dokument5 SeitenCmos Sessional 1Ashish KumarNoch keine Bewertungen

- Detailed Notes: IC Fabrication ProcessDokument81 SeitenDetailed Notes: IC Fabrication ProcessimmadiuttejNoch keine Bewertungen

- University of California at Berkeley College of Engineering Department of Electrical Engineering and Computer SciencesDokument3 SeitenUniversity of California at Berkeley College of Engineering Department of Electrical Engineering and Computer Sciencesvp agutamNoch keine Bewertungen

- Unit 2 - CMOS Logic, Fabrication and LayoutDokument34 SeitenUnit 2 - CMOS Logic, Fabrication and LayoutphillipNoch keine Bewertungen

- Ir2010 & (PBF) : High and Low Side Driver SDokument16 SeitenIr2010 & (PBF) : High and Low Side Driver SManoel BonfimNoch keine Bewertungen

- CH 6Dokument44 SeitenCH 6Samuel YuNoch keine Bewertungen

- Lesson 7 MOSFETDokument30 SeitenLesson 7 MOSFETAlbert OmondiNoch keine Bewertungen

- Module 4 CMOS LogicDokument18 SeitenModule 4 CMOS LogicJessie Tess TolentinoNoch keine Bewertungen

- Transmission Lines NotesDokument9 SeitenTransmission Lines NotesAshutosh Daichang GautamNoch keine Bewertungen

- Lecture 080 - Latchup and Esd: CMOS Analog Circuit Design, 2Dokument16 SeitenLecture 080 - Latchup and Esd: CMOS Analog Circuit Design, 2Milan DubeyNoch keine Bewertungen

- MOS and VLSI Technology OverviewDokument54 SeitenMOS and VLSI Technology OverviewAndrews austinNoch keine Bewertungen