Beruflich Dokumente

Kultur Dokumente

Universidad Politécnica de Puebla

Hochgeladen von

Motita MotaOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Universidad Politécnica de Puebla

Hochgeladen von

Motita MotaCopyright:

Verfügbare Formate

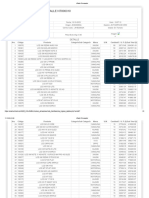

UNIVERSIDAD POLITCNICA DE PUEBLA

Organismo Pblico Descentralizado del Gobierno del Estado de Puebla

INGENIERA EN MECATRNICA

DISEO MECATRNICO I

PRCTICA 5

SENSADO DE TEMPERATURA A TRAVS DEL PROTOCOLO I2C.

INTEGRANTES

HUGO CORTES CORTES

PROFESOR. M.C. JOS PEDRO SNCHEZ SANTANA

CUATRIMESTRE: MAYO-AGOSTO

27 DE JUNIO DE 2011

OBJETIVO Implementar la comunicacin de dos pics a travs del protocolo I2C utilizando un sensor de temperatura. JUSTIFICACIN I2C facilita la comunicacin entre microcontroladores, memorias y otros dispositivos con cierto nivel de "inteligencia", slo requiere de dos lneas de seal y un comn o masa. Permite el intercambio de informacin entre muchos dispositivos a una velocidad aceptable, de unos 100 Kbits por segundo, aunque hay casos especiales en los que el reloj llega hasta los 3,4 MHz. La metodologa de comunicacin de datos del bus I2C es en serie y sincrnica. Una de las seales del bus marca el tiempo (pulsos de reloj) y la otra se utiliza para intercambiar datos. Tambin permite tener conectados elementos al bus que se alimenten a tensiones distintas siempre que la tensin en las lneas sea interpretada correctamente por todos los componentes y que esta sea la menor de todas las alimentaciones existentes. El I2C es un bus con mltiples maestros, lo que significa que se pueden conectar varios chips al mismo bus y que todos ellos pueden actuar como maestro, slo con iniciar la transferencia de datos. Este bus se utiliza en muchos dispositivos, en especial en equipos de vdeo como monitores de computadora, televisores y videocaseteras. MARCO TERICO Definicin de i2c. Abreviatura de Inter-IC (inter integrated circuits), un tipo de bus diseado por Philips Semiconductors a principios de los 80s, que se utiliza para conectar circuitos integrados (ICs). Definicin de trminos: Maestro (Master): Dispositivo que determina los tiempos y la direccin del trfico en el bus. Es el nico que aplica los pulsos de reloj en la lnea SCL. Cuando se conectan varios dispositivos maestros a un mismo bus la configuracin obtenida se denomina "multi-maestro". Esclavo (Slave): Todo dispositivo conectado al bus que no tiene la capacidad de generar pulsos de reloj. Los dispositivos esclavos reciben seales de comando y de reloj generados desde el maestro. Bus libre (Bus Free): Estado en el que ambas lneas (SDA y SCL) estn inactivas, presentando un estado lgico alto. Es el nico momento en que un dispositivo maestro puede comenzar a hacer uso del bus. Comienzo (Start): Se produce cuando un dispositivo maestro ocupa el bus, generando la condicin. La lnea de datos (SDA) toma un estado bajo mientras que la lnea de reloj (SCL) permanece alta.

Parada (Stop): Un dispositivo maestro puede generar esta condicin, dejando libre el bus. La lnea de datos y la de reloj toman un estado lgico alto. Dato vlido (Valid Data): Situacin presente cuando un dato presente en la lnea SDA es estable al tiempo que la lnea SCL est a nivel lgico alto. Formato de Datos (Data Format): La transmisin de un dato a travs de este bus consiste de 8 bits de dato (1 byte). A cada byte transmitido al bus le sigue un noveno pulso de reloj durante el cual el dispositivo receptor del byte debe generar un pulso de reconocimiento. Reconocimiento (Acknowledge): El pulso de reconocimiento, conocido como ACK se logra colocando la lnea de datos a un nivel lgico bajo durante el transcurso del noveno pulso de reloj. Direccin (Address): Todo dispositivo diseado para funcionar en este bus posee su propia y nica direccin de acceso, preestablecida por el fabricante. Hay dispositivos que permiten definir externamente parte de la direccin de acceso, lo que habilita que se pueda conectar en un mismo bus un conjunto de dispositivos del mismo tipo, sin problemas de identificacin. La direccin 00 es la denominada "de acceso general"; a sta responden todos los dispositivos conectados al bus. Lectura/Escritura (Bit R/W): Cada dispositivo tiene una direccin de 7 bits. El octavo bit (el menos significativo) que se enva durante la operacin de direccionamiento, completando el byte, indica el tipo de operacin a realizar. Si este bit es alto el dispositivo maestro lee informacin proveniente de un dispositivo esclavo. Si este bit es bajo, el dispositivo maestro escribe informacin en un dispositivo esclavo.

Das könnte Ihnen auch gefallen

- EM P02 Guide PDFDokument3 SeitenEM P02 Guide PDFjuanNoch keine Bewertungen

- Dipolo DobladoDokument14 SeitenDipolo Dobladomairyn24Noch keine Bewertungen

- PIC Pinguino 18f4550Dokument8 SeitenPIC Pinguino 18f4550Ingeniería Mecánica EléctricaNoch keine Bewertungen

- Catalogo Novedades Mayo 2016Dokument93 SeitenCatalogo Novedades Mayo 2016templpaNoch keine Bewertungen

- Dagel Nanoladder v1 Manual Version 1Dokument28 SeitenDagel Nanoladder v1 Manual Version 1juanma1364Noch keine Bewertungen

- Practica 0Dokument8 SeitenPractica 0lalezka100% (1)

- Factura Merca 11-10Dokument5 SeitenFactura Merca 11-10Luifer DevozNoch keine Bewertungen

- Pud ElectricidadDokument15 SeitenPud Electricidadeduardo sarmientoNoch keine Bewertungen

- Control de Frecuencia Con PLLDokument13 SeitenControl de Frecuencia Con PLLGiancarlo Villanueva OropezaNoch keine Bewertungen

- Ejercicios 14.10-14.41 - Cristian - Motta - A - CE3 - Grupo - ADokument26 SeitenEjercicios 14.10-14.41 - Cristian - Motta - A - CE3 - Grupo - ACRISTIAN RENE MOTTA ARRATIANoch keine Bewertungen

- Practica3 2011Dokument4 SeitenPractica3 2011Jorge SabioNoch keine Bewertungen

- Secuenciador de LucesDokument3 SeitenSecuenciador de LucesKevinAlxChrNoch keine Bewertungen

- CatalogoDokument25 SeitenCatalogomiguelNoch keine Bewertungen

- Lab06 - Control de Fase de Triac Culminado DiegoDokument19 SeitenLab06 - Control de Fase de Triac Culminado Diegoanon_843632677Noch keine Bewertungen

- Receptor FM MiniaturaDokument5 SeitenReceptor FM MiniaturaAlexander Peña Alvarado0% (1)

- Folleto Em200Dokument2 SeitenFolleto Em200Rds Comunicaciones EirlNoch keine Bewertungen

- Universidad Nacional de Ingenieri1Dokument9 SeitenUniversidad Nacional de Ingenieri1Julian Farje RondónNoch keine Bewertungen

- Práctica 5. ZenerDokument9 SeitenPráctica 5. ZenerOliver TorresNoch keine Bewertungen

- Max-Zs530 RDS-SPNDokument28 SeitenMax-Zs530 RDS-SPNFredyLoyolaNoch keine Bewertungen

- Modulación de Amplitud (Am) : Ing. Alexis Barrios Ulloa MSCDokument27 SeitenModulación de Amplitud (Am) : Ing. Alexis Barrios Ulloa MSCRhenato SierraNoch keine Bewertungen

- Tarea Electronica 1Dokument4 SeitenTarea Electronica 1Karol CardozoNoch keine Bewertungen

- Muestreo SenalesDokument8 SeitenMuestreo SenalesMilena RodriguezNoch keine Bewertungen

- Monografia Sobre La Evolución de Los MonitoresDokument16 SeitenMonografia Sobre La Evolución de Los MonitoresByron Michael Paz100% (1)

- FacturaDokument7 SeitenFacturajuanNoch keine Bewertungen

- Programacion Del Baofeng NUEVO UV B5 PDFDokument7 SeitenProgramacion Del Baofeng NUEVO UV B5 PDFZen LaboratoryNoch keine Bewertungen

- Anuncio LaptopDokument1 SeiteAnuncio LaptopCLEIDER MARTIN FLORES CASTAÑEDANoch keine Bewertungen

- Amplificador Operacional CmosDokument15 SeitenAmplificador Operacional Cmosagustin7889Noch keine Bewertungen

- Alarm ADokument3 SeitenAlarm AAlex SaarNoch keine Bewertungen

- Universidad Nacional José Faustino SánchezDokument4 SeitenUniversidad Nacional José Faustino SánchezScott MelgarejoNoch keine Bewertungen

- P03 Edicion Compilación Depuración y Simulación Con ProteusDokument12 SeitenP03 Edicion Compilación Depuración y Simulación Con ProteusBrayam MirandaNoch keine Bewertungen