Beruflich Dokumente

Kultur Dokumente

ADC (Analog To Digital Converter) Module For FPGA Design

Hochgeladen von

IonelaOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

ADC (Analog To Digital Converter) Module For FPGA Design

Hochgeladen von

IonelaCopyright:

Verfügbare Formate

ADC (Analog to Digital Converter) Module for FPGA Design http://dev.emcelettronica.

com/print/52000

Your Electronics Open Source

(http://dev.emcelettronica.com)

Home > Blog > botondkirei's blog > Contenuti

ADC (Analog to Digital Converter) Module for

FPGA Design

By botondkirei

Created 10/22/2008 - 21:17

Embedded ADC analog to digital converter FPGA fpga board fpga design

The Digilent Inc. from USA is a vendor for FPGA solutions. The portfolio of the company includes high

quality educational FPGA boards and adequate peripheral modules as ADCs and DACs.

This is equipped with the National Semiconductor’s ADCS7476MSPS 12-bit A/D converter providing up to

1 MSample/second on two independent channels. The analog input is conditioned by the 2 pole Sallen-Key

anti-alias filter. Due to its small size (0.95" x 0.80") and the 6-pin standard header it becomes suitable not

only for didactic use, but for some commercial applications also.

And now let’s focus on the FPGA interface. By opening the ADC datasheet, you will find out that it has a

standards SPI interface. Trough this you can introduce the samples for the further processing in the FPGA

design.

Some designers can get lucky and they already have some Intellectual Property for the SPI interface. They

don’t have anything to do just to instantiate this module in their design and the interfacing is done. But

some of the designers are not so lucky. They have to prepare themselves the ADC interface for DMA

controller or other industry standard bus.

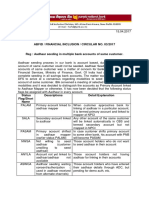

My advice is to build an interface heaving the structure Form Fig. 1. This structure contains a buffer; on the

write side there is a state machine reading the samples and writing them to the buffer; on the read side

another state machine reads the samples and passes towards the interface.

Fig. 1. Suggested structure for interface

This buffer can be created by the development tools of the FPGA vendors. The Xilinx FPGAs design suite

is the ISE Foundation Software. Within this software anybody can find the Core Generator tool, which

allows us to generate the buffer core. The Altera FPGAs are also supported by core generator software,

which can be accessed form the Quartus II design environment.

The core generator software will provide a wrapper module for simulation purpose and synthesizable

structure for implementation. From the wrapper module the designer can easily learn the necessary

read/write interface of the buffer.

1 din 2 23.10.2008 22:17

ADC (Analog to Digital Converter) Module for FPGA Design http://dev.emcelettronica.com/print/52000

Using the specifications of the SPI interface and the buffer write side signals, the designer can build “State

Machine 1” from Fig. 1. The HDL designers find much easier to write directly the code in Verilog or VHDL.

To prepare the state machine there are other options also, by using state machine computer aided design

suites. One of them StateCAD, is included in Xilinx’ ISE Foundation Software.

Fig. 2. Diagram for “State Machine 1”

On Fig 2. the state diagram of “State Machine 1” is depicted. The ‘idle’ state waits for a transaction to begin.

The transaction is started by pulling the CS signal low (see the ADC converter datasheet). When the

transaction begins 16 bits are read from the SDA pin. This operation is accomplished by the ‘read_state’.

Finally the buffer write is done by the ‘buffer_write’ state. In this state the ‘bufwr’ signal is activated and

waits for the ‘bufer_write_ack’ signal to finish the transaction.

Trademarks

Source URL: http://dev.emcelettronica.com/adc-analog-digital-converter-module-fpga-design

2 din 2 23.10.2008 22:17

Das könnte Ihnen auch gefallen

- Low Power Nine-Bit Sigma-Delta ADC Design Using TSMC 0.18micron TechnologyDokument5 SeitenLow Power Nine-Bit Sigma-Delta ADC Design Using TSMC 0.18micron Technologyeditor_ijtel100% (1)

- Chap. 8 Integrated-Circuit Logic Families: Chapter Outcomes (Objectives)Dokument62 SeitenChap. 8 Integrated-Circuit Logic Families: Chapter Outcomes (Objectives)estraj1954Noch keine Bewertungen

- MultiSIM - SPICE SimulationDokument7 SeitenMultiSIM - SPICE SimulationRomeu Corradi JúniorNoch keine Bewertungen

- Single, 2 MHZ Buck-Boost Controller Drives Entire Led Headlight Cluster Meets Cispr 25 Class 5 EmiDokument60 SeitenSingle, 2 MHZ Buck-Boost Controller Drives Entire Led Headlight Cluster Meets Cispr 25 Class 5 EmitorinomgNoch keine Bewertungen

- Circuit Analysis 2 Lab Report 2 Pieas PakistanDokument6 SeitenCircuit Analysis 2 Lab Report 2 Pieas PakistanMUYJ NewsNoch keine Bewertungen

- EE-330 Digital Signal Processing Lab1 CoDokument6 SeitenEE-330 Digital Signal Processing Lab1 CoZedrik MojicaNoch keine Bewertungen

- Digital Signal Processing Lab MannualDokument37 SeitenDigital Signal Processing Lab Mannualsreenathreddy100% (4)

- Module 7Dokument72 SeitenModule 7sai manikantaNoch keine Bewertungen

- Ec 6511 Digital Signal Processing Lab Manual PDFDokument88 SeitenEc 6511 Digital Signal Processing Lab Manual PDFBala913Noch keine Bewertungen

- Multisim Thermal ModelingDokument23 SeitenMultisim Thermal ModelingAzxctybv VpolmNoch keine Bewertungen

- Lecture 12 (ADC) Rv01Dokument47 SeitenLecture 12 (ADC) Rv01Amirul HaqimieNoch keine Bewertungen

- Lab 6Dokument12 SeitenLab 6Sujan HeujuNoch keine Bewertungen

- Notes04 ADCDokument9 SeitenNotes04 ADCHosam BendaryNoch keine Bewertungen

- VHDL Implemenation of Cordic AlgorithmDokument39 SeitenVHDL Implemenation of Cordic Algorithm1234sharada50% (2)

- Matlab Basics Tutorial: VectorsDokument52 SeitenMatlab Basics Tutorial: VectorsMohit Bathla MontyNoch keine Bewertungen

- DSP Overlap Add MethodDokument12 SeitenDSP Overlap Add MethodPavan Kumar P N71% (7)

- EE Lab Manuls Fast NuDokument70 SeitenEE Lab Manuls Fast NuMuhammad SaadNoch keine Bewertungen

- Practical Signal ProcessingDokument30 SeitenPractical Signal ProcessingLokender TiwariNoch keine Bewertungen

- Power Spectral Density MatlabDokument3 SeitenPower Spectral Density MatlabAnand Raj100% (2)

- Signal and Systems Lab Manual PDFDokument78 SeitenSignal and Systems Lab Manual PDFMuhammad SaadNoch keine Bewertungen

- Eia 232 422 486Dokument40 SeitenEia 232 422 486Supriya DessaiNoch keine Bewertungen

- Differences Between Mup and MucDokument2 SeitenDifferences Between Mup and Mucrihatrivedi_069Noch keine Bewertungen

- ADC (Analog-To-Digital Converter)Dokument11 SeitenADC (Analog-To-Digital Converter)Abdullah Muzammil0% (1)

- Lecture 20 of Goertzel AlgoDokument4 SeitenLecture 20 of Goertzel Algoc_mc2Noch keine Bewertungen

- Heart Beat MonitoringDokument5 SeitenHeart Beat MonitoringVishnu Sadasivan100% (1)

- VCODokument20 SeitenVCOVijay KiranNoch keine Bewertungen

- D 01Dokument209 SeitenD 01Raj Boda0% (1)

- Differential Voltage Current Conveyor (DVCC)Dokument81 SeitenDifferential Voltage Current Conveyor (DVCC)raam0006100% (1)

- Frequency Estimation by Modulation FFT and MusicDokument4 SeitenFrequency Estimation by Modulation FFT and MusicsujanyaNoch keine Bewertungen

- DSP Development Board User ManualDokument29 SeitenDSP Development Board User ManualWaqar UddinNoch keine Bewertungen

- 14.4 Bode Plots: Frequency Response 589Dokument12 Seiten14.4 Bode Plots: Frequency Response 589Luis Lizana100% (1)

- Biopotential AmplifiersDokument15 SeitenBiopotential AmplifiersJesus PeñaNoch keine Bewertungen

- Robot Sensors: An OverviewDokument59 SeitenRobot Sensors: An OverviewsafeerkkNoch keine Bewertungen

- Microprocessors and Interfacing DevicesDokument102 SeitenMicroprocessors and Interfacing DevicesOCTOPUS INSTITUTENoch keine Bewertungen

- Qca Project PPTDokument20 SeitenQca Project PPTPandu KNoch keine Bewertungen

- To Design An Adaptive Channel Equalizer Using MATLABDokument43 SeitenTo Design An Adaptive Channel Equalizer Using MATLABAngel Pushpa100% (1)

- Digital Logic MinutesDokument36 SeitenDigital Logic MinutesshyamalaperiNoch keine Bewertungen

- IQMath Fixed Vs Floating PDFDokument30 SeitenIQMath Fixed Vs Floating PDFGautam KumarNoch keine Bewertungen

- 2 Bit Comparator PDFDokument12 Seiten2 Bit Comparator PDFSunith CkNoch keine Bewertungen

- Progress in Electromagnetics Research, PIER 98, 33-52, 2009Dokument20 SeitenProgress in Electromagnetics Research, PIER 98, 33-52, 2009brij_astraNoch keine Bewertungen

- DTTTDokument528 SeitenDTTTMỹ Phước NguyễnNoch keine Bewertungen

- (Ebook - Electronics) - Principles of PLL - Tutorial (Kroupa 2000)Dokument66 Seiten(Ebook - Electronics) - Principles of PLL - Tutorial (Kroupa 2000)양종렬Noch keine Bewertungen

- MATLAB Chapter 1: An Overview of MATLABDokument152 SeitenMATLAB Chapter 1: An Overview of MATLABHusseinHazimeNoch keine Bewertungen

- !!!! Signal Integrity Considerations For High Speed Digital HardwareDokument12 Seiten!!!! Signal Integrity Considerations For High Speed Digital HardwarePredrag PejicNoch keine Bewertungen

- Dcs Lab ManualDokument33 SeitenDcs Lab ManualKumaran SgNoch keine Bewertungen

- DSP Matlab ProgramsDokument50 SeitenDSP Matlab ProgramsDhiraj Thakur67% (3)

- Bessel Function ZeroesDokument5 SeitenBessel Function Zeroesputin208Noch keine Bewertungen

- MultiSim PDFDokument5 SeitenMultiSim PDFjaya1816Noch keine Bewertungen

- Wall Health Monitoring by Ultrasonic Pulse-Echo TechniqueDokument4 SeitenWall Health Monitoring by Ultrasonic Pulse-Echo TechniqueBose Boban.m.Noch keine Bewertungen

- Arduino SPWM Sine InverterDokument5 SeitenArduino SPWM Sine InvertermaurilioctbaNoch keine Bewertungen

- VHDL Based Circuits Design and Synthesis On FPGA: A Dice Game Example For EducationDokument6 SeitenVHDL Based Circuits Design and Synthesis On FPGA: A Dice Game Example For EducationRam RajaNoch keine Bewertungen

- Unit 6 I ADCDokument29 SeitenUnit 6 I ADCcacaNoch keine Bewertungen

- Hve Numerical MethodsDokument17 SeitenHve Numerical MethodsSainadh SinghNoch keine Bewertungen

- Fundamentals of Electronics 2: Continuous-time Signals and SystemsVon EverandFundamentals of Electronics 2: Continuous-time Signals and SystemsNoch keine Bewertungen

- Relational Data Model A Complete Guide - 2020 EditionVon EverandRelational Data Model A Complete Guide - 2020 EditionNoch keine Bewertungen

- Engineering Optimization: An Introduction with Metaheuristic ApplicationsVon EverandEngineering Optimization: An Introduction with Metaheuristic ApplicationsNoch keine Bewertungen

- Freescale's S08 Ultra-Low-Power MCU With LCD DriverDokument6 SeitenFreescale's S08 Ultra-Low-Power MCU With LCD DriverIonela100% (1)

- Getting Started With CodeWarrior IDE From FreescaleDokument8 SeitenGetting Started With CodeWarrior IDE From FreescaleIonela100% (1)

- Fundamentals of TransistorsDokument145 SeitenFundamentals of TransistorsJoemill Veloso Flordelis100% (7)

- Brushless DC Electric Motor Control by CPLDDokument6 SeitenBrushless DC Electric Motor Control by CPLDIonela100% (3)

- Getting Started With JM Bagde Board From FreescaleDokument5 SeitenGetting Started With JM Bagde Board From FreescaleIonela100% (1)

- Transistor Technique, GernsbackDokument97 SeitenTransistor Technique, GernsbackKevin HaworthNoch keine Bewertungen

- Freescale I.mx27 IP Camera Reference DesignDokument4 SeitenFreescale I.mx27 IP Camera Reference DesignIonela100% (2)

- Microchip's MPLAB Starter Kit For DsPIC Digital Controllers - ..Dokument5 SeitenMicrochip's MPLAB Starter Kit For DsPIC Digital Controllers - ..Ionela100% (5)

- NCP3063-D - The Hysteric DC-DC ConverterDokument2 SeitenNCP3063-D - The Hysteric DC-DC ConverterIonelaNoch keine Bewertungen

- Simple Infrared BarrierDokument5 SeitenSimple Infrared BarrierIonela100% (6)

- Alarm System - Educational Example Using The Omron PLC C28KDokument6 SeitenAlarm System - Educational Example Using The Omron PLC C28KIonela100% (7)

- ColdFire Kirin3 and Free RTOS MQX From FreescaleDokument3 SeitenColdFire Kirin3 and Free RTOS MQX From FreescaleIonelaNoch keine Bewertungen

- Your Electronics Open Source: FIFO QueueDokument6 SeitenYour Electronics Open Source: FIFO QueueIonela100% (2)

- Inverter Air ConditionerDokument1 SeiteInverter Air ConditionerIonela100% (1)

- Renesas M16C Micro Controller LCD DisplayDokument12 SeitenRenesas M16C Micro Controller LCD DisplayIonela100% (2)

- Understanding Bio ElectricityDokument5 SeitenUnderstanding Bio ElectricityIonela100% (2)

- Diy - Soldering Bga Ic On PCBDokument2 SeitenDiy - Soldering Bga Ic On PCBIonela100% (3)

- How To Process Audio WAV Files in Embedded SystemsDokument4 SeitenHow To Process Audio WAV Files in Embedded SystemsIonela83% (6)

- Brand StandardsDokument33 SeitenBrand StandardsHector MatiasNoch keine Bewertungen

- Paper 2 - Option A - Databases SL/HL Core: Annotated Student Work Paper 2: Example 1Dokument9 SeitenPaper 2 - Option A - Databases SL/HL Core: Annotated Student Work Paper 2: Example 1anirudhNoch keine Bewertungen

- Ricoh Aficio MP2550 MP3350 BrochureDokument6 SeitenRicoh Aficio MP2550 MP3350 BrochureAzim TamboliNoch keine Bewertungen

- Programming Languages' Lecture Notes by Hüsnü Yenigün (CS305) (Sabancı University)Dokument259 SeitenProgramming Languages' Lecture Notes by Hüsnü Yenigün (CS305) (Sabancı University)AYasinNoch keine Bewertungen

- NCIS Los Angeles (2009) Season 6 - E.Rev 480p MKV x264Dokument2 SeitenNCIS Los Angeles (2009) Season 6 - E.Rev 480p MKV x264Stefani SeravinaNoch keine Bewertungen

- Adams - Hash Joins OracleDokument15 SeitenAdams - Hash Joins Oraclerockerabc123Noch keine Bewertungen

- SITXHRM002 Unit Assessment PackDokument55 SeitenSITXHRM002 Unit Assessment Packchan33% (6)

- Coordinate Systems Hotfix ReadmeDokument12 SeitenCoordinate Systems Hotfix ReadmebaoloilongNoch keine Bewertungen

- Rational Unified ProcessDokument40 SeitenRational Unified ProcessNitesh INoch keine Bewertungen

- CMQS 12.c-R IGDokument326 SeitenCMQS 12.c-R IGbajantrinaNoch keine Bewertungen

- Ripspeed DV740 User GuideDokument47 SeitenRipspeed DV740 User GuideRadu Baciu-NiculescuNoch keine Bewertungen

- RANSAC Vs ICP PDFDokument15 SeitenRANSAC Vs ICP PDFSaransh Vora100% (1)

- Logix Um003 - en PDokument113 SeitenLogix Um003 - en PVinícius LemosNoch keine Bewertungen

- BCSL-022Dokument7 SeitenBCSL-022Sagnik BairagyaNoch keine Bewertungen

- Fundamental Data ConceptDokument12 SeitenFundamental Data Conceptpisabandmut100% (1)

- Using Oracle ShardingDokument273 SeitenUsing Oracle ShardingNikolya SmirnoffNoch keine Bewertungen

- Tobii User Story - Scott McGuireDokument1 SeiteTobii User Story - Scott McGuireTobii AACNoch keine Bewertungen

- PDF 411 YoNFT - Com Pitch DeckDokument19 SeitenPDF 411 YoNFT - Com Pitch DeckIgor KubalskiyNoch keine Bewertungen

- NA Lec 15Dokument15 SeitenNA Lec 15hamidNoch keine Bewertungen

- What Is ManageabilityDokument5 SeitenWhat Is Manageabilitynearurheart1Noch keine Bewertungen

- Epm High AvailabilityDokument36 SeitenEpm High Availabilityزكي الدين الهلاليNoch keine Bewertungen

- Cooter Ulen - Law.and - EconomicsDokument477 SeitenCooter Ulen - Law.and - EconomicsMychy2010100% (2)

- Check Point Full Disk EncryptionDokument16 SeitenCheck Point Full Disk EncryptionDun HillNoch keine Bewertungen

- ADF TrainingDokument42 SeitenADF TrainingdeepaksatiecNoch keine Bewertungen

- Aarush T N MishraDokument2 SeitenAarush T N MishraAyush AgarwalNoch keine Bewertungen

- Aadhaar Seeding in Multiple Bank Accounts of Same CustomerDokument8 SeitenAadhaar Seeding in Multiple Bank Accounts of Same CustomerSandeep KumarNoch keine Bewertungen

- Distributed Systems Operating Systems: Björn Franke University of Edinburgh 2015/2016Dokument30 SeitenDistributed Systems Operating Systems: Björn Franke University of Edinburgh 2015/2016Salar AhmedNoch keine Bewertungen

- Inventory Management Unit IIDokument42 SeitenInventory Management Unit IIMUDITSAHANINoch keine Bewertungen

- Final Proposal EditedDokument34 SeitenFinal Proposal Editedshankar bcNoch keine Bewertungen

- Topic 5: Lesson 1: Configuring, Managing, and Troubleshooting Resource AccessDokument53 SeitenTopic 5: Lesson 1: Configuring, Managing, and Troubleshooting Resource AccessarivsNoch keine Bewertungen