Beruflich Dokumente

Kultur Dokumente

Pipelines - #1 RISC ISA Without Pipe

Hochgeladen von

Hussain HajjarOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Pipelines - #1 RISC ISA Without Pipe

Hochgeladen von

Hussain HajjarCopyright:

Verfügbare Formate

Hennessy and Patterson, Computer Architecture a Quantitative Approach (4th Ed) Appendix A Instruction Set Pipelining

Pipelines - #1 RISC ISA without pipe

RISC Reduced Instruction Set Computer or Load-Store machine is an ISA that came to prominence in the 1980s and popularized the utilization of pipelines in instruction set architectures (IBM mainframe computers pioneered the utilization of pipelines 2 decades earlier!). RISC architectures generally considered to consist of the following 3 properties, o All operations on data apply to registers alone, affecting the entire register content (32 or 64 bit); o Only load (memory to register transfer) and store (register to memory) operations may involve memory; o Minimalist provision for different instruction formats, with all instructions typically being the same number of bytes. e.g. Opcode Target Source1 Immediate/ Source2 Register-level Transfer Language : (a) Instruction with immediate operand: Target Source OPCODE Immediate (b) Instruction with two registers: Target Source1 OPCODE Source2 Opcode examples ADD DADD DADDI DADDUI AND OR Add Add, double Add, double, immediate Add, double, unsigned immediate Logical, no differentiation between 32 or 64 bit Source Two Registers Register and Sign extended immediate Register Target The above generic series of properties result in the fetch-decode-execute cycle having predicable properties (with respect to a Complex Instruction Set Computer CISC). In addition most RISC architectures have three classes of instruction, 1. ALU instructions

Malcolm Heywood CSCI3121 Dalhousie University FCS

Hennessy and Patterson, Computer Architecture a Quantitative Approach (4th Ed) Appendix A Instruction Set Pipelining

2. Load-Store instructions Operand (address) (Effective) Address Calculation Load register detailing Base Register AND (sign extended) offset Offset + base register content destination for loaded data. Store register detailing data for storage. 3. Branch or jump instructions Comparison Operand Register to register, or Register to zero Test Specified by opcode Destination ID Add sign extended offset to PC Operand (register)

NOTE RTL and tables summarize example format, but should not be considered as a practical pipelined architecture!

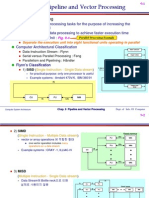

Implementation of RISC ISA

Having defined the basic instruction types now in a position to consider the requirements of a generic fetch-decode-execute cycle. Consider case of NO PIPELINE and then modify for pipelined case. Generic design decisions, o Determine the number of stages; o Determine any special purpose register requirements. 1. Consider, Instruction Fetch (IF) IR Mem[PC] NPC PC + 4; 2. Instruction Decode/ Register Fetch (ID) A Reg[IR(source1)]; B Reg[IR(source2)]; // load 32 bit word // memory is byte addressable // extract source1 // extract source2

Imm (sign ext.)##IR(Immediate); // extract immediate

Malcolm Heywood CSCI3121 Dalhousie University FCS

Hennessy and Patterson, Computer Architecture a Quantitative Approach (4th Ed) Appendix A Instruction Set Pipelining

3.

Execution/ Effective Address (EX)

One of 4 cases depending on the ID stage, (a) Memory Reference, ALU(out) A + Imm (b) Register-Register ALU operation, ALU(out) A opcode B (c) Register Immediate ALU instruction, ALU(out) A opcode Imm (d) Branch, ALU(out) NPC + Imm Cond (A opcode 0)

4.

Memory Access (MEM)

PC NPC One of either, (a) Memory reference, LMD Mem[ALU(out)] Mem[ALU(out)] B (b) Branch, IF (cond) THEN PC ALU(out) ; or

5.

Write-back (WB)

In the case of a register ALU operation OR a load instruction we need to update the register contents to reflect the new values. (a) Register-Register ALU instruction, Reg[target] ALUout (b) Register-Immediate ALU instruction, Reg[target] ALUout (c) Load Instruction, Reg[target] LMD

Figure 1 summarizes the 5 stages. Note (a) PC and registers are shown in stages corresponding to their read position.

Malcolm Heywood CSCI3121 Dalhousie University FCS

Hennessy and Patterson, Computer Architecture a Quantitative Approach (4th Ed) Appendix A Instruction Set Pipelining

(b) Multiplexers indicate location of write for PC and registers AND the temporal dependency in this decision. (c) Backward flowing dependency will cause problems for efficient operation of any pipelining.

Figure 1: MIPS RISC data path. Comments, Branch and Store complete in 4 cycles; All other instruction types complete in 5 cycles; ALU instructions idle in MEM stage, so an optimal implementation (without pipelining) would complete ALU instructions here. Two ALUs would not be necessary if we where not interested in basing our pipeline implementation on this. Registers for storing intermediate results would also not be necessary.

Nave RISC Instruction Pipeline

General objective of our instruction pipeline is to overlap the execution of each stage of the fetch-decode-execute cycle in the above example RISC ISA. Ideally this results in the following summary of operation, 4

Malcolm Heywood CSCI3121 Dalhousie University FCS

Hennessy and Patterson, Computer Architecture a Quantitative Approach (4th Ed) Appendix A Instruction Set Pipelining

Instruction 1 i i+1 i+2 i+3 i+4 IF 2 ID IF 3 EX ID IF 4 MEM EX ID IF

Clock 5 WB MEM EX ID IF WB MEM EX ID WB MEM EX WB MEM WB 6 7 8 9

Figure 1 indicates that the following pipeline hazards exist, o Structural or Resource Hazards Hardware cannot be shared between different stages (two ALUs in figure 1 to avoid this). o Data Hazards operation of one instruction dependent on the result from the previous instruction. Why is this not permissible? contents of PC changed by a branch or jump instruction. Why might this be a problem? o Control Hazards

Some Structural Hazards

The data path for our RISC fetch-decode-execute pipe is shown in figure 2. o Major functional units need to appear in different cycles. Is this the case? avoid any conflict between DM and IM; implies memory BW increases by 5 if clock period unchanged with respect to an architecture without the pipeline Why? o Internal Registers utilized twice in the same cycle, i.e. Read from register in ID; 5 o Instruction and Data memory should be independent (use different buses)

Malcolm Heywood CSCI3121 Dalhousie University FCS

Hennessy and Patterson, Computer Architecture a Quantitative Approach (4th Ed) Appendix A Instruction Set Pipelining

Write to register in WB; How can we deal with this?

Figure 2: Generic 5-stage pipe. o PC needs to change every clock cycleimplications? Figure 1 indicates that: Separate ALU necessary for NPC calculation AND branch offset calculation; Dont know the result of branch until 3 stages later! o Necessary to save the complete state of each instruction as it progresses between different pipeline stage. Pipeline registers provide this, as per figure 3;

Malcolm Heywood CSCI3121 Dalhousie University FCS

Hennessy and Patterson, Computer Architecture a Quantitative Approach (4th Ed) Appendix A Instruction Set Pipelining

Figure 3: Pipeline registers isolate each stage by propagating the value of local registers as each instruction passes through the pipe.

Summary

RISC ISA provided a suitable framework for understanding instruction pipelines leading their widespread introduction into micro-processor chip sets in the 1980s. Instruction pipelines o force a series of constraints on the ISA; o result in duplicated hardware between stages; o very sensitive to branch type instructions.

Malcolm Heywood CSCI3121 Dalhousie University FCS

Hennessy and Patterson, Computer Architecture a Quantitative Approach (4th Ed) Appendix A Instruction Set Pipelining

Example #1

With respect to the nave 5-stage RISC piped and unpiped architectures, let, Clock period be 1ns; ALU and branch instructions take 4 cycles; Memory operations take 5 cycles; Frequency of ALU instruction is 40%; Frequency of branch instruction is 20%; Frequency of memory instruction is 40%; Additional complexity of a pipeline adds 0.2ns to the clock period; 1. Why do ALU and branch instructions complete one clock cycle faster than memory instructions? 2. Assuming a full pipe and no hazards, how much speed up does the piped architecture provide with respect to the architecture without a pipe?

Question:

Example #2

Consider the case of an architecture in which separate instruction and data buses do not exist. With respect to figure 4, a data load at instruction #0 causes a structural hazard with the instruction fetch at instruction #1. The instruction being fetched is therefore stalled delaying instruction #3 and all following instructions by one clock cycle and increasing the CPI of the pipeline, figure 5. Let the following conditions hold, CPI of the pipe without stalls is 1; Data load/ store instructions constitute 40% of the instruction mix; Frequency of the pipe encountering stalls is 1.05 times higher than the pipe without stalls. 1. What is the speedup of the pipe that avoids stalls? 2. If such a stall is so detrimental to the operation of a pipeline, are there any conditions under which structural hazards of this nature might be permitted?

Questions:

Malcolm Heywood CSCI3121 Dalhousie University FCS

Hennessy and Patterson, Computer Architecture a Quantitative Approach (4th Ed) Appendix A Instruction Set Pipelining

Figure 4: Effect of single port memory on generic 5-stage pipe. Instruction 1 i i+1 i+2 i+3 i+4 IF 2 ID IF 3 EX ID IF 4 MEM EX ID stall Clock 5 WB MEM EX IF WB MEM ID IF WB EX ID MEM EX WB MEM 6 7 8 9

Figure 5: Case of structural hazard introduced by single port memory.

Malcolm Heywood CSCI3121 Dalhousie University FCS

Das könnte Ihnen auch gefallen

- Ovn MainDokument54 SeitenOvn MainAvenir BajraktariNoch keine Bewertungen

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationVon EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNoch keine Bewertungen

- Attempt All of The Following QuestionsDokument5 SeitenAttempt All of The Following Questionssoli0snakeNoch keine Bewertungen

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Von EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Noch keine Bewertungen

- Introduction To MIPS ArchitectureDokument10 SeitenIntroduction To MIPS ArchitectureJahanzaib AwanNoch keine Bewertungen

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxVon EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxBewertung: 4 von 5 Sternen4/5 (1)

- Embedded Systems Design: Pipelining and Instruction SchedulingDokument48 SeitenEmbedded Systems Design: Pipelining and Instruction SchedulingMisbah Sajid ChaudhryNoch keine Bewertungen

- Computer Architecture: Pipelining: Dr. Ashok Kumar TurukDokument136 SeitenComputer Architecture: Pipelining: Dr. Ashok Kumar TurukkoottyNoch keine Bewertungen

- Iat-4 McesDokument12 SeitenIat-4 Mcesbhatt bhattNoch keine Bewertungen

- The Big Picture: Requirements Algorithms Prog. Lang./Os Isa Uarch Circuit DeviceDokument60 SeitenThe Big Picture: Requirements Algorithms Prog. Lang./Os Isa Uarch Circuit DevicevshlvvkNoch keine Bewertungen

- Pipelining Computer Architecture LectureDokument42 SeitenPipelining Computer Architecture LectureUap OrlandinhoNoch keine Bewertungen

- Unit 05 Design Space of PipelinesDokument24 SeitenUnit 05 Design Space of PipelinesSrinivasaRaoNoch keine Bewertungen

- UNIT-5: Pipeline and Vector ProcessingDokument63 SeitenUNIT-5: Pipeline and Vector ProcessingAkash KankariaNoch keine Bewertungen

- Computer Architecture AllClasses-Outline-100-198Dokument99 SeitenComputer Architecture AllClasses-Outline-100-198SrinivasaRaoNoch keine Bewertungen

- Homework 2Dokument8 SeitenHomework 2Deepak BegrajkaNoch keine Bewertungen

- CH7-Parallel and Pipelined ProcessingDokument23 SeitenCH7-Parallel and Pipelined Processingaashifr469Noch keine Bewertungen

- Comp Architecture Sample QuestionsDokument9 SeitenComp Architecture Sample QuestionsMohamaad SihatthNoch keine Bewertungen

- Computer Architecture Lab NotesDokument15 SeitenComputer Architecture Lab Notesአንድነት togetherNoch keine Bewertungen

- CSE 820 Graduate Computer Architecture Week 5 - Instruction Level ParallelismDokument38 SeitenCSE 820 Graduate Computer Architecture Week 5 - Instruction Level ParallelismkbkkrNoch keine Bewertungen

- The Pipelined RiSC-16 ComputerDokument9 SeitenThe Pipelined RiSC-16 Computerkb_lu232Noch keine Bewertungen

- CA Classes-121-125Dokument5 SeitenCA Classes-121-125SrinivasaRaoNoch keine Bewertungen

- Your Name:: Final ExamDokument9 SeitenYour Name:: Final ExamDaniel EcheverriaNoch keine Bewertungen

- Cad For Vlsi 2 Pro Ject - Superscalar Processor ImplementationDokument10 SeitenCad For Vlsi 2 Pro Ject - Superscalar Processor ImplementationkbkkrNoch keine Bewertungen

- 01 Mik EngDokument34 Seiten01 Mik EngrbokisNoch keine Bewertungen

- 21CS34 SIMP Questions - 21SCHEME: Module-1 (Study Any 5 Questions)Dokument4 Seiten21CS34 SIMP Questions - 21SCHEME: Module-1 (Study Any 5 Questions)Rohan RNoch keine Bewertungen

- Instruction Level Parallelism: PipeliningDokument6 SeitenInstruction Level Parallelism: PipeliningkbkkrNoch keine Bewertungen

- Instruction Pipeline Design, Arithmetic Pipeline Deign - Super Scalar Pipeline DesignDokument34 SeitenInstruction Pipeline Design, Arithmetic Pipeline Deign - Super Scalar Pipeline DesignMarlon TugweteNoch keine Bewertungen

- Homework3 Solution v2Dokument41 SeitenHomework3 Solution v2razi haiderNoch keine Bewertungen

- Updated Solution Manual For Modern Processor Design by John Paul Shen and Mikko H. LipastiDokument8 SeitenUpdated Solution Manual For Modern Processor Design by John Paul Shen and Mikko H. LipastitargetiesNoch keine Bewertungen

- Solution Manual For Modern Processor Design by John Paul Shen and Mikko H. LipastiDokument11 SeitenSolution Manual For Modern Processor Design by John Paul Shen and Mikko H. LipastitargetiesNoch keine Bewertungen

- Full Solution Manual For Modern Processor Design by John Paul Shen and Mikko H. Lipasti PDFDokument18 SeitenFull Solution Manual For Modern Processor Design by John Paul Shen and Mikko H. Lipasti PDFtargetiesNoch keine Bewertungen

- Full Solution Manual For Modern Processor Design by John Paul Shen and Mikko H. LipastiDokument27 SeitenFull Solution Manual For Modern Processor Design by John Paul Shen and Mikko H. Lipastitargeties50% (2)

- Lecture6 ARMDokument50 SeitenLecture6 ARMRohith ThurlapatiNoch keine Bewertungen

- Question Bank - M5 To M7Dokument2 SeitenQuestion Bank - M5 To M7Pieter MarkerNoch keine Bewertungen

- Input Unit: Five Basic Components of Computer SystemDokument9 SeitenInput Unit: Five Basic Components of Computer SystemJefin PaulNoch keine Bewertungen

- Internal Structure of CPUDokument5 SeitenInternal Structure of CPUSaad KhanNoch keine Bewertungen

- Microprocessor Module-5 Question AnswersDokument8 SeitenMicroprocessor Module-5 Question AnswersShubham BargeNoch keine Bewertungen

- MCQsDokument19 SeitenMCQsansalvNoch keine Bewertungen

- Practice QuestionsDokument1 SeitePractice QuestionsSwastik swarup meherNoch keine Bewertungen

- CA Classes-106-110Dokument5 SeitenCA Classes-106-110SrinivasaRaoNoch keine Bewertungen

- RISC Instruction Set:: I) Data Manipulation InstructionsDokument8 SeitenRISC Instruction Set:: I) Data Manipulation InstructionsSwarup BharNoch keine Bewertungen

- Risc in Pipe IneDokument39 SeitenRisc in Pipe IneNagarjuna ReddyNoch keine Bewertungen

- ch09 Morris ManoDokument15 Seitench09 Morris ManoYogita Negi RawatNoch keine Bewertungen

- Computer Architecture Pipelining AssignmentDokument1 SeiteComputer Architecture Pipelining Assignmentsomsom39Noch keine Bewertungen

- Pipeline Data Hazards: Example #1 - Write-Back Data HazardDokument6 SeitenPipeline Data Hazards: Example #1 - Write-Back Data HazardVardhan RoyNoch keine Bewertungen

- Pipelining and ParallelismDokument41 SeitenPipelining and ParallelismPratham GuptaNoch keine Bewertungen

- Comparing FPGA Design Flows for Area, Delay, Routability and CPU TimeDokument2 SeitenComparing FPGA Design Flows for Area, Delay, Routability and CPU TimedasdsasadNoch keine Bewertungen

- 5 6Dokument26 Seiten5 6cn3588Noch keine Bewertungen

- Pipelining and Vector ProcessingDokument28 SeitenPipelining and Vector ProcessingBinuVargisNoch keine Bewertungen

- EE380 Spring 2004 Sample Final Exam: Direct Connection (Aka, Fully Connected) Networ Ks Offer Ver y Good Latency andDokument7 SeitenEE380 Spring 2004 Sample Final Exam: Direct Connection (Aka, Fully Connected) Networ Ks Offer Ver y Good Latency andJaxzen42Noch keine Bewertungen

- CpSc 418/538E Midterm February 28, 2007Dokument4 SeitenCpSc 418/538E Midterm February 28, 2007EasyNoch keine Bewertungen

- ILP - Appendix C PDFDokument52 SeitenILP - Appendix C PDFDhananjay JahagirdarNoch keine Bewertungen

- 3 Introduction PipelineDokument149 Seiten3 Introduction PipelineIshwar MhtNoch keine Bewertungen

- DSP-8 (DSP Processors)Dokument8 SeitenDSP-8 (DSP Processors)Sathish BalaNoch keine Bewertungen

- Ca07 2014 PDFDokument56 SeitenCa07 2014 PDFPance CvetkovskiNoch keine Bewertungen

- Instruction TypesDokument13 SeitenInstruction TypesShubham GoswamiNoch keine Bewertungen

- CPU Registers Document ExplainedDokument35 SeitenCPU Registers Document ExplainedanandNoch keine Bewertungen

- National University of Computer and Emerging Sciences, Lahore CampusDokument4 SeitenNational University of Computer and Emerging Sciences, Lahore CampusxxxNoch keine Bewertungen

- Computer Organization and Architecture Model Question PaperDokument3 SeitenComputer Organization and Architecture Model Question PaperPrateekMandiNoch keine Bewertungen

- Heroes of Might and Magic 5 Cheats, Codes, Cheat Codes, Walkthrough, Guide, FAQDokument6 SeitenHeroes of Might and Magic 5 Cheats, Codes, Cheat Codes, Walkthrough, Guide, FAQNumpangNampangNoch keine Bewertungen

- Номенклатура Оборудования 1 (Данфос)Dokument100 SeitenНоменклатура Оборудования 1 (Данфос)Даниил СторчеусNoch keine Bewertungen

- VLSI Design Margin and Reliability ScalingDokument17 SeitenVLSI Design Margin and Reliability ScalingRapolu SushmaNoch keine Bewertungen

- QuestionDokument80 SeitenQuestionRodalie Vale CruzNoch keine Bewertungen

- Pipeline and Vector ProcessingDokument18 SeitenPipeline and Vector Processingnancy_01Noch keine Bewertungen

- Getting Started Guide IPM 8Dokument24 SeitenGetting Started Guide IPM 8ojrfgmrfNoch keine Bewertungen

- BlackBerry 10 OS Version 10.3.2 10.3.1.2576-10.3.2.2474Dokument23 SeitenBlackBerry 10 OS Version 10.3.2 10.3.1.2576-10.3.2.2474MahmoudNoch keine Bewertungen

- CDD 000-900Dokument745 SeitenCDD 000-900Isabela LustosaNoch keine Bewertungen

- KT-300 Installation Manual en DN1315-0707Dokument22 SeitenKT-300 Installation Manual en DN1315-0707silviosergio2Noch keine Bewertungen

- Seminar On HDL's and HVL'sDokument25 SeitenSeminar On HDL's and HVL'sharishkashaNoch keine Bewertungen

- Lab 4 Homework Heathrow QSDokument2 SeitenLab 4 Homework Heathrow QSsumsum12210% (2)

- Cumulus System RequirementsDokument2 SeitenCumulus System RequirementsRicardo Espinosa ReoNoch keine Bewertungen

- 2018 Arduino Projects List About 2745 Arduino List of ProjectsUse Arduino For Projects PDFDokument148 Seiten2018 Arduino Projects List About 2745 Arduino List of ProjectsUse Arduino For Projects PDFSCORSAM1100% (1)

- Asus VW193DRDokument71 SeitenAsus VW193DRbawbawerert34Noch keine Bewertungen

- 6320 Ma Pa Va ManualDokument238 Seiten6320 Ma Pa Va ManualJose GarciaNoch keine Bewertungen

- Automatic Hand SanitizerDokument47 SeitenAutomatic Hand SanitizerAbhishek DhimanNoch keine Bewertungen

- How To Draw A Semi Realistic CharacterDokument12 SeitenHow To Draw A Semi Realistic CharacterLars Christevandersson100% (1)

- 2016 Paper FirmadyneDokument16 Seiten2016 Paper FirmadyneBuRnerNoch keine Bewertungen

- BSCDokument10 SeitenBSCmonu 490Noch keine Bewertungen

- 05 AbstractsDokument24 Seiten05 AbstractsMukta DebnathNoch keine Bewertungen

- BK Precision CatalogDokument118 SeitenBK Precision CatalogTony WilliamsNoch keine Bewertungen

- Unix ProgramsDokument20 SeitenUnix ProgramsSupriya KakaraddiNoch keine Bewertungen

- Aster Analytics Foundation 0510Dokument611 SeitenAster Analytics Foundation 0510Emanuele ParenteNoch keine Bewertungen

- Device drivers and hardware IDsDokument3 SeitenDevice drivers and hardware IDsGuin PintNoch keine Bewertungen

- Goldstar Chassis Nc-5aa Cn-14a30h Cn-14 20b30h Cn-20h10Dokument5 SeitenGoldstar Chassis Nc-5aa Cn-14a30h Cn-14 20b30h Cn-20h10Airam MelendezNoch keine Bewertungen

- Iolmaster 5 PDFDokument117 SeitenIolmaster 5 PDFJose MorenoNoch keine Bewertungen

- CA4500 - 4 Reader Access Control Board: NEW - The Control Board May Require Setting S2 DIPDokument2 SeitenCA4500 - 4 Reader Access Control Board: NEW - The Control Board May Require Setting S2 DIPLuis Huerta100% (1)

- 6SL3210 1PE32 5UL0 Datasheet enDokument2 Seiten6SL3210 1PE32 5UL0 Datasheet enHernando RomeroNoch keine Bewertungen

- Competency MatrixDokument1 SeiteCompetency MatrixEdleo MaghopoyNoch keine Bewertungen

- U8668-D DatasheetDokument42 SeitenU8668-D DatasheetOrlando Emilio TachéNoch keine Bewertungen