Beruflich Dokumente

Kultur Dokumente

74HC HCT4066 NXP

Hochgeladen von

prpabst8514Originalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

74HC HCT4066 NXP

Hochgeladen von

prpabst8514Copyright:

Verfügbare Formate

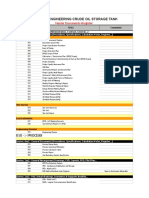

INTEGRATED CIRCUITS

DATA SHEET

74HC4066; 74HCT4066 Quad bilateral switches

Product specication Supersedes data of 2003 Jun 17 2004 Nov 11

Philips Semiconductors

Product specication

Quad bilateral switches

74HC4066; 74HCT4066

FEATURES Very low ON-resistance: 50 (typical) at VCC = 4.5 V 45 (typical) at VCC = 6.0 V 35 (typical) at VCC = 9.0 V. Complies with JEDEC standard no. 7A ESD protection: HBM EIA/JESD22-A114-B exceeds 2000 V MM EIA/JESD22-A115-A exceeds 200 V. Specified from 40 C to +85 C and 40 C to +125 C.

GENERAL DESCRIPTION The 74HC4066 and 74HCT4066 are high-speed Si-gate CMOS devices and are pin compatible with the HEF4066B. They are specified in compliance with JEDEC standard no. 7A. The 74HC4066 and 74HCT4066 have four independent analog switches. Each switch has two input/output pins (pins nY or nZ) and an active HIGH enable input pin (pin nE). When pin nE = LOW the belonging analog switch is turned off. The 74HC4066 and 74HCT4066 are pin compatible with the 74HC4016 and 74HCT4016 but exhibit a much lower on-resistance. In addition, the on-resistance is relatively constant over the full input signal range.

QUICK REFERENCE DATA GND = 0 V; Tamb = 25 C; tr = tf = 6 ns. TYPICAL SYMBOL tPZH/tPZL tPHZ/tPLZ CI CPD CS Notes 1. CPD is used to determine the dynamic power dissipation (PD in W). PD = CPD VCC2 fi N + [(CL + CS) VCC2 fo] where: fi = input frequency in MHz; fo = output frequency in MHz; CL = output load capacitance in pF; CS = maximum switch capacitance in pF; VCC = supply voltage in V; N = number of inputs switching; [(CL + CS) VCC2 fo] = sum of the outputs. 2. For 74HC4066 the condition is VI = GND to VCC. For 74HCT4066 the condition is VI = GND to VCC 1.5 V. PARAMETER turn-on time nE to Vos turn-off time nE to Vos input capacitance power dissipation capacitance per switch maximum switch capacitance notes 1 and 2 CONDITIONS 74HC4066 CL = 15 pF; RL = 1 k; VCC = 5 V CL = 15 pF; RL = 1 k; VCC = 5 V 11 13 3.5 11 8 74HCT4066 12 16 3.5 12 8 ns ns pF pF pF UNIT

2004 Nov 11

Philips Semiconductors

Product specication

Quad bilateral switches

74HC4066; 74HCT4066

FUNCTION TABLE See note 1. INPUT nE L H Note 1. H = HIGH voltage level. L = LOW voltage level. ORDERING INFORMATION PACKAGE TYPE NUMBER TEMPERATURE RANGE 74HC4066N 74HCT4066N 74HC4066D 74HCT4066D 74HC4066DB 74HCT4066DB 74HC4066PW 74HCT4066PW 74HC4066BQ 74HCT4066BQ PINNING PIN 1 2 3 4 5 6 7 8 9 10 11 12 13 14 SYMBOL 1Y 1Z 2Z 2Y 2E 3E GND 3Y 3Z 4Z 4Y 4E 1E VCC DESCRIPTION independent input/output independent input/output independent input/output independent input/output enable input (active HIGH) enable input (active HIGH) ground (0 V) independent input/output independent input/output independent input/output independent input/output enable input (active HIGH) enable input (active HIGH) supply voltage Fig.1 Pin configuration DIP14, SO14 and (T)SSOP14.

2Y 2E 3E GND 4 5 6 7

MGR253

SWITCH off on

PINS 14 14 14 14 14 14 14 14 14 14

PACKAGE DIP14 DIP14 SO14 SO14 SSOP14 SSOP14 TSSOP14 TSSOP14 DHVQFN14 DHVQFN14

MATERIAL plastic plastic plastic plastic plastic plastic plastic plastic plastic plastic

CODE SOT27-1 SOT27-1 SOT108-1 SOT108-1 SOT337-1 SOT337-1 SOT402-1 SOT402-1 SOT762-1 SOT762-1

40 C to 125 C 40 C to 125 C 40 C to 125 C 40 C to 125 C 40 C to 125 C 40 C to 125 C 40 C to 125 C 40 C to 125 C 40 C to 125 C 40 C to 125 C

handbook, halfpage

1Y 1Z 2Z

1 2 3

14 VCC 13 1E 12 4E

4066

11 4Y 10 4Z 9 3Z

8 3Y

2004 Nov 11

Philips Semiconductors

Product specication

Quad bilateral switches

74HC4066; 74HCT4066

terminal 1 index area 1Z 2Z 2Y 2E 3E 2 3 4 5 6

14 VCC

1Y

handbook, halfpage

13 1E 12 4E

1Y 13 1E 1Z 2Y 2Z 3Y 3Z 4Y 4Z

MGR254

1 2 4 3 8 9 11 10

4066

VCC(1) 7 8

11 4Y 10 4Z 9 3Z

2E

3E

GND

3Y

001aac116

12

4E

Transparent top view

(1) The die substrate is attached to this pad using conductive die attach material. It can not be used as a supply pin or input.

Fig.2 Pin configuration DHVQFN14.

Fig.3 Logic symbol.

handbook, halfpage handbook, halfpage

1 13 #

1 X1

1 13 # 4 5 # 8 6 # 11 12 #

MGR255

4 5 #

1 X1

8 6 #

1 X1

10 11 12 # 1 X1

MGR256

10

Fig.4 IEEEC logic symbol.

2004 Nov 11

Philips Semiconductors

Product specication

Quad bilateral switches

74HC4066; 74HCT4066

handbook, halfpage

nY

13 handbook, halfpage 1E

1 1Y

5 2E

4 2Y

6 3E

8 3Y

12 4E

11 4Y nE

1Z 2

2Z 3

3Z 9

4Z 10

MGR257

VCC

VCC

GND

nZ

MGR258

Fig.5 Functional diagram.

Fig.6 Schematic diagram (one switch).

2004 Nov 11

Philips Semiconductors

Product specication

Quad bilateral switches

74HC4066; 74HCT4066

RECOMMENDED OPERATING CONDITIONS 74HC4066 SYMBOL VCC VI VS Tamb PARAMETER supply voltage input voltage switch voltage ambient temperature see DC and AC characteristics per device VCC = 2.0 V VCC = 4.5 V VCC = 6.0 V VCC = 10.0 V CONDITIONS MIN. 2.0 GND GND 40 40 TYP. 5.0 +25 6.0 MAX. 10.0 VCC VCC +85 +125 1000 500 400 250 MIN. 4.5 GND GND 40 40 TYP. 5.0 +25 6.0 MAX. 5.5 VCC VCC +85 +125 500 V V V C C ns ns ns ns 74HCT4066 UNIT

tr, tf

input rise and fall times

LIMITING VALUES In accordance with the Absolute Maximum Rating System (IEC 60134); voltages are referenced to GND (ground = 0 V). SYMBOL VCC IIK ISK IS ICC, IGND Tstg Ptot PS Notes 1. To avoid drawing VCC current out of pin nZ, when switch current flows in pin nY, the voltage drop across the bidirectional switch must not exceed 0.4 V. If the switch current flows into pin nZ, no VCC current will flow out of pin nY. In this case there is no limit for the voltage drop across the switch, but the voltages at pins nY and nZ may not exceed VCC or GND. 2. For DIP14 packages: above 70 C derate linearly with 12 mW/K. For SO14 packages: above 70 C derate linearly with 8 mW/K. For SSOP14 and TSSOP16 packages: above 60 C derate linearly with 5.5 mW/K. For DHVQFN14 packages: above 60 C derate linearly with 4.5 mW/K. PARAMETER supply voltage input diode current switch diode current switch current VCC or GND current storage temperature power dissipation power dissipation per switch Tamb = 40 C to +125 C; note 2 VI < 0.5 V or VI > VCC + 0.5 V VS < 0.5 V or VS > VCC + 0.5 V 0.5 V < VO < VCC + 0.5 V; note 1 CONDITIONS MIN. 0.5 65 MAX. +11.0 20 20 25 50 +150 500 100 UNIT V mA mA mA mA C mW mW

2004 Nov 11

Philips Semiconductors

Product specication

Quad bilateral switches

74HC4066; 74HCT4066

DC CHARACTERISTICS Family 74HC4066 Voltages are referenced to GND (ground = 0 V); Vis is the input voltage at pins nY or nZ, whichever is assigned as an input; Vos is the output voltage at pins nY or nZ, whichever is assigned as an output. TEST CONDITIONS SYMBOL PARAMETER OTHER Tamb = 40 C to +85 C; note 1 VIH HIGH-level input voltage 2.0 4.5 6.0 9.0 VIL LOW-level input voltage 2.0 4.5 6.0 9.0 ILI IS(OFF) IS(ON) ICC input leakage current analog switch current OFF-state analog switch current ON-state quiescent supply current VI = VCC or GND per channel; VI = VIH or VIL; VS = VCC GND; see Fig.7 VI = VIH or VIL; VS = VCC GND; see Fig.8 VI = VCC or GND; Vis = GND or VCC; Vos = VCC or GND 6.0 10.0 10.0 10.0 6.0 10.0 1.5 3.15 4.2 6.3 1.2 2.4 3.2 4.7 0.8 2.1 2.8 4.3 0.50 1.35 1.80 2.70 1.0 2.0 1.0 1.0 20.0 40.0 V V V V V V V V A A A A A A VCC (V) MIN. TYP. MAX. UNIT

2004 Nov 11

Philips Semiconductors

Product specication

Quad bilateral switches

74HC4066; 74HCT4066

TEST CONDITIONS SYMBOL PARAMETER OTHER Tamb = 40 C to +125 C VIH HIGH-level input voltage 2.0 4.5 6.0 9.0 VIL LOW-level input voltage 2.0 4.5 6.0 9.0 ILI IS(OFF) IS(ON) ICC Note 1. All typical values are measured at Tamb = 25 C. input leakage current analog switch current OFF-state analog switch current ON-state quiescent supply current VI = VCC or GND per channel; VI = VIH or VIL; VS = VCC GND; see Fig.7 VI = VIH or VIL; VS = VCC GND; see Fig.8 VI = VCC or GND; Vis = GND or VCC; Vos = VCC or GND 6.0 10.0 10.0 10.0 6.0 10.0 1.5 3.15 4.2 6.3 0.50 1.35 1.80 2.70 1.0 2.0 1.0 1.0 40.0 80.0 V V V V V V V V A A A A A A VCC (V) MIN. TYP. MAX. UNIT

2004 Nov 11

Philips Semiconductors

Product specication

Quad bilateral switches

74HC4066; 74HCT4066

Family 74HCT4066 Voltages are referenced to GND (ground = 0 V); Vis is the input voltage at pins nY or nZ, whichever is assigned as an input; Vos is the output voltage at pins nY or nZ, whichever is assigned as an output. TEST CONDITIONS SYMBOL PARAMETER OTHER Tamb = 40 C to +85 C; note 1 VIH VIL ILI IS(OFF) IS(ON) ICC ICC HIGH-level input voltage LOW-level input voltage input leakage current analog switch current OFF-state analog switch current ON-state quiescent supply current VI = VCC or GND per channel; VI = VIH or VIL; VS = VCC GND; see Fig.7 VI = VIH or VIL; VS = VCC GND; see Fig.8 VI = VCC or GND; Vis = GND or VCC; Vos = VCC or GND 4.5 to 5.5 2.0 4.5 to 5.5 5.5 5.5 5.5 1.6 1.2 100 0.8 1.0 1.0 1.0 20.0 450 V V A A A A A VCC (V) MIN. TYP. MAX. UNIT

4.5 to 5.5 4.5 to 5.5

additional quiescent VI = VCC 2.1 V; other inputs at VCC supply current per input or GND

Tamb = 40 C to +125 C VIH VIL ILI IS(OFF) IS(ON) ICC ICC Note 1. All typical values are measured at Tamb = 25 C. HIGH-level input voltage LOW-level input voltage input leakage current analog switch current OFF-state analog switch current ON-state quiescent supply current VI = VCC or GND per channel; VI = VIH or VIL; VS = VCC GND; see Fig.7 VI = VIH or VIL; VS = VCC GND; see Fig.8 VI = VCC or GND; Vis = GND or VCC; Vos = VCC or GND 4.5 to 5.5 2.0 4.5 to 5.5 5.5 10.0 10.0 0.8 1.0 1.0 1.0 40.0 490 V V A A A A A

4.5 to 5.5 4.5 to 5.5

additional quiescent VI = VCC 2.1 V; other inputs at VCC supply current per input or GND

2004 Nov 11

Philips Semiconductors

Product specication

Quad bilateral switches

74HC4066; 74HCT4066

handbook, full pagewidth

LOW (from enable inputs) nY VI = VCC or GND A nZ A

VO = GND or VCC

GND

MGR260

Fig.7 Test circuit for measuring OFF-state current.

handbook, full pagewidth

HIGH (from enable inputs) nY VI = VCC or GND A nZ A

VO (open circuit)

GND

MGR261

Fig.8 Test circuit for measuring ON-state current.

2004 Nov 11

10

Philips Semiconductors

Product specication

Quad bilateral switches

74HC4066; 74HCT4066

Resistance RON for 74HC4066 and 74HCT4066 For 74HC4066: VCC = 2.0, 4.5, 6.0 and 9.0 V; for 74HCT4066: VCC = 4.5 V; note 1; Vis is the input voltage at pins nY or nZ, whichever is assigned as an input; see Fig.9. TEST CONDITIONS SYMBOL PARAMETER OTHER Tamb = 40 C to +85 C; note 2 RON(peak) ON-resistance (peak) VI = VIH or VIL; Vis = VCC to GND 100 1000 2.0 4.5 6.0 9.0 RON(rail) ON-resistance (rail) VI = VIH or VIL; Vis = GND 100 1000 2.0 4.5 6.0 9.0 VI = VIH or VIL; Vis = VCC 100 1000 2.0 4.5 6.0 9.0 RON maximum variation of ON-resistance between any two channels VI = VIH or VIL; Vis = VCC to GND 2.0 4.5 6.0 9.0 54 42 32 80 35 27 20 100 42 35 27 5 4 3 118 105 88 95 82 70 106 94 78 IS (A) VCC (V) MIN. TYP. MAX. UNIT

Tamb = 40 C to +125 C RON(peak) ON-resistance (peak) VI = VIH or VIL; Vis = VCC to GND 100 1000 2.0 4.5 6.0 9.0 RON(rail) ON-resistance (rail) VI = VIH or VIL; Vis = GND 100 1000 2.0 4.5 6.0 9.0 VI = VIH or VIL; Vis = VCC 100 1000 2.0 4.5 6.0 9.0 Notes 1. At supply voltages approaching 2 V, the analog ON-resistance switch becomes extremely non-linear. Therefore, it is recommended that these devices are being used to transmit digital signals only, when using these supply voltages. 2. All typical values are measured at Tamb = 25 C. 142 126 105 115 100 85 128 113 95

2004 Nov 11

11

Philips Semiconductors

Product specication

Quad bilateral switches

74HC4066; 74HCT4066

handbook, full pagewidth

HIGH (from enable inputs) nY

V nZ Is GND

MGR259

Vis = 0 to VCC GND

Fig.9 Test circuit for measuring ON-resistance (RON).

handbook, halfpage

60

MGR262

RON ()

VCC = 4.5 V

50 6V 40 9V

30

20

10 0 1.8 3.6 5.4 7.2 Vis (V) 9

Vis = 0 V to VCC. Fig.10 Typical ON-resistance (RON) as a function of input voltage (Vis).

2004 Nov 11

12

Philips Semiconductors

Product specication

Quad bilateral switches

74HC4066; 74HCT4066

AC CHARACTERISTICS Type 74HC4066 GND = 0 V; tr = tf = 6 ns; CL = 50 pF; Vis is the input voltage at pins nY or nZ, whichever is assigned as an input; Vos is the output voltage at pins nY or nZ, whichever is assigned as an output. TEST CONDITIONS SYMBOL PARAMETER OTHER Tamb = 40 C to +85 C; note 1 tPHL/tPLH propagation delay Vis to Vos RL = ; see Fig.19 2.0 4.5 6.0 9.0 tPZH/tPZL turn-on time nE to Vos RL = 1 k; see Figs 20 and 21 2.0 4.5 6.0 9.0 tPHZ/tPLZ turn-off time nE to Vos RL = 1 k; see Figs 20 and 21 2.0 4.5 6.0 9.0 Tamb = 40 C to +125 C tPHL/tPLH propagation delay Vis to Vos RL = ; see Fig.19 2.0 4.5 6.0 9.0 tPZH/tPZL turn-on time nE to Vos RL = 1 k; see Figs 20 and 21 2.0 4.5 6.0 9.0 tPHZ/tPLZ turn-off time nE to Vos RL = 1 k; see Figs 20 and 21 2.0 4.5 6.0 9.0 Note 1. All typical values are measured at Tamb = 25 C. 90 18 15 12 150 30 26 20 225 45 38 30 ns ns ns ns ns ns ns ns ns ns ns ns 8 3 2 2 36 13 10 8 44 16 13 16 75 15 13 10 125 25 21 16 190 38 33 26 ns ns ns ns ns ns ns ns ns ns ns ns VCC (V) MIN. TYP. MAX. UNIT

2004 Nov 11

13

Philips Semiconductors

Product specication

Quad bilateral switches

74HC4066; 74HCT4066

Type 74HCT4066 GND = 0 V; tr = tf = 6 ns; CL = 50 pF; Vis is the input voltage at pins nY or nZ, whichever is assigned as an input; Vos is the output voltage at pins nY or nZ, whichever is assigned as an output. TEST CONDITIONS SYMBOL PARAMETER OTHER Tamb = 40 C to +85 C; note 1 tPHL/tPLH tPZH/tPZL tPHZ/tPLZ propagation delay Vis to Vos turn-on time nE to Vos turn-off time nE to Vos RL = ; see Fig.19 RL = 1 k; see Figs 20 and 21 RL = 1 k; see Figs 20 and 21 RL = ; see Fig.19 RL = 1 k; see Figs 20 and 21 RL = 1 k; see Figs 20 and 21 4.5 4.5 4.5 3 12 20 15 30 44 ns ns ns VCC (V) MIN. TYP. MAX. UNIT

Tamb = 40 C to +125 C tPHL/tPLH tPZH/tPZL tPHZ/tPLZ Note 1. All typical values are measured at Tamb = 25 C. 74HC4066 and 74HCT4066 At recommended conditions and typical values; GND = 0 V; tr = tf = 6 ns; Vis is the input voltage at pins nY or nZ, whichever is assigned as an input; Vos is the output voltage at pins nY or nZ, whichever is assigned as an output. CONDITIONS SYMBOL dsin PARAMETER OTHER sine wave distortion f = 1 kHz; RL = 10 k; CL = 50 pF; see Fig.17 Vis(p-p) (V) 4.0 8.0 VCC (V) 4.5 9.0 4.5 9.0 4.5 9.0 note 1 4.5 9.0 4.5 9.0 0.04 0.02 0.12 0.06 50 50 60 60 110 220 % % % % dB dB dB dB mV mV TYP. UNIT propagation delay Vis to Vos turn-on time nE to Vos turn-off time nE to Vos 4.5 4.5 4.5 18 36 53 ns ns ns

f = 10 kHz; RL = 10 k; CL = 50 pF; 4.0 see Fig.17 8.0 OFF(feedthr) ct(s) Vct(p-p) switch OFF signal feed-through RL = 600 ; CL = 50 pF; f = 1 MHz; see Figs 11 and 18 note 1

crosstalk between any two RL = 600 ; CL = 50 pF; f = 1 MHz; switches see Fig.13 crosstalk voltage between any input to any switch (peak-to-peak value) minimum frequency response (3 dB) maximum switch capacitance RL = 600 ; CL = 50 pF; f = 1 MHz; see Fig.15 (nE, square wave between VCC and GND, tr = tf = 6 ns) RL = 50 ; CL = 10 pF; see Figs 12 and 16

fmax CS Notes

note 2

4.5 9.0

180 200 8

MHz MHz pF

1. Adjust input voltage Vis is 0 dBM level (0 dBM = 1 mW into 600 ). 2. Adjust input voltage Vis is 0 dBM level at Vos for 1 MHz (0 dBM = 1 mW into 50 ). 2004 Nov 11 14

Philips Semiconductors

Product specication

Quad bilateral switches

74HC4066; 74HCT4066

MGR263

handbook, full pagewidth

(dB) 20

40

60

80

100 10

102

103

104

105

f (kHz)

106

Test conditions: VCC = 4.5 V; GND = 0 V; RL = 50 ; Rsource = 1 k.

Fig.11 Typical switch OFF signal feed-through as a function of frequency.

MGR264

handbook, full pagewidth

(dB)

5 10

102

103

104

105

f (kHz)

106

Test conditions: VCC = 4.5 V; GND = 0 V; RL = 50 ; Rsource = 1 k.

Fig.12 Typical frequency response.

2004 Nov 11

15

Philips Semiconductors

Product specication

Quad bilateral switches

74HC4066; 74HCT4066

handbook, full pagewidth

VCC 2RL nY/nZ RL 2RL channel ON CL GND

MGR265

0.1 F VI

nZ/nY

Fig.13 Test circuit for measuring crosstalk between any two switches; channels ON condition.

handbook, full pagewidth

VCC 2RL nY/nZ

VCC 2RL nZ/nY Vos

2RL

channel OFF

2RL

CL dB GND

MGR266

Fig.14 Test circuit for measuring crosstalk between any two switches; channels OFF condition.

2004 Nov 11

16

Philips Semiconductors

Product specication

Quad bilateral switches

74HC4066; 74HCT4066

The crosstalk is defined as follows handbook, full pagewidth (oscilloscope output).

VCC 2RL

nE

VCC VCC GND 2RL nZ/nY 2RL CL Vos

fpage

Vct(p-p)

MGR267

nY/nZ 2RL

D.U.T.

oscilloscope GND

MGR268

Fig.15 Test circuit for measuring crosstalk between control and any switch.

handbook, full pagewidth

VCC 2RL nY/nZ 2RL channel ON

MGR269

0.1 F sine-wave Vis

nZ/nY CL dB

Vos

GND

Adjust input voltage to obtain 0 dB at Vos when fi = 1 MHz. After set-up, the frequency of fi is increased to obtain a reading of -3 dB at Vos.

Fig.16 Test circuit for measuring minimum frequency response.

2004 Nov 11

17

Philips Semiconductors

Product specication

Quad bilateral switches

74HC4066; 74HCT4066

handbook, full pagewidth

VCC 2RL nY/nZ nZ/nY DISTORTION METER GND

MGR270

10 F fi = 1 kHz sine-wave Vis

Vos

2RL channel ON

CL

Fig.17 Test circuit for measuring sine wave distortion.

handbook, full pagewidth

VCC 2RL nY/nZ 2RL channel OFF

MGR271

0.1 F Vis

nZ/nY CL dB

Vos

GND

Fig.18 Test circuit for measuring switch OFF signal feed-through.

2004 Nov 11

18

Philips Semiconductors

Product specication

Quad bilateral switches

74HC4066; 74HCT4066

AC WAVEFORMS

handbook, full pagewidth

tr 90% Vis 10% 50%

tf VCC

GND

Vos

50%

tPLH

tPHL

MGR272

Fig.19 Waveforms showing the input (Vis) to output (Vos) propagation delays.

tf 90 % nE input VM 10 % t PLZ output LOW - to - OFF OFF - to - LOW t PHZ output HIGH - to - OFF OFF - to - HIGH outputs enabled 90 %

tr

t PZL

50 % 10 % t PZH 50 % outputs disabled outputs enabled

MGA846

74HC4066: VM = 50 %; VI = GND to VCC. 74HCT4066: VM = 1.3 V; VI = GND to 3 V.

Fig.20 Waveforms showing the turn-on and turn-off times.

2004 Nov 11

19

Philips Semiconductors

Product specication

Quad bilateral switches

74HC4066; 74HCT4066

TEST CIRCUIT AND WAVEFORMS

VCC Vis VI D.U.T. RT CL GND

MGR273

handbook, full pagewidth

VCC VO RL switch open

PULSE GENERATOR

TEST tPZH tPZL tPHZ tPLZ other

SWITCH GND VCC GND VCC open

Vis VCC GND VCC GND pulse

tf = 6 ns; when measuring fmax, there is no constraint to tr and tf with 50 % duty factor.

Definitions for test circuit: RL = Load resistance. CL = Load capacitance including jig and probe capacitance. RT = Termination resistance should be equal to the output impedance ZO of the pulse generator.

Fig.21 Test circuit for measuring AC performance.

handbook, full pagewidth

tW 90% negative input pulse VM 10% tTHL (tf) tTLH (tr) positive input pulse 10% tW 90% VM 0V

MGR274

amplitude

0V tTLH (tr) tTHL (tf) amplitude

tr and tf FAMILY 74HC4066 74HCT4066 AMPLITUDE VCC 3.0 V VM 50 % 1.3 V fmax; PULSE WIDTH <2 ns <2 ns OTHER 6 ns 6 ns

Fig.22 Input pulse definitions.

2004 Nov 11

20

Philips Semiconductors

Product specication

Quad bilateral switches

74HC4066; 74HCT4066

PACKAGE OUTLINES

DIP14: plastic dual in-line package; 14 leads (300 mil) SOT27-1

seating plane

ME

A2

A1

c Z e b1 b 14 8 MH w M (e 1)

pin 1 index E

5 scale

10 mm

DIMENSIONS (inch dimensions are derived from the original mm dimensions) UNIT mm inches Note 1. Plastic or metal protrusions of 0.25 mm (0.01 inch) maximum per side are not included. OUTLINE VERSION SOT27-1 REFERENCES IEC 050G04 JEDEC MO-001 JEITA SC-501-14 EUROPEAN PROJECTION A max. 4.2 0.17 A1 min. 0.51 0.02 A2 max. 3.2 0.13 b 1.73 1.13 0.068 0.044 b1 0.53 0.38 0.021 0.015 c 0.36 0.23 0.014 0.009 D (1) 19.50 18.55 0.77 0.73 E (1) 6.48 6.20 0.26 0.24 e 2.54 0.1 e1 7.62 0.3 L 3.60 3.05 0.14 0.12 ME 8.25 7.80 0.32 0.31 MH 10.0 8.3 0.39 0.33 w 0.254 0.01 Z (1) max. 2.2 0.087

ISSUE DATE 99-12-27 03-02-13

2004 Nov 11

21

Philips Semiconductors

Product specication

Quad bilateral switches

74HC4066; 74HCT4066

SO14: plastic small outline package; 14 leads; body width 3.9 mm

SOT108-1

A X

c y HE v M A

Z 14 8

Q A2 A1 pin 1 index Lp 1 e bp 7 w M L detail X (A 3) A

2.5 scale

5 mm

DIMENSIONS (inch dimensions are derived from the original mm dimensions) UNIT mm A max. 1.75 A1 0.25 0.10 A2 1.45 1.25 A3 0.25 0.01 bp 0.49 0.36 c 0.25 0.19 D (1) 8.75 8.55 E (1) 4.0 3.8 0.16 0.15 e 1.27 0.05 HE 6.2 5.8 L 1.05 Lp 1.0 0.4 Q 0.7 0.6 0.028 0.024 v 0.25 0.01 w 0.25 0.01 y 0.1 Z (1) 0.7 0.3

0.010 0.057 inches 0.069 0.004 0.049

0.019 0.0100 0.35 0.014 0.0075 0.34

0.244 0.039 0.041 0.228 0.016

0.028 0.004 0.012

8 o 0

Note 1. Plastic or metal protrusions of 0.15 mm (0.006 inch) maximum per side are not included. OUTLINE VERSION SOT108-1 REFERENCES IEC 076E06 JEDEC MS-012 JEITA EUROPEAN PROJECTION

ISSUE DATE 99-12-27 03-02-19

2004 Nov 11

22

Philips Semiconductors

Product specication

Quad bilateral switches

74HC4066; 74HCT4066

SSOP14: plastic shrink small outline package; 14 leads; body width 5.3 mm

SOT337-1

A X

c y HE v M A

Z 14 8

Q A2 A1 pin 1 index Lp L 1 bp 7 w M detail X (A 3) A

2.5 scale

5 mm

DIMENSIONS (mm are the original dimensions) UNIT mm A max. 2 A1 0.21 0.05 A2 1.80 1.65 A3 0.25 bp 0.38 0.25 c 0.20 0.09 D (1) 6.4 6.0 E (1) 5.4 5.2 e 0.65 HE 7.9 7.6 L 1.25 Lp 1.03 0.63 Q 0.9 0.7 v 0.2 w 0.13 y 0.1 Z (1) 1.4 0.9 8 o 0

o

Note 1. Plastic or metal protrusions of 0.25 mm maximum per side are not included. OUTLINE VERSION SOT337-1 REFERENCES IEC JEDEC MO-150 JEITA EUROPEAN PROJECTION

ISSUE DATE 99-12-27 03-02-19

2004 Nov 11

23

Philips Semiconductors

Product specication

Quad bilateral switches

74HC4066; 74HCT4066

TSSOP14: plastic thin shrink small outline package; 14 leads; body width 4.4 mm

SOT402-1

c y HE v M A

14

Q A2 pin 1 index A1 Lp L (A 3) A

1

e bp

7

w M detail X

2.5 scale

5 mm

DIMENSIONS (mm are the original dimensions) UNIT mm A max. 1.1 A1 0.15 0.05 A2 0.95 0.80 A3 0.25 bp 0.30 0.19 c 0.2 0.1 D (1) 5.1 4.9 E (2) 4.5 4.3 e 0.65 HE 6.6 6.2 L 1 Lp 0.75 0.50 Q 0.4 0.3 v 0.2 w 0.13 y 0.1 Z (1) 0.72 0.38 8 o 0

o

Notes 1. Plastic or metal protrusions of 0.15 mm maximum per side are not included. 2. Plastic interlead protrusions of 0.25 mm maximum per side are not included. OUTLINE VERSION SOT402-1 REFERENCES IEC JEDEC MO-153 JEITA EUROPEAN PROJECTION ISSUE DATE 99-12-27 03-02-18

2004 Nov 11

24

Philips Semiconductors

Product specication

Quad bilateral switches

74HC4066; 74HCT4066

DHVQFN14: plastic dual in-line compatible thermal enhanced very thin quad flat package; no leads; SOT762-1 14 terminals; body 2.5 x 3 x 0.85 mm

A A1 E c

terminal 1 index area

detail X

terminal 1 index area e 2 L

e1 b 6 v M C A B w M C y1 C

C y

1 Eh 14

7 e 8

13 Dh 0

9 X 2.5 scale 5 mm

DIMENSIONS (mm are the original dimensions) UNIT mm A(1) max. 1 A1 0.05 0.00 b 0.30 0.18 c 0.2 D (1) 3.1 2.9 Dh 1.65 1.35 E (1) 2.6 2.4 Eh 1.15 0.85 e 0.5 e1 2 L 0.5 0.3 v 0.1 w 0.05 y 0.05 y1 0.1

Note 1. Plastic or metal protrusions of 0.075 mm maximum per side are not included. OUTLINE VERSION SOT762-1 REFERENCES IEC --JEDEC MO-241 JEITA --EUROPEAN PROJECTION ISSUE DATE 02-10-17 03-01-27

2004 Nov 11

25

Philips Semiconductors

Product specication

Quad bilateral switches

74HC4066; 74HCT4066

DATA SHEET STATUS LEVEL I DATA SHEET STATUS(1) Objective data PRODUCT STATUS(2)(3) Development DEFINITION This data sheet contains data from the objective specication for product development. Philips Semiconductors reserves the right to change the specication in any manner without notice. This data sheet contains data from the preliminary specication. Supplementary data will be published at a later date. Philips Semiconductors reserves the right to change the specication without notice, in order to improve the design and supply the best possible product. This data sheet contains data from the product specication. Philips Semiconductors reserves the right to make changes at any time in order to improve the design, manufacturing and supply. Relevant changes will be communicated via a Customer Product/Process Change Notication (CPCN).

II

Preliminary data Qualication

III

Product data

Production

Notes 1. Please consult the most recently issued data sheet before initiating or completing a design. 2. The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL http://www.semiconductors.philips.com. 3. For data sheets describing multiple type numbers, the highest-level product status determines the data sheet status. DEFINITIONS Short-form specification The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook. Limiting values definition Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability. Application information Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification. DISCLAIMERS Life support applications These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application. Right to make changes Philips Semiconductors reserves the right to make changes in the products including circuits, standard cells, and/or software described or contained herein in order to improve design and/or performance. When the product is in full production (status Production), relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no licence or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

2004 Nov 11

26

Philips Semiconductors a worldwide company

Contact information For additional information please visit http://www.semiconductors.philips.com. Fax: +31 40 27 24825 For sales ofces addresses send e-mail to: sales.addresses@www.semiconductors.philips.com.

Koninklijke Philips Electronics N.V. 2004

SCA76

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.

Printed in The Netherlands

R44/05/pp27

Date of release: 2004

Nov 11

Document order number:

9397 750 14188

Das könnte Ihnen auch gefallen

- Data Sheet: 74HC14 74HCT14Dokument23 SeitenData Sheet: 74HC14 74HCT14Miguel LamborghiniNoch keine Bewertungen

- 74HC32Dokument20 Seiten74HC32Ingrid XytrasNoch keine Bewertungen

- 47HC00 NandDokument17 Seiten47HC00 NandWilliams Paredes CNoch keine Bewertungen

- Data Sheet: 74HC/HCT4316Dokument15 SeitenData Sheet: 74HC/HCT4316alguien1972Noch keine Bewertungen

- 74HC02 74HCT02: 1. General DescriptionDokument16 Seiten74HC02 74HCT02: 1. General DescriptionCesar VilledaNoch keine Bewertungen

- General Description: Quad Bistable Transparant LatchDokument20 SeitenGeneral Description: Quad Bistable Transparant LatchCesar VilledaNoch keine Bewertungen

- 74 LV 00Dokument10 Seiten74 LV 00Brzata PticaNoch keine Bewertungen

- 74HC00 74HCT00: 1. General DescriptionDokument16 Seiten74HC00 74HCT00: 1. General DescriptionvanlongsportNoch keine Bewertungen

- General Description: Quad Bilateral SwitchDokument23 SeitenGeneral Description: Quad Bilateral Switchtotal4321Noch keine Bewertungen

- 74HC 040Dokument20 Seiten74HC 040linguyen1Noch keine Bewertungen

- 74HC4040 74HCT4040: 1. General DescriptionDokument24 Seiten74HC4040 74HCT4040: 1. General Descriptiontt884211Noch keine Bewertungen

- 74 Ls 244Dokument16 Seiten74 Ls 244Abednego TariganNoch keine Bewertungen

- 74HC244 74HCT244: 1. General DescriptionDokument18 Seiten74HC244 74HCT244: 1. General DescriptionCesar VilledaNoch keine Bewertungen

- 74HC04 74HCT04: 1. General DescriptionDokument18 Seiten74HC04 74HCT04: 1. General DescriptionDistribuidorIBoolPedregalDeSantoDomingoNoch keine Bewertungen

- General Description: Quad Buffer/line Driver 3-StateDokument15 SeitenGeneral Description: Quad Buffer/line Driver 3-Statesinner86Noch keine Bewertungen

- 74LVC14APWDHDokument11 Seiten74LVC14APWDHIlie GrecuNoch keine Bewertungen

- Quad Bilateral Switches: Integrated CircuitsDokument10 SeitenQuad Bilateral Switches: Integrated CircuitsBrzata PticaNoch keine Bewertungen

- 74 HC 245Dokument22 Seiten74 HC 245Vương QuýNoch keine Bewertungen

- 74HC107 74HCT107: 1. General DescriptionDokument20 Seiten74HC107 74HCT107: 1. General DescriptionDistribuidorIBoolPedregalDeSantoDomingoNoch keine Bewertungen

- 74ahc Ahct1g14Dokument15 Seiten74ahc Ahct1g14Ignacio ScalisiNoch keine Bewertungen

- 74HC14 74HCT14: 1. General DescriptionDokument21 Seiten74HC14 74HCT14: 1. General DescriptionDao Nguyen Trong TinNoch keine Bewertungen

- Integrated Circuits Data Sheet: 74HC4050 Hex High-to-Low Level ShifterDokument7 SeitenIntegrated Circuits Data Sheet: 74HC4050 Hex High-to-Low Level ShifterBrzata PticaNoch keine Bewertungen

- 74HC4050 CNV PDFDokument7 Seiten74HC4050 CNV PDFtare890Noch keine Bewertungen

- 74 HC 4067Dokument15 Seiten74 HC 4067김경원Noch keine Bewertungen

- 74HC HCT574Dokument19 Seiten74HC HCT574huypiggyNoch keine Bewertungen

- General Description: Dual 4-Input AND GateDokument15 SeitenGeneral Description: Dual 4-Input AND GateRizki FebriyantoNoch keine Bewertungen

- 74LVC00A: 1. General DescriptionDokument14 Seiten74LVC00A: 1. General DescriptionVlad Cristia-AvramNoch keine Bewertungen

- 74LVC1G386: 1. General DescriptionDokument12 Seiten74LVC1G386: 1. General DescriptionÊder ContrerasNoch keine Bewertungen

- Data Sheet: 74AHC74 74AHCT74Dokument20 SeitenData Sheet: 74AHC74 74AHCT74Kang JadiJaya OtodidakNoch keine Bewertungen

- 74LVC08A: 1. General DescriptionDokument15 Seiten74LVC08A: 1. General DescriptionWalterNoch keine Bewertungen

- 74HC573Dokument21 Seiten74HC573ric_napigkitNoch keine Bewertungen

- 74HC02 74HCT02: 1. General DescriptionDokument15 Seiten74HC02 74HCT02: 1. General DescriptionAnonymous xTGQYFrNoch keine Bewertungen

- 74AHC1G02 74AHCT1G02: 1. General DescriptionDokument11 Seiten74AHC1G02 74AHCT1G02: 1. General DescriptionMarcu Andrei StefanNoch keine Bewertungen

- 74HC03 74HCT03: 1. General DescriptionDokument16 Seiten74HC03 74HCT03: 1. General DescriptionDistribuidorIBoolPedregalDeSantoDomingoNoch keine Bewertungen

- 74AUP1G07: 1. General DescriptionDokument19 Seiten74AUP1G07: 1. General DescriptionSyed Noman AhmedNoch keine Bewertungen

- 74AHC125 74AHCT125: 1. General DescriptionDokument15 Seiten74AHC125 74AHCT125: 1. General Descriptionkitt354Noch keine Bewertungen

- 74AHC1G86 74AHCT1G86: 1. General DescriptionDokument12 Seiten74AHC1G86 74AHCT1G86: 1. General DescriptionKushalSwamyNoch keine Bewertungen

- 74LVC1G11: 1. General DescriptionDokument14 Seiten74LVC1G11: 1. General DescriptionnevdullNoch keine Bewertungen

- 74AHC1G32 74AHCT1G32: 1. General DescriptionDokument12 Seiten74AHC1G32 74AHCT1G32: 1. General DescriptionnevdullNoch keine Bewertungen

- Datasheet 74153Dokument17 SeitenDatasheet 74153Ingga Permana0% (1)

- 74HC08 74HCT08: 1. General DescriptionDokument16 Seiten74HC08 74HCT08: 1. General DescriptionCesar VilledaNoch keine Bewertungen

- Octal Bus Transceiver With 3-State Outputs: FeaturesDokument24 SeitenOctal Bus Transceiver With 3-State Outputs: FeaturesLungoci AdrianNoch keine Bewertungen

- Mc74hc4051a DDokument17 SeitenMc74hc4051a DroozbehxoxNoch keine Bewertungen

- 74 Alvc 164245Dokument13 Seiten74 Alvc 164245roozbehxoxNoch keine Bewertungen

- 74HC08 74HCT08: 1. General DescriptionDokument15 Seiten74HC08 74HCT08: 1. General DescriptionFlavio KwiecinskiNoch keine Bewertungen

- 74HC10-Q100 74HCT10-Q100: 1. General DescriptionDokument13 Seiten74HC10-Q100 74HCT10-Q100: 1. General DescriptionNelson RodriguezNoch keine Bewertungen

- 74HC245 74HCT245: 1. General DescriptionDokument18 Seiten74HC245 74HCT245: 1. General Descriptionnadeem hameedNoch keine Bewertungen

- 74HC4040 74HCT4040: 1. General DescriptionDokument20 Seiten74HC4040 74HCT4040: 1. General DescriptionWilliamNoch keine Bewertungen

- 74HC32-Q100 74HCT32-Q100: 1. General DescriptionDokument16 Seiten74HC32-Q100 74HCT32-Q100: 1. General Descriptiongotcha75Noch keine Bewertungen

- 74HC4051 74HCT4051: 1. General DescriptionDokument31 Seiten74HC4051 74HCT4051: 1. General DescriptiondonghungstbNoch keine Bewertungen

- LW 066 ADokument23 SeitenLW 066 ABin WangNoch keine Bewertungen

- 74HC74 74HCT74: 1. General DescriptionDokument21 Seiten74HC74 74HCT74: 1. General DescriptionGermán BergerNoch keine Bewertungen

- MC 14052 DatasheetDokument12 SeitenMC 14052 DatasheetgrooyoNoch keine Bewertungen

- 74HC273 74HCT273: 1. General DescriptionDokument20 Seiten74HC273 74HCT273: 1. General DescriptionAsif ShahNoch keine Bewertungen

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Noch keine Bewertungen

- Beginning Digital Electronics through ProjectsVon EverandBeginning Digital Electronics through ProjectsBewertung: 5 von 5 Sternen5/5 (1)

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsVon EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNoch keine Bewertungen

- Metal Glaze ResistorDokument3 SeitenMetal Glaze Resistorprpabst8514Noch keine Bewertungen

- B41821 Single-Ended CapacitorsDokument19 SeitenB41821 Single-Ended Capacitorsprpabst8514Noch keine Bewertungen

- V100 Eu PDFDokument16 SeitenV100 Eu PDFprpabst8514Noch keine Bewertungen

- Software PID Control of An Inverted Pendulum Using The PIC16F684Dokument14 SeitenSoftware PID Control of An Inverted Pendulum Using The PIC16F684Antony Charles TejadaNoch keine Bewertungen

- 1009PCDFCA DownstreamDokument3 Seiten1009PCDFCA Downstreamprpabst8514Noch keine Bewertungen

- Relez Auto PID AdjustmentDokument3 SeitenRelez Auto PID AdjustmentSemir MustaficNoch keine Bewertungen

- Solution Optimization For Smps ApplicationDokument106 SeitenSolution Optimization For Smps ApplicationHemantkumar100% (1)

- Alldatasheet - World's Biggest Datasheet Search EngineDokument12 SeitenAlldatasheet - World's Biggest Datasheet Search EngineDede TajirNoch keine Bewertungen

- Ceilcote 6640 Ceilcrete+ds+engDokument4 SeitenCeilcote 6640 Ceilcrete+ds+englivefreakNoch keine Bewertungen

- TDS 46682 Essence Easy Wipe (New) Euk ID PDFDokument4 SeitenTDS 46682 Essence Easy Wipe (New) Euk ID PDFGunawan AryantoNoch keine Bewertungen

- Fronius Ig PV Inverter: Technical Data SheetDokument2 SeitenFronius Ig PV Inverter: Technical Data Sheetfarani87Noch keine Bewertungen

- Safety Data Sheet: Section 1 - Product and Company IdentificationDokument8 SeitenSafety Data Sheet: Section 1 - Product and Company IdentificationWici WiciNoch keine Bewertungen

- Europump - 6-Guidelines On The Application of The Regulation EC-640-2009 - 2011-05Dokument17 SeitenEuropump - 6-Guidelines On The Application of The Regulation EC-640-2009 - 2011-05XavierNoch keine Bewertungen

- PBW SDS enDokument8 SeitenPBW SDS enMika TacquetNoch keine Bewertungen

- Mt190aw01 V5Dokument24 SeitenMt190aw01 V5Orangelin SantaellaNoch keine Bewertungen

- 351701digsf0053 Exco00 30Dokument30 Seiten351701digsf0053 Exco00 30Theophilus Oduro-NyarkoNoch keine Bewertungen

- LB1967Dokument5 SeitenLB1967Marcelituz RojasNoch keine Bewertungen

- SigmaCover 410 Protective Coating GuideDokument4 SeitenSigmaCover 410 Protective Coating GuideMohammed AdilNoch keine Bewertungen

- Surfa'SafeDokument6 SeitenSurfa'SafeIndraPieceNoch keine Bewertungen

- Aquathol K Aquatic Herbicide MsdsDokument7 SeitenAquathol K Aquatic Herbicide MsdsSouth Santee AquacultureNoch keine Bewertungen

- Ciclo Di Verniciatura: Painting CycleDokument7 SeitenCiclo Di Verniciatura: Painting CycleMaffone NumerounoNoch keine Bewertungen

- 1N4001GP 1N4007GPDokument3 Seiten1N4001GP 1N4007GPAlexandre S. CorrêaNoch keine Bewertungen

- Linearlight Power Flex Lm10pDokument4 SeitenLinearlight Power Flex Lm10pFandy Aditya WiranaNoch keine Bewertungen

- Engineering Design Guidelines Process Flow SheetDokument29 SeitenEngineering Design Guidelines Process Flow SheetPedro ViegasNoch keine Bewertungen

- Crude Oil Storage Tank MDRDokument5 SeitenCrude Oil Storage Tank MDRAtty Atty50% (2)

- Specification: Inno Display CorporationDokument23 SeitenSpecification: Inno Display Corporationserssh 11Noch keine Bewertungen

- Data ViewerDokument3 SeitenData ViewerAnonymous FZNn6rBNoch keine Bewertungen

- TDS PDF Intercept - 7000Dokument4 SeitenTDS PDF Intercept - 7000PastiDjadi PastiDjadiNoch keine Bewertungen

- The Role of Safety OfficerDokument10 SeitenThe Role of Safety OfficerSiddharth100% (1)

- Interline 994+ds+eng PDFDokument4 SeitenInterline 994+ds+eng PDFMohamed NouzerNoch keine Bewertungen

- Sunpakfsp TdsDokument8 SeitenSunpakfsp TdsTanjaNoch keine Bewertungen

- Touchwood NC Thinner: Architectural CoatingsDokument2 SeitenTouchwood NC Thinner: Architectural CoatingsmuthukumarNoch keine Bewertungen

- Norsok M 630 BasicsDokument1 SeiteNorsok M 630 BasicsLakshit SethNoch keine Bewertungen

- Ottocoll® M 500: The Water-Resistant Premium Hybrid Adhesive/sealantDokument4 SeitenOttocoll® M 500: The Water-Resistant Premium Hybrid Adhesive/sealantJoeNoch keine Bewertungen

- GMW3001Dokument1 SeiteGMW3001skgolban0% (1)

- Chartek 1709: Epoxy IntumescentDokument4 SeitenChartek 1709: Epoxy IntumescentShijil ValsanNoch keine Bewertungen

- Carta FuturaDokument3 SeitenCarta FuturaCarlosSánchezNoch keine Bewertungen