Beruflich Dokumente

Kultur Dokumente

Pipeline Control

Hochgeladen von

greenvalley746766Originalbeschreibung:

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Pipeline Control

Hochgeladen von

greenvalley746766Copyright:

Verfügbare Formate

PIPELINE CONTROL

Because of the nonlinear usage of the stages of an arithmetic pipeline, it becomes more difficult to determine when to initiate each successive task in order to obtain maximum performance without conflict. We wish to initiate new tasks at as high a rate as possible; but we must also ensure that a single stage will never be needed by two tasks at the same time. In some pipelines, more than one type of task may be scheduled at the same time. In this discussion we will assume that all tasks are identical. The problem of pipeline scheduling can be addressed by means of a scheduling diagram known as a reservation table. This technique will be briefly described in the following sections. Reservation Tables A reservation table is a two-dimensional table in which each row represents a pipeline stage (processing element) and each column represents a cycle in the execution of a task. Within each column, an X is placed in the entries corresponding to the stages required by that task during that cycle. Figure 1 shows a typical reservation table for a three-stage pipeline and a six-cycle task. This table shows that the task uses stage A for two cycles. During the second cycle, Stage B is also used; this stage is still used in cycle three. Cycle four uses stage C. During the fifth cycle, the task returns again to Stage A. Finally, Stage B is used in the last cycle.

Figure 1 -- A Reservation Table Forbidden Latencies Our goal is to determine how many cycles we must wait, after one task is initiated, until another task can be initiated without conflict. The number of cycles between initiations is called the latency. We want to design a schedule which has

the minimum average latency (MAL) for our pipeline. However, such a schedule may not have the same latency between each successive task. The first step is to identify the forbidden latencies revealed by the diagram. A latency is forbidden if it will lead to a collision, that is, a simultaneous need for the same stage by two different tasks. The table shows that stage A is required during both the first and second cycles. We cannot initiate a new task after only one cycle, or there would be an immediate collision. Suppose instead that we try to begin the second task three cycles after the first. There will be no collision during its initial cycle. During the second cycle for the new task, however, the original task will have reached cycle five, and both will require stage A. Fortunately, there is a systematic way to identify all forbidden latencies from a given reservation table. For each row containing more than one X, we write down the distance between every pair of X's. Each such distance represents a forbidden latency. In our example, row A contains three X's which can form three distinct pairs. The latencies blocked by these pairs are 1, 3, and 4. Row B yields an identical set of forbidden latencies. There are no forbidden latencies for row C, since it contains only one X. The set of forbidden latencies is then summarized in a bit string called a collision vector. The collision vector contains a bit for each possible latency from one up to the total length of the task. The bits are numbered from left to right (but some authors use the opposite order). The collision vector for our example table is 101100. State Transitions A collision vector may be thought of as a representation of the current state of the pipeline. Our example pipeline will be in state 101100 at the moment that the first task is initiated. This pattern tells us that we may not initiate another task after 1, 3, or 4 cycles, but we may initiate a new task after 2, 5, or 6 cycles. Of course, we may also initiate after any number of cycles greater than 6, since the original task will then be completed.

Suppose that we begin a second task after two cycles. Can we then wait another two cycles and begin a third task? Unfortunately, the answer is no. To see this, consider the time at which the second task has just been initiated. The first task still has four cycles to complete. We can represent this situation by a new reservation table, in

which the stages reserved by the first task are marked by 1's, and those reserved by the second task are marked by 2's.

Figure 2 -- Reservation Table for Two Tasks

The conflicts in this table are represented by the union of two collision vectors. The collision vector for the first task is the original vector with the first two positions shifted out to the left. Its form is 110000. The vector for the second task, just begun, has the original form. The collision vector formed by the union of these two is 111100. This is the state represented by the table in Figure 2. State Diagrams Using a similar analysis, the set of possible states for a given pipeline may be identified. The original collision vector shows allowable transitions for latencies of 2, 5, or 6. In general each of these will lead to a new state. However, in this example, the resulting states for latencies of 5 or 6 are identical to the original state. Latency 2, as we have seen, leads to a distinct state. Further transitions from this state can occur only at latencies of 5 or 6 (or greater). Each of these transitions produce additional states; in this case these are again identical to the original state.

By a systematic analysis of each possible transition, all possible states can be identified together with the full set of allowable latencies. Fortunately, the set of distinct states is usually small. A state diagram can be used to represent these states; the state diagram corresponding to our example is shown in Figure 3.

Figure 3 -- A State Diagram

Finding the MAL A sequence of allowable task initiations corresponds to a sequence of allowable transitions in the state diagram. By inspection we can find all cycles in the diagram; each cycle identifies a repeatable sequence of initiations. The cycle with the lowest value for all of the transitions it contains represents the initiation sequence with the minimum average latency. In our example, The desired cycle contains alternating latencies of 2 and 5, giving an average latency of 3.5. We will obtain maximum throughput for this task in this pipeline by waiting alternately two cycles followed by five cycles for successive initiations. In many cases, the cycle having the minimum average latency is a greedy cycle, that is, one that makes the earliest possible transition to each new state. However, there are cases in which a non-greedy strategy must be used to obtain the MAL. Implementation In the design of a pipeline which is dedicated to a single type of task with a fixed reservation pattern, the above analysis may be performed during the design stage. Simple sequencing logic is then developed to ensure that the correct schedule is followed.

Alternately, logic can be included in some pipelines to keep track of the current collision vector for the system and make scheduling decisions dynamically. This is most appropriate for pipelines that may accept more than one kind of task.

Das könnte Ihnen auch gefallen

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- IES OBJ Civil Engineering 2000 Paper IDokument17 SeitenIES OBJ Civil Engineering 2000 Paper Itom stuartNoch keine Bewertungen

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- ALTS150-12P Datasheet1Dokument2 SeitenALTS150-12P Datasheet1mamloveNoch keine Bewertungen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Toftejorg TZ-75 Rotary Jet Head - Portable: Fast, Effective Impact CleaningDokument3 SeitenToftejorg TZ-75 Rotary Jet Head - Portable: Fast, Effective Impact CleaningSamo SpontanostNoch keine Bewertungen

- 2011 Frequency AllocationsDokument1 Seite2011 Frequency Allocationsculeros1Noch keine Bewertungen

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- 2011 Burris CatalogDokument56 Seiten2011 Burris CatalogMario Lopez100% (1)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- World Trends in Municipal Solid Waste ManagementDokument11 SeitenWorld Trends in Municipal Solid Waste ManagementNeima EndrisNoch keine Bewertungen

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- HP Scanjet Pro 2500 F1 Flatbed Scanner: Boost Productivity With Fast, Versatile ScanningDokument2 SeitenHP Scanjet Pro 2500 F1 Flatbed Scanner: Boost Productivity With Fast, Versatile ScanningParesh BabariaNoch keine Bewertungen

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- CNC Milling ReportDokument15 SeitenCNC Milling ReportStarscream Aisyah78% (37)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- DAY 3 STRESS Ielts NguyenhuyenDokument1 SeiteDAY 3 STRESS Ielts NguyenhuyenTĩnh HạNoch keine Bewertungen

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- Piaggio MP3 300 Ibrido LT MY 2010 (En)Dokument412 SeitenPiaggio MP3 300 Ibrido LT MY 2010 (En)Manualles100% (3)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Afa Coursework ExamplesDokument6 SeitenAfa Coursework Examplesiuhvgsvcf100% (2)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- 22 Thành NG Quen Thu C Trên Ielts - FirefighterDokument2 Seiten22 Thành NG Quen Thu C Trên Ielts - FirefighterNinh NguyễnNoch keine Bewertungen

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- Optimizing Stata For Analysis of Large Data SetsDokument29 SeitenOptimizing Stata For Analysis of Large Data SetsTrần Anh TùngNoch keine Bewertungen

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- Slide 7 PV NewDokument74 SeitenSlide 7 PV NewPriyanshu AgrawalNoch keine Bewertungen

- Dpb6013 HRM - Chapter 3 HRM Planning w1Dokument24 SeitenDpb6013 HRM - Chapter 3 HRM Planning w1Renese LeeNoch keine Bewertungen

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- Visual Metaphor Process BookDokument18 SeitenVisual Metaphor Process Bookmatt8859Noch keine Bewertungen

- Number CardsDokument21 SeitenNumber CardsCachipún Lab CreativoNoch keine Bewertungen

- تأثير العناصر الثقافية والبراغماتية الأسلوبية في ترجمة سورة الناس من القرآن الكريم إلى اللغة الإ PDFDokument36 Seitenتأثير العناصر الثقافية والبراغماتية الأسلوبية في ترجمة سورة الناس من القرآن الكريم إلى اللغة الإ PDFSofiane DouifiNoch keine Bewertungen

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (345)

- Green ThumbDokument2 SeitenGreen ThumbScarlet Sofia Colmenares VargasNoch keine Bewertungen

- Corrosion Protection PT Tosanda Dwi SapurwaDokument18 SeitenCorrosion Protection PT Tosanda Dwi SapurwaYoga FirmansyahNoch keine Bewertungen

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- Chomsky's Universal GrammarDokument4 SeitenChomsky's Universal GrammarFina Felisa L. AlcudiaNoch keine Bewertungen

- 1st Unseen Passage For Class 5 in EnglishDokument7 Seiten1st Unseen Passage For Class 5 in EnglishVibhav SinghNoch keine Bewertungen

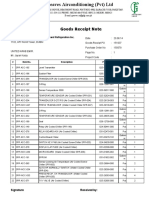

- Goods Receipt Note: Johnson Controls Air Conditioning and Refrigeration Inc. (YORK) DateDokument4 SeitenGoods Receipt Note: Johnson Controls Air Conditioning and Refrigeration Inc. (YORK) DateSaad PathanNoch keine Bewertungen

- 19 71 Hydrologic Engineering Methods For Water Resources DevelopmentDokument654 Seiten19 71 Hydrologic Engineering Methods For Water Resources DevelopmentMartha LetchingerNoch keine Bewertungen

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- Lab 3 Report Fins RedoDokument3 SeitenLab 3 Report Fins RedoWestley GomezNoch keine Bewertungen

- Engineering Geology: Wei-Min Ye, Yong-Gui Chen, Bao Chen, Qiong Wang, Ju WangDokument9 SeitenEngineering Geology: Wei-Min Ye, Yong-Gui Chen, Bao Chen, Qiong Wang, Ju WangmazharNoch keine Bewertungen

- All Worksheets MYSQLDokument33 SeitenAll Worksheets MYSQLSample1Noch keine Bewertungen

- 4 PDFDokument81 Seiten4 PDFMohammad K. NassouraNoch keine Bewertungen

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- A New Procedure For Generalized Star Modeling Using Iacm ApproachDokument15 SeitenA New Procedure For Generalized Star Modeling Using Iacm ApproachEdom LazarNoch keine Bewertungen

- Updated WorksheetDokument5 SeitenUpdated WorksheetJohn Ramer Lazarte InocencioNoch keine Bewertungen

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)