Beruflich Dokumente

Kultur Dokumente

4bit Adder

Hochgeladen von

rajat7169451734Originalbeschreibung:

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

4bit Adder

Hochgeladen von

rajat7169451734Copyright:

Verfügbare Formate

Switching & Logic Laboratory

Spring 2008

jeg

Lab 3 Four-Bit Adder

Within VHDL we can describe the logic in three different manners. These three different architectures are: Behavioral describes how the output is derived from the inputs using structured statements. Dataflow describes how the data flows from the inputs to the output most often using NOT, AND and OR operations. Structural describes how gates are interconnected similar to schematic approach.

You are required to implement the VHDL in this laboratory exercise as a structural architecture. In previous laboratory exercises behavioral and dataflow VHDL has been implemented. To implement a design in a structural architecture requires two levels of VHDL. At the lower level, we define the components that make up the higher-level device. As an example in this laboratory exercise, we are going to implement a 4-bit adder using four cascaded full-adders. Therefore, at the lower level we will define the full-adder. At the upper level, we will cascade these components in to the 4-bit adder device. The full-adder will look like a normal VHDL file with an ENTITY statement and an ARCHITECTURE statement. The full adder could be itself a behavioral description, a dataflow description, or a structural description. We will use a dataflow description of the full-adder. These equation in Boolean algebra notation can be found on page 38 in the textbook on the bottom third of the page. We will use: S <= ( A AND NOT B AND NOT Cin) OR (A AND B AND Cin) OR (NOT A AND B AND NOT Cin) OR (NOT A AND NOT B AND Cin); Cout <= (A AND Cin) OR (B AND Cin) OR (A AND B); Note Cout is the reduced form shown near the bottom of page 38. In the higher level VHDL file we must define the full-adder component. The COMPONENT statement has the same PORT statement embedded in it as the lower level VHDL files ENTITY statement. We will use COMPONENT FullAdder --Defined in FullAdder.vhd PORT ( Cin,A,B : IN BIT; Cout,S : OUT BIT); END COMPONENT; Also, in the higher level VHDL file is the instantiation of the Full-Adder components. The instantiation statement contains a label for the component. We will use U01, U02,

Switching & Logic Laboratory

Spring 2008

jeg

U03, and U04 much like components on a printed circuit board. The label is followed by the name of the component and PORT map. The name of the component in this case is FullAdder. The PORT MAP is a mapping of the higher-level VHDL signals to those of the lower-level VHDL file signals. We will use: U01: FullAdder PORT MAP (C,X(0),Y(0),Carry(0),R(0)); U02: FullAdder PORT MAP (Carry(0),X(1),Y(1),Carry(1),R(1)); U03: FullAdder PORT MAP (Carry(1),X(2),Y(2),Carry(2),R(2)); U04: FullAdder PORT MAP (Carry(2),X(3),Y(3),R(4),R(3)); See online help for a definition of the signals within the PORT MAP.

Adder4 as VHDL Structural

To complete a structural type implementation of logic in VHDL using Quartus II perform the following steps: 1. Create a project called Adder4 with the top-level file specified as Adder4. Place the project under your LAB_day directory in the appropriate subdirectory or folder. 2. Set unused pins as tri-state inputs. 3. Create a New file of VHDL type. 4. Enter the following VHDL description in the newly created VHDL file:

Listing 1 Full-Adder Dataflow VHDL

5. Save the VHDL description as FullAdder.vhd. 6. Create a second new file of VHDL type. Enter the following VHDL description in the newly created VHDL file:

Switching & Logic Laboratory

Spring 2008

jeg

Listing 2 Adder4 Structural VHDL

7. Save the VHDL description as Adder4.vhd and perform Analysis & Synthesis until there are 0 errors and 0 warnings by correcting typographical errors. 8. Assign the pins locations using the Assignment Editor. See Table 1 given below for the signal and pin number associations.

Table 1 Hex7Seg I/O Pin Assignments

Pin 4 37 40 39 41 34 33 36 35

Type Input Input Input Input Input Input Input Input Input

Name C X[3] X[2] X[1] X[0] Y[3] Y[2] Y[1] Y[0]

PLDT-2 S5-C1 S1-5 S1-6 S1-7 S1-8 S1-1 S1-2 S1-3 S1-4

Pin 48 49 50 51 52

Type Output Output Output Output Output

Name R[4] R[3] R[2] R[1] R[0]

PLDT-2 LED-4 LED-5 LED-6 LED-7 LED-8

9. Perform a full compile. There should be 0 errors and 0 warnings. Correct the problem if any errors or warnings are displayed. 10. Create a Vector Waveform File and save as Adder4.vwf . The Vector Waveform File should include all 512 combinations of the nine inputs in 100 ns steps. Set the ending time for 512 x 100 ns = 51200 ns or 51.2 us. Add X, Y and R as grouped signals. Add C a single signal. Do not include the individual signals for

Switching & Logic Laboratory

Spring 2008 , to enter the

jeg

X and Y. Expand X and Y and then use the Count Value Icon, data in Table 2 for each input signal.

Table 2 Input Count Vales for Simulation

Inputs Count every: Multiply by: X[0] 100 ns 1 X[1] 100 ns 2 X[2] 100 ns 4 X[3] 100 ns 8 Y[0] 100 ns 16 Y[1] 100 ns 32 Y[2] 100 ns 64 Y[3] 100 ns 128 C 100 ns 256 11. Perform a functional simulation with an ending time of 51200 ns or 51.2 us. Check the simulation for correctness. . If you format X, Y, and R as unsigned decimals, you can use your knowledge of decimal addition to check the results of the simulation. 12. Check the PLDT-2 board to see that all eight jumpers are present on HD1 and a jumper wire goes from J12-1 to HD4-4. If either are missing contact, the laboratory assistant or instructor. 13. Program the EPM7128SLC84-15 on the PLDT-2 board and exercise the DIP switch SK-1 while observing the red LEDs. Record the results of the following additions. Perform the additions by hand to verify the correctness of Table 3. If the hand calculations pre-laboratory and the PLDT-2 results are different, resolve the discrepancies.

Table 3 PLDT-2 Adder4 Test Vectors Results

C 0 X[i] 1 0 1 0 Y[i] + 0 0 0 0 R[i] i 4 3 2 1 0 C 1 X[i] 1 0 1 0 Y[i] + 0 0 0 0 R[i] i 4 3 2 1 0

0 0 1 1 1 + 0 0 1 0 4 3 2 1 0 1 0 1 1 1 + 1 0 0 0 4 3 2 1 0

0 1 0 1 1 + 0 1 1 1 4 3 2 1 0 1 1 0 1 1 + 0 1 1 0 4 3 2 1 0

14. For your report, you will need the FullAdder.vhd and Adder4.vhd. In addition, you will need images of the pin assignments and simulation results. Zoom to a level in which the value of each input may be read. Make sure you have a case with Cin = 0 and a case with Cin =1. Obtain these images by opening the

Switching & Logic Laboratory

Spring 2008

jeg

necessary window and then press Alt-Print Scrn. Then paste the clipboard into Paint or a similar program. Cut or copy only that part of the images that contains useful information. Paste this into either a new Paint window or a Word document. Make sure you take this information with you when you leave the laboratory. Hardcopies printed in the laboratory and then stapled to the report will not be allowed in your report.

Signal Labels

Some times a device will have a group of pins or bus with a common name, such as D in Figure 1. Each signal in the group or bus is differentiated by a number. In this example, Figure 1, the individual signals are D[6], D[5], D[4], D[3], D[2], and D[1]. The group or bus is labeled D[6..1]. When interconnecting bus signals, use the wide line or wire on the drawing toolbar. This is also know as the Orthogonal Bus Tool, , and is right next to the Orthogonal Node Tool, , which you have been using up to this point in time. Note Quartus II uses square braces around bus names to remain compatible with AHDL, while VHDL uses parenthesis around bit_vector names.

Figure 1 Bus Name Exceptions for Primitive Arrays

When the schematic diagram gets to be too complex, one often wants to avoid crossing signal lines. Figure 2 shows an example where signals are connected by name alone. In this case, individual signals are connected to a bus. The signals Ticket[0], Ticket[1], Ticket[2], and Ticket[3 ] are connected to the bus Ticket[3..0]. Note the individual signals in the schematic have the corresponding number appended to it outside of parenthesis or square braces. You will find both of these techniques useful when performing the next project in this laboratory exercise. I did not define the differences between VHDL and Quartus II schematic signal naming. Do not punish the messenger.

Switching & Logic Laboratory

Spring 2008

jeg

Figure 2 Connection by Name Only

Adder4 as Library of Parameterized Model

Quartus II has a large library of parameterized modules, which is abbreviated as LPM. This project will use the Adder/Subtracter LPM known as ADD_SUB.LPM. The models are parameterized which allows you to change the size and features of the LPM device. As an example we will specify the ADD_SUB.LPM to be a 4-bit adder only (no subtractor) with a carry-in and a carry-out. 1. Create a project called Adder4 with the top-level file specified as Adder4. Place the project under your mySL0n directory in a different subdirectory or folder than used in the previous project.. 2. Set unused pins as tri-state inputs. 3. Create a New file of Block Diagram/Schematic Diagram type 4. Create the following schematic with input and output pin names:

Figure 3 Adder4 Schematic Diagram

Switching & Logic Laboratory

Spring 2008

jeg

To create the lpm_add_sub0 block perform the following steps. a. Click on the symbol tool, , and then under C:/altera/72/quartus/libraries/, select megafunctions, then arithmetic, and finally lpm_add_sub. See Figure 4 for an example.

Figure 4 Pre-Parameterized ADD_SUB LPM

b. Now select the OK, dont select the MegaWizard Plug-In Manager. This will be used to configure the 4-bit adder. Select Edit an existing custom megafunction variation.

Switching & Logic Laboratory

Spring 2008

jeg

Figure 5 Page 2c of MegaWizard Plug-In Manager for LPM_ADD_SUB

c. On page 2c select What type of output file do you want to create? as VHLD. Then select Next>. See Figure 5. d. On page 1, select How wide should the data and datab input buses be? as 4 bits. And Which operating mode do you want for the adder/subtractor? as Addition only. Then select Next >. See Figure 6.

Figure 6 Page 1 of the MegaWizard Plug-In Manager LPM_ADD_SUB

e. On page 2 select Is the data or datab input bus value a constant? as No, both values vary. Then select Next >. See Figure 7.

Switching & Logic Laboratory

Spring 2008

jeg

Figure 7 Page 2 of the MegaWazard Plug-In Manager LPM_ADD_SUB

f. On page 3 select Do you want an optional inputs or output? as Input: Create a carry input and Output: Create a carry output. Then select Next>. See Figure 8.

Figure 8 Page 3 of the MegaWazard Plug-In Manager LPM_ADD_SUB

g. On page 4 select Do you want to pipeline function? as No. Then select Next>. See Figure 9.

Switching & Logic Laboratory

Spring 2008

jeg

Figure 9 Page 4 of the MegaWazard Plug-In Manager LPM_ADD_SUB

Figure 10 Page 5 of MegaWizard Plug-In Manager LPM_ADD_SUB Click Next,

h. Figure 10. On page 6 deselect the lpm_add_sub0_waveforms HTML and JPG. Finally select Finish. See Figure 11.

10

Switching & Logic Laboratory

Spring 2008

jeg

\

Figure 11 Page 6 of the MegaWazard Plug-In Manager LPM_ADD_SUB

5. Save the schematic diagram description as Adder4.bdf and perform Analysis & Synthesis until there are 0 errors and 0 warnings by correcting typographical or graphic errors. 6. Assign the pins locations using the Assignment Editor. See Table 1 given above for the signal and pin number associations. 7. Perform a full compile. There should be 0 errors and 0 warnings. Correct the problem if any errors or warnings are displayed. 8. Create a Vector Waveform File and save as Adder4.vwf . The Vector Waveform File should include all 512 combinations of the nine inputs in 100 ns steps. See step 10 of the previous project for details. 9. Perform a functional simulation with an ending time of 52100 ns or 52.1 us. Check the simulation for correctness. . If you format X, Y, and R as unsigned decimals you can use your knowledge of decimal addition to check the results of the simulation. 10. Program the EPM7128SLC84-15 on the PLDT-2 board and exercise the DIP switch SK-1 while observing the red LEDs. Record the results of the following additions. Perform the additions by hand to verify the correctness of Table 3. If the hand calculations and the PLDT-2 results differ, resolve the discrepancy.

Table 4 PLDT-2 Adder4 Test Vectors Results

C 0 X[i] 1 0 1 0 Y[i] + 0 0 0 0 R[i] i 4 3 2 1 0

0 0 1 1 1 + 0 0 1 0 4 3 2 1 0

0 1 0 1 1 + 0 1 1 1 4 3 2 1 0

11

Switching & Logic Laboratory

Spring 2008

jeg

C 1 X[i] 1 0 1 0 Y[i] + 0 0 0 0 R[i] i 4 3 2 1 0

1 0 1 1 1 + 1 0 0 0 4 3 2 1 0

1 1 0 1 1 + 0 1 1 0 4 3 2 1 0

11. For your report, you will need the Adder4 schematic. Either open the appropriate window and then select all, and then paste this image into Paint or similar program and save; or paste the clipboard into a Word document. In addition, you will need images of the pin assignments and simulation results. Zoom to a level in which the value of each input may be read. Make sure you have a case with Cin = 0 and a case with Cin = 1. Obtain these images by opening the necessary window and then press Alt-Print Scrn. Paste the clipboard into Paint or a similar program. Cut or copy only that part of the images that contains useful information. Then paste either this new image into a new Paint window and save or a Word document and save. Make sure you take this information with you when you leave the laboratory. Hardcopies printed in the laboratory and then stapled to the report will not be allowed in your report.

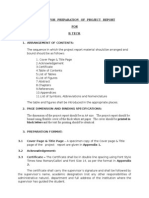

Report Format

This laboratory exercise requires a formal report. See report format handout for detail on the content of a formal reports.

Done?

Things that you might consider doing on your own are: 1. Replace the dataflow architecture with a behavioral architecture and perform a complete implementation with simulation and verification on the PLDT-2. 2. Repeat the second project but use a Adder/Subtractor instead of an Adder LPM. It is suggested that you use S5-C2 for the Add/Sub control. Perform a complete implementation with simulation and verification on the PLDT-2.

12

Switching & Logic Laboratory

Spring 2008

jeg

Lab 3 Adder4

Group Member # 1________________________________________ Please Print

Group Member #2 ________________________________________ Please Print

Group Member #3________________________________________ Please Print

Lab Period: _________________ Monday ... Thursday Lab Station: _______________ 1 through 12 Check List: Description Score

Purpose Discussion to include at a minimum the following: FullAdder.vhd and Adder4.vhd Adder4 Pin assignments Simulation Outputs Adder4 Schematic Simulation Outputs Requested results, if any Conclusion Raw data, if any Laboratory procedure handout

Total

The work presented is the sole work of the stated group members. Representing the work of others as your own is plagiarism and is punishable by failure of the course for the slightest infraction. 13

Das könnte Ihnen auch gefallen

- MPT 3Dokument8 SeitenMPT 3rajat7169451734Noch keine Bewertungen

- MPT IvDokument8 SeitenMPT Ivrajat7169451734Noch keine Bewertungen

- MATHS Progression TestDokument4 SeitenMATHS Progression Testrajat7169451734Noch keine Bewertungen

- G.K III Term QuestionsDokument3 SeitenG.K III Term Questionsrajat7169451734Noch keine Bewertungen

- How To Install Linux: Installing Any Linux DistributionDokument3 SeitenHow To Install Linux: Installing Any Linux Distributionrajat7169451734Noch keine Bewertungen

- Excel Lab ManualDokument79 SeitenExcel Lab Manualrajat716945173450% (2)

- Format For Preparation of Project Report FOR B. TechDokument9 SeitenFormat For Preparation of Project Report FOR B. Techrajat7169451734Noch keine Bewertungen

- Dbms Complete Lab ManualDokument184 SeitenDbms Complete Lab Manualrajat7169451734Noch keine Bewertungen

- Final Year Project Report CSEDokument5 SeitenFinal Year Project Report CSErajat71694517340% (1)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (345)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- This Study Resource Was: CelloDokument4 SeitenThis Study Resource Was: CelloVijju Battini100% (1)

- Instruction Templates of Microprocessor 8086Dokument5 SeitenInstruction Templates of Microprocessor 8086Tafzeel Mohammad100% (3)

- I#413 Muhamad Ali-FaiqDokument6 SeitenI#413 Muhamad Ali-FaiqAnonymous X7WdfpfwgNoch keine Bewertungen

- Ingles para Principiantes - PRE U - TIGRE PDFDokument128 SeitenIngles para Principiantes - PRE U - TIGRE PDFPreu UnprgNoch keine Bewertungen

- EncapsulationDokument13 SeitenEncapsulationKainat KabeerNoch keine Bewertungen

- Content Criticism of HadithDokument167 SeitenContent Criticism of HadithNanang NurcholisNoch keine Bewertungen

- f5 Bigip v13 Secassessment PDFDokument105 Seitenf5 Bigip v13 Secassessment PDFBttrngrmNoch keine Bewertungen

- Witold Gombrowicz Bacacay 1Dokument62 SeitenWitold Gombrowicz Bacacay 1StarastenkoNoch keine Bewertungen

- Chapman, A. - Is Sid Meier's Civilization HistoryDokument23 SeitenChapman, A. - Is Sid Meier's Civilization HistorydserranolozanoNoch keine Bewertungen

- OCP Oracle Certified Professional Java SE 11 Programmer II Study Guide: Exam 1Z0-816 and Exam 1Z0-817 - Scott SelikoffDokument6 SeitenOCP Oracle Certified Professional Java SE 11 Programmer II Study Guide: Exam 1Z0-816 and Exam 1Z0-817 - Scott Selikofflydyfipi0% (1)

- KMA002 - Applied Mathematics Foundation: Linear AlgebraDokument33 SeitenKMA002 - Applied Mathematics Foundation: Linear AlgebramikeyNoch keine Bewertungen

- Women, Jung and The Hebrew BibleDokument23 SeitenWomen, Jung and The Hebrew BibleArnold HailNoch keine Bewertungen

- The Role of Jesus Resurrection in The Epistle To The Hebrews Once Again A Brief Response To Jean Rene MoretDokument7 SeitenThe Role of Jesus Resurrection in The Epistle To The Hebrews Once Again A Brief Response To Jean Rene MoretJosh BloorNoch keine Bewertungen

- Ammaleh Ganja Gopaleh DadaDokument3 SeitenAmmaleh Ganja Gopaleh DadaDazzlingpop SparkNoch keine Bewertungen

- Doctrine of The Sabbath.Dokument73 SeitenDoctrine of The Sabbath.Steve SparksNoch keine Bewertungen

- Socratic Seminar Questions - Parts 3 and 4Dokument3 SeitenSocratic Seminar Questions - Parts 3 and 4James HollomanNoch keine Bewertungen

- AMEB Theory Terms and Signs - InddDokument9 SeitenAMEB Theory Terms and Signs - InddRebekah Tan100% (3)

- CP R80.20.M1 Gaia AdminGuideDokument266 SeitenCP R80.20.M1 Gaia AdminGuideVenkatesh KonadaNoch keine Bewertungen

- 1 s2.0 S0889490605000530 MainDokument4 Seiten1 s2.0 S0889490605000530 Main邱琦Noch keine Bewertungen

- Ultrasonic TransDokument21 SeitenUltrasonic TransULFAT HUSSAINNoch keine Bewertungen

- CV - 2021 07 03 072308Dokument2 SeitenCV - 2021 07 03 072308Flair Gamemade (CERAGEM Member CAMBODIA)Noch keine Bewertungen

- Levman-Pali The Language The Medium and MessageDokument1 SeiteLevman-Pali The Language The Medium and MessageAnandaNoch keine Bewertungen

- Reduced Relative Clauses-Presentation-Final VersionDokument9 SeitenReduced Relative Clauses-Presentation-Final Versionbgorgulu_yeditepe100% (2)

- Uses of MSDokument3 SeitenUses of MSTalha IqbalNoch keine Bewertungen

- Verri Puku ScribdDokument584 SeitenVerri Puku Scribdajax248590Noch keine Bewertungen

- Cisco c1111Dokument5 SeitenCisco c1111Eddy Josse MoreloNoch keine Bewertungen

- (Review of International Studies 2004-Apr Vol. 30 Iss. 2) Review by - JefDokument17 Seiten(Review of International Studies 2004-Apr Vol. 30 Iss. 2) Review by - JefBianca SferleNoch keine Bewertungen

- CrashDokument37 SeitenCrashRiccardoGirardiNoch keine Bewertungen

- Romeo and Juliet Test MCDokument5 SeitenRomeo and Juliet Test MCJackeline ChanNoch keine Bewertungen

- Y10 English Language Remote Learning 25.1.2021Dokument14 SeitenY10 English Language Remote Learning 25.1.2021Elllie TattersNoch keine Bewertungen