Beruflich Dokumente

Kultur Dokumente

A 2.4-Ghz Ism-Band Sliding-If Receiver With A 0.5-V Supply

Hochgeladen von

Karim H. MohamedOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

A 2.4-Ghz Ism-Band Sliding-If Receiver With A 0.5-V Supply

Hochgeladen von

Karim H. MohamedCopyright:

Verfügbare Formate

1138

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 43, NO. 5, MAY 2008

A 2.4-GHz ISM-Band Sliding-IF Receiver With a 0.5-V Supply

Neboja Stanic, Member, IEEE, Ajay Balankutty, Peter R. Kinget, Senior Member, IEEE, and s Yannis Tsividis, Fellow, IEEE

AbstractWe report an ultra-low-voltage RF receiver for applications in the 2.4 GHz band, designed in a 90 nm CMOS technology. The sliding-IF receiver prototype includes an LNA, an image-reject LC lter with single-ended to differential conversion, an RF mixer, an LC IF lter, a quadrature IF mixer, RF and IF LO buffers, and an I/Q baseband section with a VGA and a low-pass channel-select lter in each path, all integrated on-chip. It has a programmable overall gain of 30 dB, noise gure of 18 dB, out-of-channel IIP3 of 22 dBm. The 3.4 mm2 chip consumes 8.5 mW from a 0.5 V supply. Index TermsCoupled resonator lter, low-voltage circuits, lowvoltage receivers, sliding IF, 0.5 V circuits.

I. INTRODUCTION MOS technology scaling is dictated mainly by the requirements of digital circuits and is moving towards shorter channel lengths, enabling denser and faster digital systems. Supply voltages scale down together with device sizes, while transistor threshold voltages remain at a relatively high level, for leakage reduction in the digital circuits OFF state. Analog and RF interfaces must often coexist on the same chip with digital systems to make possible economical mixed-signal system-on-chip solutions. It may be required that all circuits in such a system use only thin-gate devices with a single supply. Analog and RF circuits in high-end applications require substantial gate voltage overdrive to maintain device speed. As technology scaling has lead to reduced voltage headroom, analog and RF designs have become increasingly difcult. The range of the possible signal and interferer power levels at the input of the receiver is wide, while maximum voltage swings in the RF and analog circuits decrease with the scaling of CMOS technology. The high signal-to-unwanted-signal ratio required for good reception is becoming harder to maintain. Circuit topologies with small number of stacked devices need to be used to maximize the available signal swing. Additionally, sufcient gain programmability is a necessity to maximize signal handling capabilities. Anticipating the future challenges imposed on analog and RF design by the supply voltage reduction associated with CMOS

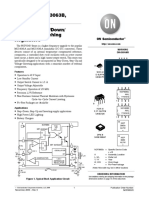

technology scaling into nanoscale dimensions [1], we designed an RF receiver operating from a 0.5 V supply. To determine how close one can get to commercial specications, we extended our earlier low-voltage work, which included an LNA+mixer front-end [2], and a low-pass lter [3], to a complete front end [4]. In our true-low voltage design, all building blocks operate from the nominal supply and no internal voltage boosting has been used. A sliding-IF receiver architecture was selected as shown in Fig. 1 [5]. The frequencies of the LO signals are chosen to 1.6 GHz and 0.8 GHz. The power at the be image-frequency, located also around 0.8 GHz, is suppressed with help of on-chip bandpass ltering before RF downconversion (some of the ltering is typically off-chip to get good overall image rejection). The IF downconversion translates the selected channel to the baseband where it is processed by a low-pass lter, preceded by an amplifying stage with variable gain control, for both I and Q channels. The general advantages of the sliding-IF architecture are reduced and mostly xed DC offset compared to direct conversion, and the use of a single frequency synthesizer and a divide-by-two circuit to generate the RF and IF LO, unlike in a heterodyne receiver. Having only one RF mixer (non-quadrature) with a single-phase LO, operating at 2/3 of the signal frequency, is more suitable for low-voltage operation where speed is an issue. Quadrature LO generation at 1/3 of the signal frequency is also advantageous, compared to the same at the signal frequency in direct conversion. Additionally, passive ltering at IF is possible to help eliminate some of the out-of-band blockers. The challenges lie in the presence of an image frequency and in having two down-converting steps, requiring additional circuitry. There is an area penalty due to the required on-chip passive lters.

II. RF SECTION BLOCKS Fig. 2 shows the schematic of the 2.4-GHz LNA, the LC image-reject lter, the 2.4-GHz-to-800-MHz RF mixer, the LC IF lter, and the IF mixer for the I channel. To maintain sufcient performance in the receiver RF front-end circuits, stacks of multiple transistors have been avoided and forward body-source biasing has been used to reduce the threshold voltages of the regular-threshold devices used. The bodies of the nMOS devices were connected to the supply rail, while the bodies of the pMOS devices were connected to the ground potential [6]. Since the supply voltage is only 0.5 V, this does not create leakage issues in the forward-biased source-body junctions, or latch-up problems.

Manuscript received September 17, 2007; revised January 21, 2008. This work was supported by grants from Intel Corporation and Analog Devices Inc. Chip prototypes were manufactured by United Microelectronics Corporation (UMC). N. Stanic was with Columbia University, New York, NY 10027 USA, and is now with Silicon Laboratories, Somerset, NJ 08873 USA (e-mail: nebojsa. stanic@ieee.org). A. Balankutty, P. Kinget, and Y. Tsividis are with the Department of Electrical Engineering, Columbia University, New York, NY 10027 USA (e-mail: ajay@cisl.columbia.edu; peter.kinget@ieee.org; tsividis@ee.columbia.edu). Digital Object Identier 10.1109/JSSC.2008.920357

0018-9200/$25.00 2008 IEEE

STANIC et al.: A 2.4-GHZ ISM-BAND SLIDING-IF RECEIVER WITH A 0.5-V SUPPLY

1139

Fig. 1. Block diagram of 2.4 GHz sliding-IF receiver.

Fig. 2. Schematic of the receiver RF section.

A. LNA and Image-Reject Filter A common-source inductively degenerated LNA creates a single-ended matched 50 input, saving power over a differential design. The off-chip part of the matching network is formed of an AC coupling capacitor, and a combination of trace and bondwire inductance. The LNA gain can be lowered by 12 dB by steering part of its current to the and . The LNA load supply, using control signals is an on-chip fourth-order coupled-resonator bandpass LC lter, shown in Fig. 2.

The use of the sliding-IF architecture and choice of the intermediate frequency cause the image to be far from the band of interest. Thus, the lter is allowed to have a passband broader than the communication band itself while still achieving good image rejection. We chose a fourth-order bandpass lter for this task. The lter response is centered around the 2.4 GHz band, and has bandwidth of around 600 MHz (ISM band is located between 2.4 GHz and . 2.48 GHz). The required quality factor of the lter is Therefore, we used LC resonators without -enhancement to build this lter. The lter is realized with weakly mag-

1140

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 43, NO. 5, MAY 2008

Fig. 5. Layout of the coupled inductors of the 2.4 GHz IR lter and balun. Fig. 3. Simulated frequency responses of a fourth-order lter: the ideal lter with shunt termination resistances (at pass-band response) and the lter with series inductor loss as termination resistances (sloped pass-band response).

Fig. 4. In a balun, asymmetry arises in the secondary outputs due to the capacitive parasitic between the windings.

netically coupled symmetric spirals and performs single-ended to differential signal conversion. Instead of the shunt termination resistances, commonly used in ideal doubly-terminated coupled resonator LC lter with parallel resonators, we used series loss (resistance) of the inductors in the lter to set the desired quality factors of the two LC resonators. This change in the lter topology causes a distortion in the frequency response of the lter, manifested in a slope in the passband compared to the ideal frequency response, as shown in Fig. 3. The gain of the lter slopes 5 dB over the entire band, but less than 1 dB over the 80 MHz communication band, which is acceptable. A similar phenomenon is reported in [7]. Transformers with strong magnetic coupling between the primary and the secondary winding can also have a strong asymmetric parasitic capacitive coupling between the inductors when the transformer is operated as a balun. The asymmetry is explained schematically in Fig. 4, using a simple lumped model. The parasitic coupling causes an imbalance in the voltage amplitude at the two secondary outputs and results in a phase difference of the two voltages other than the desired 180 . Fig. 5 shows the layout of the two coupled inductors in the lter imis required, plementation. Since only weak coupling a staggered layout can be used. This reduces the parasitic capacitance between the primary and secondary of this transformer. Thus, good symmetry between the differential secondary out-

Fig. 6. Frequency responses of the lter for several consecutive capacitance settings.

puts is achieved. In electromagnetic simulation, the gain imbalance in the passband was less than 0.2 dB and the phase difference was 181 2 degrees in 4 GHz band across the passband. The two inductors occupy area of 250 m by 300 m, not a large increase compared to a single inductor LNA load. The lter dissipates no DC power and its single-ended-to-differential conversion performance is superior to off-chip baluns. The associated 6 dB voltage loss (equivalent to 3 dB insertion loss) occurs after the LNA, and the penalty in terms of noise gure is not large. The center frequency of the lter is tuned using a combination of MOS switches and interdigitated MIM capacitors, through a . The interdigitated capacitors 5-bit digital tuning word were implemented using M1M6 interconnect. In simulation, the LNA/lter combination achieves 18 dB gain, 12 dBm IIP , and 2 dB noise gure, for a supply current of 4 mA. B. First and Second Downconversion The outputs of the image-reject lter are DC-coupled to the inputs of the RF mixer, as shown in Fig. 2. A switched-

STANIC et al.: A 2.4-GHZ ISM-BAND SLIDING-IF RECEIVER WITH A 0.5-V SUPPLY

1141

Fig. 7. Block diagram of the lter tuning algorithm to determine the optimal tank capacitance setting.

transconductor mixer topology [2], [8], was selected to be compatible with the ultra-low-voltage supply. The sources of transconductor transistors are switched from on-chip LO buffers which provide a square-wave LO signal, driven by an external sinusoidal generator. The mixer output load is a tuned on-chip LC IF lter, implemented and tuned in a similar fashion as the image-reject lter, via a 5-bit digital tuning word . In simulation, the RF mixer achieves 3 dB voltage gain, 10 dBVrms IIP3, 21 dBVrms input-referred 1-dB compression point and 20 dB noise gure, for supply currents of 2.4 mA in the core mixer and 3.4 mA in the LO buffers. The IF-to-baseband down-conversion is performed using quadrature passive mixers which are AC-coupled to the IF lter output. The use of passive mixers saves power dissipation, maintains good linearity, and does not signicantly worsen the noise gure of the receiver, since it comes after sufcient front-end gain. The IF mixer LO signals are generated in a similar way as for the rst mixer. With supply current of 1.6 mA in the LO buffers, simulated results for the IF mixer are 5 dB voltage gain, 3 dBVrms IIP3, 20 dBVrms input-referred 1-dB compression point and 26 dB noise gure. C. Filter Tuning In this section, we describe a method for direct tuning of the implemented LC lter. Fig. 6 shows simulated frequency responses of the LC lter for several resonator capacitance settings. The capacitance is varied at a minimal step between the responses, using the 5-bit control word. If we apply a test tone to the input of the lter at about 2.4 GHz (i.e., at the communication band center frequency) the amplitude of the signal at the output of the lter will be different for the different capacitance values. We observe from Fig. 6 that the amplitude at the output has a single local maximum at the control point indicated in black. Thus, we can realize the frequency tuning of our lter by measuring the magnitude of the response at the output and maximizing it when a test tone at the frequency equal to the center frequency of the communication band is applied at the input of the lter. The measurement of the amplitude of the high-frequency signal at the lter output can be performed using mostly the existing signal processing circuits in the receiver chain, as

shown in Fig. 7. This can be done in the time slots when the receiver is idle, for example at the power-up of the entire transceiver. Additional mixing circuits are required to form a 2.4 GHz , where is baseband test tone at frequency. The 2.4 GHz tone can be created by quadrature (image-reject) mixing of the existing local oscillator signals at 1.6 GHz and 0.8 GHz, which also rejects the undesired mixing product at 0.8 GHz. The produced test tone can be then applied either at the input to the LNA (provided that the leakage to the antenna is not excessive), or at the input to the lter, whichever is more convenient. After the lter, the signal passes through the mixers in the receiver chain, getting downconverted to the baseband, amplied and converted to digital form. The output of the chain is a digital signal at frequency , whose magnitude is proportional to the magnitude of the frequency response of the lter. One possible tuning algorithm is to obtain this digital output for each capacitance setting in the lter (there is 32 different settings), and by comparison, nd which tuning word produces the aforementioned maximum. The result of this operation would be a stored tuning word applied back to the lter. Hz in the above method, the signal carrying the For information about the frequency response of the lter would be at DC (0 Hz) when it reaches the DSP. Since the receiver may have offset cancelation applied, which is essentially high-pass ltering in the signal path, the information we need for tuning can be lost. To overcome this problem, it is necessary to move ( should be an in-channel away from 2.4 GHz tone by frequency). To test the described tuning system in simulation, we applied a 100 A current at frequency of 2.401 GHz to the input to the lter, and measured the magnitude of the 1 MHz signal at the output of the baseband lter set to have a cutoff frequency of 1 MHz and maximum gain. For different capacitance settings in the lter, we obtained a plot in Fig. 8. The output voltage has a single maximum, and the sensitivity of the response is high enough for detection in the digital part of the tuning circuitry. The maximum of the output voltage in Fig. 8 corresponds to the same capacitance setting which results in the frequency response of the lter marked in black in Fig. 6.

1142

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 43, NO. 5, MAY 2008

Fig. 8. Simulated magnitude of the 1 MHz signal measured at the output of the baseband lter for different capacitance settings in the RF lter.

III. BASEBAND SECTION BLOCKS Each baseband path has a variable gain amplier (VGA) with programmable gain implemented using switchable resistors at the input of an operational transconductance amplier (OTA), as shown in Fig. 9. The VGA drives an on-chip channel-select lter which is a fth-order Chebyshev low-pass lter [9] realized with a leapfrog active-RC fully-balanced topology with dynamic range scaling [10]. The capacitor across the feedback resistor of the VGA lters out the high-frequency signals from the mixer, with a cutoff frequency of 20 MHz. The main lter has 0.5 dB ripple, and is made tunable through the use of switchable capacitor arrays. The cutoff frequency is tunable from 1 to 3.1 MHz, with a nominal frequency step of 25 kHz. This can be used to accommodate different types of signal bandwidths for low or zero-IF operation: for the reception of narrowband signals such as Bluetooth [11] a low-IF frequency plan can be selected; for wideband signals as in Zigbee [12] a zero-IF frequency plan can be used [9]. The lter poles are realized with high-resistivity poly resistors and with MOS capacitors. Two-stage Miller-compensated OTAs are used for the VGA and lter (Fig. 10). The input stage can be operated from a by using threshold voltage common-mode voltage of devices. The is lowreduction techniques for the regular ered with forward body-biasing and by taking advantage of reduction due to reverse short channel effect by using non-minimum length devices. Depending on the sizing of the device and applied body bias, the threshold voltage can be lowered by and is furup to 70 mV. The input transistor pair -efciency. To get ther biased in weak inversion for higher rail-to-rail swing for the second stage, the swing required in the rst stage is lower by a factor equal to the gain of the second along with stage (which is about 10 V/V). The lowering of the reduced signal swing for the rst stage enables stacking of three devices. Due to the low supply voltage, no cascode devices could be inserted to achieve a sufciently high DC-gain, and is and instead, a cross-coupled differential pair used to create a negative conductance at the rst stage output. The negative conductance was carefully sized and biased such that it cancels only one third of the total node conductance and

Fig. 9. Schematic of the receiver baseband section.

improves the gain by about 8 dB. This sizing ensures that the OTA will not develop any hysteresis [3] over process, voltage and temperature corner conditions. The use of a tail current source for the input pair suppresses the propagation of common-mode signals. Additional common-mode rejection is achieved by local common-mode and for the feedback for each stage using resistors and for the second stage. All OTA rst stage and bias voltages are generated on-chip using replica circuits. The circuit in Fig. 10(b) replicates the bias conditions for the input and to set the pair devices and generates input pair current. The current in the second OTA stage is then also xed through the DC current mirorring action of and . The OTA output common-mode via a level shifting current DC voltage is adjusted to controlled by the bias voltage as shown source variations, an in Fig. 10(c). To provide for compensation of , is generated adaptive body bias for the nMOS devices, on-chip (Fig. 10(d)). The size of the transistor in Fig. 10(d) and the reference current (supplied through external pins) is is 250 mV in the typical process chosen such that variations, adjusts (from corner. When there are of the transistor is 0 to 500 mV) such that the effective is generated maintained relatively constant. Similarly, for pMOS devices (not shown). The nominal simulated OTA gain was 45 dB and the unity gain frequency was 175 MHz. The OTAs were scaled proportional to the load for each lter stage to minimize power consumption. IV. RESULTS The microphotograph of the prototype realized in a 90 nm CMOS technology is shown in Fig. 11. The area of the chip is 2.6 1.3 mm . The chip was bonded to a 10 by 10 mm QFN plastic package and mounted on a PCB for testing. Off-chip

STANIC et al.: A 2.4-GHZ ISM-BAND SLIDING-IF RECEIVER WITH A 0.5-V SUPPLY

1143

Fig. 10. Schematic of the two-stage OTA for the baseband VGA and lter; (b)-(d) on-chip automatic replica biasing circuits (some body biasing details omitted).

Fig. 11. Die photograph of the receiver prototype with extra test structures and test pads.

baluns at the LO inputs and a differential probe at the receiver output were used to interface with the single-ended measurement equipment. The measurements are performed from the single-ended LNA , one of the receivers differential quadrature outinput, to puts; see Fig. 1. Fig. 12 shows the measured gains of parts of the chain normalized to their peak value, as well as the degree of , versus frequency. The on-chip lter eninput matching sures at least 26 dB of measured image rejection at the 850 MHz image frequency. This, in combination with more than 30 dB of image rejection typically provided by the off-chip band-select lter between the antenna and the receiver input (see for example Murata lter LFB212 G45 SG8 A166 [13]), results in a sufcient overall image suppression of better than 56 dB. The combined rejection of the LNA input matching network and the LC IR lter was measured by sweeping while keeping

Fig. 12. Measured frequency responses at the outputs of the IR and IF lters and the reection coefcient at the RF input (see text for measurement details).

at a constant offset of 801 MHz from and setting at 800 MHz which produces a 1 MHz output signal for all input frequencies; this arrangement allows to measure the response of the RF section independent of the IF sections. A similar measurement technique was used to obtain the shape of the response of the IF lter. The input reection coefcient for the RF input was lower than 10 dB in a 500 MHz band around the center frequency of the RF lter. The baseband section was measured separately by applying a differential input to the VGA input through test pads. Figs. 13 and 14 show the baseband transfer characteristics measured

1144

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 43, NO. 5, MAY 2008

TABLE I SUMMARY OF RECEIVER PERFORMANCE

Fig. 13. Measured frequency response of the baseband lter for different VGA gain settings.

Fig. 14. Measured frequency response of the baseband lter for different cutoff frequency settings. TABLE II COMPARISON

from the VGA input to the lter output for different gain and cutoff frequency settings. Instead of varactors as in [3], digitally selected capacitors using analog switches were used to tune the lter, which improved lters in-band linearity by 8 dB over [3]; additonally, the lter bandwidth is more than 10 times higher and the power consumption is less than half compared to [3]. The measured performance of the receiver and of several of its building blocks is summarized in Table I for different gain settings and supply voltages; the chip operates reliably over a 10% supply voltage range. Table II compares this work to other existing Bluetooth, Zigbee and sensor-application receivers operating in the 2.4 GHz ISM band. V. CONCLUSION Our ultra-low-voltage 0.5 V receiver exceeds the noise specications from the Bluetooth standard [11] and is very close to meeting the linearity requirements while having a low power consumption. The noise performance is just sufcient for Zigbee applications but the linearity is not sufcient [12]. In the high-gain mode, the receiver linearity is limited by the VGAs linearity and design improvements are currently being explored to further improve the design.

STANIC et al.: A 2.4-GHZ ISM-BAND SLIDING-IF RECEIVER WITH A 0.5-V SUPPLY

1145

ACKNOWLEDGMENT The transformer, inductors, and comb capacitors were designed with the EMX simulator of Integrand Software. REFERENCES [1] The International Technology Roadmap for Semiconductors. 2004 [Online]. Available: http://public.itrs.net [2] N. Stanic, P. Kinget, and Y. Tsividis, A 0.5 V 900 MHz receiver front end, in Symp. VLSI Circuits Dig., Jun. 2006, pp. 282283. [3] S. Chatterjee, Y. Tsividis, and P. Kinget, 0.5-V analog circuit techniques and their application in OTA and lter design, IEEE J. SolidState Circuits, vol. 40, no. 12, pp. 23732387, Dec. 2005. [4] N. Stanic, A. Balankutty, P. Kinget, and Y. Tsividis, A 0.5 V receiver in 90 nm CMOS for 2.4 GHz applications, in IEEE Radio Frequency Integrated Circuits (RFIC) Symp. Dig. Tech. Papers, Jun. 2007, pp. 109112. [5] A. Zolfaghari and B. Razavi, A low-power 2.4-GHz transmitter/receiver CMOS IC, IEEE J. Solid-State Circuits, vol. 38, no. 2, pp. 176183, Feb. 2003. [6] S. Narendra, J. Tschanz, J. Hofsheier, B. Bloechel, S. Vangal, Y. Hoskote, S. Tang, D. Somasekhar, A. Keshavarzi, V. Erraguntla, G. Dermer, N. Borkar, S. Borkar, and V. De, Ultra-low voltage circuits and processor in 180 nm to 90 nm technologies with a swapped-body biasing technique, in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2004, pp. 156157, 518. [7] D. Li and Y. Tsividis, Design techniques for automatically tuned integrated gigahertz-range active LC lters, IEEE J. Solid-State Circuits, vol. 37, no. 8, pp. 967977, Aug. 2002. [8] E. Klumperink, S. Louwsma, G. Wienk, and B. Nauta, A CMOS switched transconductor mixer, IEEE J. Solid-State Circuits, vol. 39, no. 8, pp. 12311240, Aug. 2004. [9] B. Guthrie, J. Hughes, T. Sayers, and A. Spencer, A CMOS gyrator low-IF lter for a dual-mode Bluetooth/Zigbee transceiver, IEEE J. Solid-State Circuits, vol. 40, no. 9, pp. 18721879, Sep. 2005. [10] M. Banu and Y. Tsividis, Fully integrated active RC lters in MOS technology, IEEE J. Solid-State Circuits, vol. SSC-18, no. 6, pp. 644651, Dec. 1983. [11] S. Ozev, C. Olgaard, and A. Orailoglu, Testability implications in lowcost integrated radio transceivers: A Bluetooth case study, in Proc. IEEE Int. Test Conf., Oct. 2001, pp. 965974. [12] N.-J. Oh and S.-G. Lee, A CMOS 868/915 MHz direct conversion Zigbee single-chip radio, IEEE Commun. Mag., vol. 43, no. 12, pp. 100109, Dec. 2005. [13] Filters/Components/Modules for Communication Equipment. 2006 [Online]. Available: http://www.murata.com [14] J. A. M. Jarvinen, J. Kaukovuori, J. Ryynanen, J. Jussila, K. Kivekas, M. Honkanen, and K. A. I. Halonen, 2.4-GHz receiver for sensor applications, IEEE J. Solid-State Circuits, vol. 40, no. 7, pp. 14261433, Jul. 2005. [15] H. J. Bergveld, M. M. Kees, V. Kaam, M. W. Leenaerts, K. J. P. Philips, W. P. Vassen, and G. Wetkzer, A low-power highly digitized receiver for 2.4-GHz-band GFSK applications, IEEE Trans. Microw. Theory Tech., vol. 53, no. 2, pp. 453461, Feb. 2005. [16] M. Ugajin, A. Yamagishi, J. Kodate, M. Harada, and T. Tsukahara, Design techniques for a 1-V operation Bluetooth RF transeiver, in Proc. IEEE Custom Integrated Circuits Conf. (CICC), Oct. 2004, pp. 965974.

Neboja Stanic (M05) received the Dipl. Ing. des gree in electrical engineering from University of Belgrade, Serbia, in 1999, and the M.S. and Ph.D. degrees from Columbia University, New York, NY, in 2003 and 2007, respectively. He is working with Silicon Laboratories, Somerset, NJ, in areas of analog and RF integrated circuits and signal processing.

Ajay Balankutty received the B.Tech. degree in electronic and communication engineering from the National Institute of Technology, Calicut, India, in 2001, and the M.S. degree in electrical engineering from Columbia University, New York, NY, in 2006. Currently, he is working toward the Ph.D. degree at Columbia University. From 2001 to 2005, he was with Analog Devices, Inc., Bangalore. His current research interests include analog, RF and millimeter wave circuits.

Peter R. Kinget (M90SM02) received the engineering degree (summa cum laude) in electrical and mechanical engineering and the Ph.D. degree (summa cum laude) in electrical engineering from the Katholieke Universiteit Leuven, Belgium, in 1990 and 1996, respectively. From 1991 to 1995, he received a graduate fellowship from the Belgian National Fund for Scientic Research (NFWO) to work as a Research Assistant at the ESAT-MICAS Laboratory of the Katholieke Universiteit Leuven. From 1996 to 1999, he was at Bell Laboratories, Lucent Technologies, in Murray Hill, NJ, as a Member of Technical Staff in the Design Principles Department. From 1999 to 2002, he held various technical and management positions in IC design and development at Broadcom, CeLight and MultiLink. In the summer of 2002, he joined the faculty of the Department of Electrical Engineering, Columbia University, New York, NY. He is also a consultant to industry. His research interests are in analog and RF integrated circuits and signal processing. He has published over 70 papers in journals and conferences and holds six U.S. patents with several applications under review. His research group has received funding from the National Science Foundation, the Semiconductor Research Corporation, an IBM Faculty Award and from several grants from semiconductor companies. Dr. Kinget was an Associate Editor for the IEEE JOURNAL OF SOLID-STATE CIRCUITS from 2003 to 2007. He has served on the Technical Program Committee of the IEEE Custom Integrated Circuits Conference (CICC) and the the IEEE Symposium on VLSI Circuits. He currently serves on the Technical Program Committee of the European Solid-State Circuits Conference and the IEEE International Solid-State Circuits Conference.

Yannis Tsividis (M74SM81F86) received the B.S. degree from the University of Minnesota, Minneapolis, and the M.S. and Ph.D. degrees from the University of California, Berkeley, in 1972, 1973, and 1976, respectively. He is the Charles Batchelor Memorial Professor of Electrical Engineering at Columbia University, New York, NY. He has worked at Motorola Semiconductor and AT&T Bell Laboratories, and has taught at the University of California at Berkeley, the Massachusetts Institute of Technology, and the National Technical University of Athens, Greece. Dr. Tsividis is the recipient of the 1984 IEEE W. R. G. Baker Best Paper Award, the 1986 European Solid-State Circuits Conference Best Paper Award, and the 1998 IEEE Circuits and Systems Society Guilllemin-Cauer Best Paper Award. He is a co-recipient of the 1987 IEEE Circuits and Systems Society Darlington Best Paper Award and the 2003 IEEE International Solid-State Circuits Conference L. Winner Outstanding Paper Award. He received the IEEE Gustav Robert Kirchhoff Award in 2007, the Presidential Teaching Award from Columbia University in 2003, and the IEEE Undergraduate Teaching Award in 2005.

Das könnte Ihnen auch gefallen

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- SolvedTechnical Papers by IftikharDokument26 SeitenSolvedTechnical Papers by IftikharNoman Ahmed100% (5)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (587)

- 59 Instrumentation Interview Questions and AnswersDokument13 Seiten59 Instrumentation Interview Questions and AnswersplanningratnagiriNoch keine Bewertungen

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (890)

- TOP246YNDokument49 SeitenTOP246YNjoelpalzaNoch keine Bewertungen

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Super CapacitorDokument14 SeitenSuper CapacitorBien Morfe100% (1)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- Integrated - Power - Designs SRP 30A 2005 DatasheetDokument5 SeitenIntegrated - Power - Designs SRP 30A 2005 DatasheetJorge Andres SantistebanNoch keine Bewertungen

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- WBJEE 2019 Physics and Chemistry answers and hintsDokument22 SeitenWBJEE 2019 Physics and Chemistry answers and hintsAmogh VaishnavNoch keine Bewertungen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- NEET 2019 Answer Key Solution Code P1 by GovtDokument63 SeitenNEET 2019 Answer Key Solution Code P1 by GovtmisostudyNoch keine Bewertungen

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- CT Z1425 FinalDokument33 SeitenCT Z1425 FinalRodolfo ArosemenaNoch keine Bewertungen

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- BGM User ManualDokument48 SeitenBGM User ManualAlgebra92Noch keine Bewertungen

- Electrical Power System Design For Industrial FacilitiesDokument29 SeitenElectrical Power System Design For Industrial Facilitiesgusgon521292100% (1)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- 0185-1062-E 6V12 IG Drives C1100Dokument29 Seiten0185-1062-E 6V12 IG Drives C1100asdlksadasfNoch keine Bewertungen

- Electrical Exterior Facilities SpecificationDokument203 SeitenElectrical Exterior Facilities Specificationirshad018Noch keine Bewertungen

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Lahore Converter Station Operation Regulations Volume 1 (Equipment Overview) .Zh-CN.en (1) -拉合尔换流站运行规程第1分册(设备概况).Zh-CN.enDokument185 SeitenLahore Converter Station Operation Regulations Volume 1 (Equipment Overview) .Zh-CN.en (1) -拉合尔换流站运行规程第1分册(设备概况).Zh-CN.enUsama ZafarNoch keine Bewertungen

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- Ap 3843 CPDokument13 SeitenAp 3843 CPJesus ChaileNoch keine Bewertungen

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2219)

- NCP3063, NCP3063B, NCV3063 1.5 A, Step-Up/Down/ Inverting Switching RegulatorsDokument19 SeitenNCP3063, NCP3063B, NCV3063 1.5 A, Step-Up/Down/ Inverting Switching RegulatorschawkigenieNoch keine Bewertungen

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- Physics Lab Report GuideDokument18 SeitenPhysics Lab Report GuideTural UsubovNoch keine Bewertungen

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- Clarion Ps3021na NB 3022na NBDokument22 SeitenClarion Ps3021na NB 3022na NBDiego ToledoNoch keine Bewertungen

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (265)

- Magnetic Flux Leakage Testing: HapterDokument19 SeitenMagnetic Flux Leakage Testing: HapterkingstonNoch keine Bewertungen

- PROBLEM SET ANALYSISDokument32 SeitenPROBLEM SET ANALYSISSarthak JainNoch keine Bewertungen

- High-Frequency Model of The Power Transformer Based On Frequency-Response MeasurementsDokument9 SeitenHigh-Frequency Model of The Power Transformer Based On Frequency-Response MeasurementsFernando PaezNoch keine Bewertungen

- LG TV Service ManualDokument76 SeitenLG TV Service Manualrakso_o67% (3)

- Chap-2-Transient Over VoltagesDokument68 SeitenChap-2-Transient Over VoltageschalaNoch keine Bewertungen

- Phase-Control Circuit - General Purpose Feedback: DescriptionDokument22 SeitenPhase-Control Circuit - General Purpose Feedback: DescriptionBoyke WinterbergNoch keine Bewertungen

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- Smart Iii: ComputerDokument2 SeitenSmart Iii: ComputerfaikNoch keine Bewertungen

- MotorsDokument25 SeitenMotorsAyush SrivastavaNoch keine Bewertungen

- TRANSISTORIZED INVERTER OPTIMIZED TITLEDokument226 SeitenTRANSISTORIZED INVERTER OPTIMIZED TITLEThanh BuiNoch keine Bewertungen

- (UPDATED) Compilation of Important Info Don Smith Shared To NuEnergy Yahoo GroupDokument13 Seiten(UPDATED) Compilation of Important Info Don Smith Shared To NuEnergy Yahoo Groupjubeng100% (1)

- A Capacitive Sensor Interface Circuit Based On Phase Differential MethodDokument4 SeitenA Capacitive Sensor Interface Circuit Based On Phase Differential MethodPriyanshu_D_An_1642Noch keine Bewertungen

- Ejercicios AnalogicaDokument22 SeitenEjercicios AnalogicaManel GarciaNoch keine Bewertungen

- 220kv ShornurDokument102 Seiten220kv ShornurAhamed Shahin CkNoch keine Bewertungen

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (119)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)