Beruflich Dokumente

Kultur Dokumente

Octal 3-State Noninverting D Flip-Flop: KK74HC574A

Hochgeladen von

jksb100Originalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Octal 3-State Noninverting D Flip-Flop: KK74HC574A

Hochgeladen von

jksb100Copyright:

Verfügbare Formate

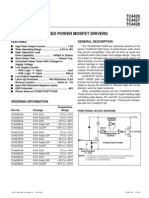

TECHNICAL DATA

KK74HC574A

Octal 3-State Noninverting D Flip-Flop

High-Performance Silicon-Gate CMOS

N SUFFIX PLASTIC DIP

The KK74HC574A is identical in pinout to the LS/ALS574. The device inputs are compatible with standard CMOS outputs; with pullup resistors, they are compatible with LS/ALSTTL outputs. Data meeting the setup time is clocked to the outputs with the rising edge of the Clock. The OE input does not affect the states of the flip-flops, but when OE is high, all device outputs are forced to the high-impedance state; thus, data may be stored even when the outputs are not enabled. Outputs Directly Interface to CMOS, NMOS, and TTL Operating Voltage Range: 2.0 to 6.0 V Low Input Current: 1.0 A High Noise Immunity Characteristic of CMOS Devices

20 1 20 1 DW SUFFIX SOIC

ORDERING INFORMATION

KK74HC574AN Plastic DIP KK74HC574ADW SOIC

TA = -55 to 125 C for all packages

PIN ASSIGNMENT

LOGIC DIAGRAM

OE D0 D1

D0 D1 D2 DATA INPUTS D3 D4 D5 D6 D7 CLOCK 2 3 4 5 6 7 8 9 11 19 18 17 16 15 14 13 12 Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 NONINVERTING OUTPUTS

1 2 3 4 5 6 7 8 9 10

20 19 18 17 16 15 14

13 12 11

V CC

Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 CLOCK

D2 D3 D4 D5 D6 D7 GND

FUNCTION TABLE

Inputs Output

D

H

L

L,H,

X

1 OE

OE

L

Clock

Q

H

L

no change

Z

PIN 20=VCC PIN 10 = GND

L

L

H

X

X

H= high level L = low level X = dont care Z = high impedance

KK74HC574A

MAXIMUM RATINGS*

Symbol VCC VIN VOUT IIN IOUT ICC PD Tstg TL

*

Parameter DC Supply Voltage (Referenced to GND) DC Input Voltage (Referenced to GND) DC Output Voltage (Referenced to GND) DC Input Current, per Pin DC Output Current, per Pin DC Supply Current, VCC and GND Pins Power Dissipation in Still Air, Plastic DIP+ SOIC Package+ Storage Temperature Lead Temperature, 1.5 mm from Case for 4 Seconds (Plastic DIP or SOIC Package)

Value -0.5 to +7.0 -1.5 to VCC +1.5 -0.5 to VCC +0.5 20 35 75 750 500 -65 to +150 260

Unit V V V mA mA mA mW C C

Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the Recommended Operating Conditions. +Derating - Plastic DIP: - 10 mW/C from 65 to 125C SOIC Package: : - 7 mW/C from 65 to 125C

RECOMMENDED OPERATING CONDITIONS

Symbol VCC VIN, VOUT TA tr, tf Parameter DC Supply Voltage (Referenced to GND) DC Input Voltage, Output Voltage (Referenced to GND) Operating Temperature, All Package Types Input Rise and Fall Time (Figure 1) VCC =2.0 V VCC =4.5 V VCC =6.0 V Min 2.0 0 -55 0 0 0 Max 6.0 VCC +125 1000 500 400 Unit V V C ns

This device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high-impedance circuit. For proper operation, VIN and VOUT should be constrained to the range GND(VIN or VOUT)VCC. Unused inputs must always be tied to an appropriate logic voltage level (e.g., either GND or VCC). Unused outputs must be left open.

KK74HC574A

DC ELECTRICAL CHARACTERISTICS(Voltages Referenced to GND)

VC

C

Guaranteed Limit 25 C to -55C 1.5 3.15 4.2 0.5 1.35 1.8 1.9 4.4 5.9 3.98 5.48 0.1 0.1 0.1 0.26 0.26 0.1 0.5 85 C 1.5 3.15 4.2 0.5 1.35 1.8 1.9 4.4 5.9 3.84 5.34 0.1 0.1 0.1 0.33 0.33 1.0 5.0 125 C 1.5 3.15 4.2 0.5 1.35 1.8 1.9 4.4 5.9 3.7 5.2 0.1 0.1 0.1 0.4 0.4 1.0 10 A A V Unit V

Symbol VIH

Parameter Minimum High-Level Input Voltage Maximum Low -Level Input Voltage Minimum High-Level Output Voltage

Test Conditions VOUT VCC-0.1 V IOUT 20 A VOUT 0.1 V IOUT 20 A VIN=VIH IOUT 20 A VIN=VIH IOUT 6.0 mA IOUT 7.8 mA

V 2.0 4.5 6.0 2.0 4.5 6.0 2.0 4.5 6.0 4.5 6.0 2.0 4.5 6.0 4.5 6.0 6.0 6.0

VIL

VOH

VOL

Maximum Low-Level Output Voltage

VIN= VIL IOUT 20 A VIN= VIL IOUT 6.0 mA IOUT 7.8 mA

IIN IOZ

Maximum Input Leakage Current Maximum Three State Leakage Current

VIN=VCC or GND Output in High-Impedance State VIN =VIH VOUT= VCC or GND VIN=VCC or GND IOUT=0A

ICC

Maximum Quiescent Supply Current (per Package)

6.0

4.0

40

160

KK74HC574A

AC ELECTRICAL CHARACTERISTICS (CL=50pF,Input tr=tf=6.0 ns)

VCC Symbol fmax Parameter Maximum Clock Frequency (50% Duty Cycle) (Figures 1 and 4) Maximum Propagation Delay, Clock to Q (Figures 1 and 4) Maximum Propagation Delay, Output Enable to Q (Figures 2 and 5) Maximum Propagation Delay, Output Enable to Q (Figures 2 and 5) Maximum Output Transition Time, Any Output (Figures 1 and 4) Maximum Input Capacitance Maximum Three-State Output Capacitance (Output in High-Impedance State) Power Dissipation Capacitance (Per Enabled Output) CPD Used to determine the no-load dynamic power consumption: PD=CPDVCC2f+ICCVCC V 2.0 4.5 6.0 2.0 4.5 6.0 2.0 4.5 6.0 2.0 4.5 6.0 2.0 4.5 6.0 Guaranteed Limit 25 C to -55C 6.0 30 35 160 32 27 150 30 26 140 28 24 60 12 10 10 15 85C 4.8 24 28 200 40 34 190 38 33 175 35 30 75 15 13 10 15 125 C 4.0 20 24 240 48 41 225 45 38 210 42 36 90 18 15 10 15 Unit MHz

tPLH, tPHL

ns

tPLZ, tPHZ

ns

tPZH, tPZL

ns

tTLH, tTHL

ns

CIN COUT

pF pF

Typical @25C,VCC=5.0 V 24 pF

TIMING REQUIREMENTS (CL=50pF,Input tr=tf=6.0 ns)

VCC Symbol tSU Parameter Minimum Setup Time, Data to Clock (Figure 3) Minimum Hold Time, Clock to Data (Figure 3) Minimum Pulse Width, Clock (Figure 1) Maximum Input Rise and Fall Times (Figure 1) V 2.0 4.5 6.0 2.0 4.5 6.0 2.0 4.5 6.0 2.0 4.5 6.0 25 C to -55C 50 10 9 5 5 5 75 15 13 1000 500 400 Guaranteed Limit 85C 65 13 11 5 5 5 95 19 16 1000 500 400 125C 75 15 13 5 5 5 110 22 19 1000 500 400 Unit ns

th

ns

tw

ns

tr, tf

ns

KK74HC574A

tr CLOCK

90% 50% 10%

tf

VCC VCC GND OE t PZL Q t PHL Q t THL tPZH

50% 50% 50%

GND t PLZ 10% t PHZ 90% HIGH IMPEDANCE VOL VOH HIGH IMPEDANCE

tw 1/fmax tPLH Q

50% 10% 90%

tTLH

Figure 1. Switching Waveforms

VALID D

Figure 2. Switching Waveforms

VCC

50%

GND t su CLOCK

50%

th VCC GND

Figure 3. Switching Waveforms

TEST POINT

TEST POINT 1k CL

*

DEVICE UNDER TEST

OUTPUT

* CL

DEVICE UNDER TEST

OUTPUT

Connect to V CC when testing tPLZ and tPZL Connect to GND when testing tPHZ and tPZH

* Includes all probe and jig capacitance Figure 4. Test Circuit

* Includes all probe and jig capacitance Figure 5. Test Circuit

EXPANDED LOGIC DIAGRAM

D0 D1 D2 D3 D4 D5 D6 D7

D C Q CLOCK

D C Q

D C Q

D C Q

D C Q

D C Q

D C Q

D C Q

OE Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

KK74HC574A

N SUFFIX PLASTIC DIP (MS - 001AD)

Dimension, mm

20 11 B 1 10

Symbol A B C

MIN 24.89 6.1

MAX 26.92 7.11 5.33

D F

0.36 1.14 2.54 7.62 0 2.92 7.62 0.2 0.38

0.56 1.78

C -T- SEATING

PLANE

G H

H J

N G D 0.25 (0.010) M T K M

J K L M N

10 3.81 8.26 0.36

NOTES:

1. Dimensions A, B do not include mold flash or protrusions. Maximum mold flash or protrusions 0.25 mm (0.010) per side.

D SUFFIX SOIC (MS - 013AC)

A 20 11

Dimension, mm Symbol MIN 12.6 7.4 2.35 0.33 0.4 1.27 9.53 0 0.1 0.23 10 0.25 8 0.3 0.32 10.65 0.75 MAX 13 7.6 2.65 0.51 1.27

A B

10 C R x 45

C D F

-TD 0.25 (0.010) M T C M K

SEATING PLANE

G H J K M P R

NOTES: 1. Dimensions A and B do not include mold flash or protrusion. 2. Maximum mold flash or protrusion 0.15 mm (0.006) per side for A; for B 0.25 mm (0.010) per side.

Das könnte Ihnen auch gefallen

- IC-ON-LINE - CN In74hc164a 4331941Dokument6 SeitenIC-ON-LINE - CN In74hc164a 4331941enriquevagoNoch keine Bewertungen

- DatasheetDokument5 SeitenDatasheetIonut SimaNoch keine Bewertungen

- Quad 2-Input AND Gate: KK74HC08ADokument5 SeitenQuad 2-Input AND Gate: KK74HC08Acatsoithahuong84Noch keine Bewertungen

- Octal 3-State Noninverting Transparent Latch: SL74HC573Dokument5 SeitenOctal 3-State Noninverting Transparent Latch: SL74HC573Prayu GarnurmNoch keine Bewertungen

- 74 LV 00Dokument10 Seiten74 LV 00Brzata PticaNoch keine Bewertungen

- HC74Dokument5 SeitenHC74Bruno NascimentoNoch keine Bewertungen

- 74LVC14APWDHDokument11 Seiten74LVC14APWDHIlie GrecuNoch keine Bewertungen

- Mid Semester 2012 TID203Dokument17 SeitenMid Semester 2012 TID203peas002Noch keine Bewertungen

- 74 HC 138Dokument5 Seiten74 HC 138dlbplbNoch keine Bewertungen

- 74AC74, 74ACT74 Dual D-Type Positive Edge-Triggered Flip-FlopDokument13 Seiten74AC74, 74ACT74 Dual D-Type Positive Edge-Triggered Flip-FlopMudasir UmarNoch keine Bewertungen

- SN54HC573A, SN74HC573A Octal Transparent D-Type Latches With 3-State OutputsDokument7 SeitenSN54HC573A, SN74HC573A Octal Transparent D-Type Latches With 3-State OutputsMadhukar PuliNoch keine Bewertungen

- 74 HC 573Dokument5 Seiten74 HC 573Yann Van OsselaerNoch keine Bewertungen

- D D D D D D D D D D D D D: CD74HC08-Q1 Quadruple 2-Input Positive-And GatesDokument8 SeitenD D D D D D D D D D D D D: CD74HC08-Q1 Quadruple 2-Input Positive-And Gatesmalirezazadeh5549Noch keine Bewertungen

- 7473Dokument8 Seiten7473Merényi OszkárNoch keine Bewertungen

- MM74HC245A Octal 3-STATE Transceiver: General DescriptionDokument7 SeitenMM74HC245A Octal 3-STATE Transceiver: General DescriptionMubarak CeNoch keine Bewertungen

- MC74HC541A Octal 3-State Non-Inverting Buffer/Line Driver/ Line ReceiverDokument8 SeitenMC74HC541A Octal 3-State Non-Inverting Buffer/Line Driver/ Line ReceivernandobnuNoch keine Bewertungen

- C.I 74HC175Dokument7 SeitenC.I 74HC175DOMINGOS ALADIRNoch keine Bewertungen

- CD54HC14, CD74HC14, CD54HCT14, CD74HCT14: Features DescriptionDokument16 SeitenCD54HC14, CD74HC14, CD54HCT14, CD74HCT14: Features DescriptionAndrea DispoNoch keine Bewertungen

- DatasheetDokument8 SeitenDatasheetMaizatul Hanisah RoziNoch keine Bewertungen

- CD54HC08, CD74HC08, CD54HCT08, CD74HCT08: Features DescriptionDokument13 SeitenCD54HC08, CD74HC08, CD54HCT08, CD74HCT08: Features DescriptionWissam NawfalNoch keine Bewertungen

- Data SheetDokument6 SeitenData SheetΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣNoch keine Bewertungen

- 74LCX125 Low Voltage Quad Buffer With 5V Tolerant Inputs and OutputsDokument13 Seiten74LCX125 Low Voltage Quad Buffer With 5V Tolerant Inputs and Outputsfenixtec1Noch keine Bewertungen

- 74AC74Dokument9 Seiten74AC74ciernesNoch keine Bewertungen

- Octal Bus Transceiver With 3-State Outputs: FeaturesDokument24 SeitenOctal Bus Transceiver With 3-State Outputs: FeaturesLungoci AdrianNoch keine Bewertungen

- Distributed byDokument42 SeitenDistributed bydennyjoelNoch keine Bewertungen

- Nc7Sz373 Tinylogic Uhs D-Type Latch With 3-State Output: General Description FeaturesDokument9 SeitenNc7Sz373 Tinylogic Uhs D-Type Latch With 3-State Output: General Description Featuresgreentea601Noch keine Bewertungen

- CD4047Dokument15 SeitenCD4047mohankumarktvrNoch keine Bewertungen

- Datasheet SN74HC04 - Hex InversorDokument16 SeitenDatasheet SN74HC04 - Hex InversorPablo CarvalhoNoch keine Bewertungen

- 78 hct14Dokument16 Seiten78 hct14Bruno AlvesNoch keine Bewertungen

- CA3161EDokument4 SeitenCA3161EAlejandro Borrego DominguezNoch keine Bewertungen

- 8-Bit Serial-Input/Serial or Parallel-Output Shift Register With Latched 3-State OutputsDokument11 Seiten8-Bit Serial-Input/Serial or Parallel-Output Shift Register With Latched 3-State OutputsLưu TinhNoch keine Bewertungen

- HCTS245MS: Radiation Hardened Octal Bus Transceiver, Three-State, Non-InvertingDokument9 SeitenHCTS245MS: Radiation Hardened Octal Bus Transceiver, Three-State, Non-InvertingDeepa DevarajNoch keine Bewertungen

- SN74CBTS16211 24-Bit Fet Bus Switch With Schottky Diode ClampingDokument11 SeitenSN74CBTS16211 24-Bit Fet Bus Switch With Schottky Diode ClampingBa DuyNoch keine Bewertungen

- CD4047Dokument9 SeitenCD4047Haryadi VjNoch keine Bewertungen

- CD54/74HC688, CD54/74HCT688: Features DescriptionDokument6 SeitenCD54/74HC688, CD54/74HCT688: Features Descriptionbhavsar_vaibhavNoch keine Bewertungen

- 74ac11032 - OR PDFDokument10 Seiten74ac11032 - OR PDFgiuliano alvesNoch keine Bewertungen

- MC74ACT564 Octal D Type Flip Flop With 3 State Outputs: PDIP 20 N Suffix CASE 738Dokument8 SeitenMC74ACT564 Octal D Type Flip Flop With 3 State Outputs: PDIP 20 N Suffix CASE 738greentea601Noch keine Bewertungen

- 74HC03 74HCT03: 1. General DescriptionDokument16 Seiten74HC03 74HCT03: 1. General DescriptionDistribuidorIBoolPedregalDeSantoDomingoNoch keine Bewertungen

- CLAA150XP01QDokument21 SeitenCLAA150XP01QSergio Alvarez BarajasNoch keine Bewertungen

- Ultra Small Temperature Switches With Pin Selectable HysteresisDokument17 SeitenUltra Small Temperature Switches With Pin Selectable HysteresisBala SubramaniamNoch keine Bewertungen

- CD 74 HCT 164 MDokument16 SeitenCD 74 HCT 164 MfabriziocasNoch keine Bewertungen

- Quadruple Bus Buffer Gate With 3-State Outputs: FeaturesDokument20 SeitenQuadruple Bus Buffer Gate With 3-State Outputs: FeaturesEngine Tuning UpNoch keine Bewertungen

- D D D D D: SN74CBT3126 Quadruple Fet Bus SwitchDokument4 SeitenD D D D D: SN74CBT3126 Quadruple Fet Bus SwitchRicky CoxNoch keine Bewertungen

- 74AHC1G02 74AHCT1G02: 1. General DescriptionDokument11 Seiten74AHC1G02 74AHCT1G02: 1. General DescriptionMarcu Andrei StefanNoch keine Bewertungen

- CD4047BC Low Power Monostable/Astable Multivibrator: General DescriptionDokument10 SeitenCD4047BC Low Power Monostable/Astable Multivibrator: General DescriptionWillianNoch keine Bewertungen

- Dual D-Type Flip-Flop: Integrated CircuitsDokument8 SeitenDual D-Type Flip-Flop: Integrated CircuitsRakesh Kumar DNoch keine Bewertungen

- C.I 74HC365Dokument7 SeitenC.I 74HC365DOMINGOS ALADIRNoch keine Bewertungen

- 7Z08Dokument7 Seiten7Z08André Frota PaivaNoch keine Bewertungen

- Driver Mosfet TC4425Dokument18 SeitenDriver Mosfet TC4425jaimeNoch keine Bewertungen

- Cmos Sram K6T1008C2E Family: Document TitleDokument11 SeitenCmos Sram K6T1008C2E Family: Document TitleOmar LeonNoch keine Bewertungen

- 74AHC1G86 74AHCT1G86: 1. General DescriptionDokument12 Seiten74AHC1G86 74AHCT1G86: 1. General DescriptionKushalSwamyNoch keine Bewertungen

- Synchronous Presettable 4-Bit Counter: M B Order CodesDokument12 SeitenSynchronous Presettable 4-Bit Counter: M B Order CodesMarimuthu RajNoch keine Bewertungen

- 74 HC 4538Dokument11 Seiten74 HC 4538vagitusNoch keine Bewertungen

- Ic-Cmos-4008 UNTUK DECODER PDFDokument9 SeitenIc-Cmos-4008 UNTUK DECODER PDFBenny PadlyNoch keine Bewertungen

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsVon EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNoch keine Bewertungen

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Noch keine Bewertungen

- Beginning Digital Electronics through ProjectsVon EverandBeginning Digital Electronics through ProjectsBewertung: 5 von 5 Sternen5/5 (1)

- CAT28C16A 16 KB CMOS Parallel Eeprom: DescriptionDokument11 SeitenCAT28C16A 16 KB CMOS Parallel Eeprom: DescriptionLaboratorio GTO Perú S.A.C.Noch keine Bewertungen

- Datasheet Digital 74hcDokument10 SeitenDatasheet Digital 74hcСтанислав ИвановNoch keine Bewertungen

- BRAUTOPRDCTMAPDokument2 SeitenBRAUTOPRDCTMAPChris AbramowiczNoch keine Bewertungen

- CD4007Dokument8 SeitenCD4007renegonzalesvasquezNoch keine Bewertungen

- GSM Based Home AutomationDokument80 SeitenGSM Based Home AutomationShashi Kant SainiNoch keine Bewertungen

- bq30z554 r1Dokument29 Seitenbq30z554 r1tinel1968Noch keine Bewertungen

- 450 Μa, 5 Mhz Rail-To-Rail Op Amp: Features DescriptionDokument32 Seiten450 Μa, 5 Mhz Rail-To-Rail Op Amp: Features DescriptionYusuf UçkunNoch keine Bewertungen

- TC4426 TC4427 TC4428 1.5A Dual High-Speed Power Mosfet DriversDokument9 SeitenTC4426 TC4427 TC4428 1.5A Dual High-Speed Power Mosfet DriversroozbehxoxNoch keine Bewertungen

- Mpxh6400a 185587Dokument12 SeitenMpxh6400a 185587TDFRIOGRANDENoch keine Bewertungen

- 256-Kbit (32 K × 8) F-RAM Memory: FeaturesDokument21 Seiten256-Kbit (32 K × 8) F-RAM Memory: FeaturesAnonymous QlZYEDRHNoch keine Bewertungen

- LX6503Dokument2 SeitenLX6503Manori Liyanage100% (3)

- cd4013b PDFDokument28 Seitencd4013b PDFEasy Renewable Pvt LtdNoch keine Bewertungen

- QX Series System Software User GuideDokument406 SeitenQX Series System Software User GuidePaulo PereiraNoch keine Bewertungen

- HI-8421, HI-8424: 6-Channel / 8-Channel Discrete-to-Digital Interface Sensing 28V / Open SignalsDokument5 SeitenHI-8421, HI-8424: 6-Channel / 8-Channel Discrete-to-Digital Interface Sensing 28V / Open SignalsAnonymous 3mJfZENoch keine Bewertungen

- D D D D D D D: SN54HC541, SN74HC541 Octal Buffers and Line Drivers With 3-State OutputsDokument13 SeitenD D D D D D D: SN54HC541, SN74HC541 Octal Buffers and Line Drivers With 3-State OutputsdarkenelNoch keine Bewertungen

- 74HCT74 PDFDokument7 Seiten74HCT74 PDFDeni KhanNoch keine Bewertungen

- 64K (8Kx8) Parallel EEPROM With Page Write and Software Data Protection AT28C64BDokument21 Seiten64K (8Kx8) Parallel EEPROM With Page Write and Software Data Protection AT28C64BRoberto Kaled Silva ValdiviaNoch keine Bewertungen

- Opa 4990Dokument83 SeitenOpa 4990VIVEK THOMAS CHACKONoch keine Bewertungen

- Ucc 1801Dokument55 SeitenUcc 1801AriNeto100% (1)

- CD54/74HC688, CD54/74HCT688: Features DescriptionDokument6 SeitenCD54/74HC688, CD54/74HCT688: Features Descriptionbhavsar_vaibhavNoch keine Bewertungen

- 18CV8 EtcDokument10 Seiten18CV8 EtcAdriancito ZavalaNoch keine Bewertungen

- 74C922Dokument18 Seiten74C922Gunnar GodaraNoch keine Bewertungen

- Tpic 6 C 595Dokument30 SeitenTpic 6 C 595Edzio StreamNoch keine Bewertungen

- 74AHC04 74AHCT04: 1. General DescriptionDokument17 Seiten74AHC04 74AHCT04: 1. General DescriptionalexNoch keine Bewertungen

- How T Design and Built Working Electronic CircuitsDokument53 SeitenHow T Design and Built Working Electronic CircuitsfaisalshaikhthedeepNoch keine Bewertungen

- Fairchild Logic Selection GuideDokument12 SeitenFairchild Logic Selection Guidenapoleon_velasc3617Noch keine Bewertungen

- JC210SP Chinese AM-FM IC Radio Kit Construction: BackgroundDokument3 SeitenJC210SP Chinese AM-FM IC Radio Kit Construction: BackgroundantonioNoch keine Bewertungen

- X28HC256Dokument25 SeitenX28HC256schwagerino100% (1)

- TC4423/TC4424/TC4425: 3A Dual High-Speed Power MOSFET DriversDokument19 SeitenTC4423/TC4424/TC4425: 3A Dual High-Speed Power MOSFET DriversRodrigo TorresNoch keine Bewertungen

- Datasheet Lv04aDokument16 SeitenDatasheet Lv04aHeriberto Flores AmpieNoch keine Bewertungen