Beruflich Dokumente

Kultur Dokumente

Five Port NOC

Hochgeladen von

Anonymous VASS3z0wTHOriginalbeschreibung:

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Five Port NOC

Hochgeladen von

Anonymous VASS3z0wTHCopyright:

Verfügbare Formate

Five Port Router for Network on Chip

Swati Malviya (M.Tech. -Digital Communication) Anurag Jaiswal (Capgemini Consulting India Pvt. Ltd., Former HOD-IT, FMS, MITS University) mcms_anurag@rediff.com, swati_malviya4@yahoo.co.in Abstract Multiprocessor system on chip is emerging as a new trend for System on chip design but the wire and power design constraints are forcing adoption of new design methodologies. Researchers pursued a scalable solution to this problem i.e. Network on Chip (NOC). Network on chip architecture better supports the integration of SOC consists of on chip packet switched network. Thus the idea is borrowed from large scale multiprocessors and wide area network domain and envisions on chip routers based network. Cores access the network by means of proper interfaces and have their packets forwarded to destination through multihop routing path. In order to implement a competitive NOC architecture, the router should be efficiently design as it is the central component of NOC architecture. In this paper we implement a parallel router which can support five requests simultaneously. Thus the speed of communication can be increased after reducing communication bottleneck by using simplest routing mechanism, flow mechanism and decoding logic.

1.

Introduction

System on chip is a complex interconnection of various functional elements. It creates communication bottleneck in the gigabit communication due to its bus based architecture. Thus there was need of system that explicits modularity and parallelism, network on chip possess many such attractive properties and solve the problem of communication bottleneck. It basically works on the idea of interconnection of cores using on chip network. The communication on network on chip is carried out by means of router, so for implementing better NOC , the router should be efficiently design. This router supports five parallel connections at the same time. It uses store and forward type of flow control and XY deterministic routing which improves the performance of router. The switching mechanism used here is packet switching which is generally used on network on chip. In packet switching the data the data transfers in the form of packets between cooperating routers and independent routing decision is taken. The store and forward flow mechanism is best because it does not reserve channels and thus does not lead to idle physical channels. The routing used here is XY routing due to its simplicity and low overhead. The arbiter is of rotating priority scheme so that every channel once get chance to transfer its data. In this router both input and output buffering is used so that congestion can be avoided at both sides. 2. Background The router used here is it avoid congestion and communication bottleneck. Although there are number of router implementation has already been done. Some of the related works are included here. Marescaux presented the implementation of router for NOC based system which has 2D torus network toplogy, XY blocking and deterministic routing. Packet size was 16 bits and 3 control bits. The main drawback here was it was a 2D torus formed using 1D router which creates a serious bottleneck in traffic. Zerferino presented a soft core router for NOC, the problem with this router implementation was it uses 4 flit

104

buffer having 8 bit implementation which is quite high. Its input and output channel has four distinct blocks and uses a large decoding logic. Moraes also presented its work but the drawback with it was that its packet has two headers which is quite expensive. The buffer here is present only with input channel. The absence of output buffer creates a serious problem in the implementation of router as it increases the problem of congestion. Our paper removes most of the problems cited above and improves the performance of router. 3. Design The router consists of five ports east, west, north, south and local port and a central crosspoint matrix. Each port has its input channel and output channel. Data packet moves in to the input channel of one port of router by which it is forwarded to the output channel of other port. Each input channel and output channel has its own decoding logic which increases the performance of the router. Buffers are present at all ports to store the data temporarily. The buffering method used here is store and forward. Control logic is present to make arbitration decisions. Thus communication is established between input and output ports. The connection or configuration is made between both with the central crosspoint matrix. According to the destination path of data packet, control bit lines of crosspoint matrix are set. The movement of data from source to destination is called switching mechanism. The packet switching mechanism is used here, in which the flit size is 8 bits .Thus the packet size varies from 8 bits to 120 bits. A detailed explanation of Design is as follows.

Figure 1 Router Architecture a. Input Channel: There is one input channel at each port and each has its control and decoding logic. It consists of main three parts i.e. FIFO, FSM, XY logic. FIFO is used as input buffer to store the data temporarily. The size of FIFO is 8 bits and depth is of 16 bits. The first 8 bits are the header which consists of coordinates of destination path. In this way the size of packet varies from 8 bits to 120 bits. The status of FIFO decides the communication can start

105

or not. If the FIFO is empty the data can be written in it and communication can start .If FIFO is full, data can be read or can be forwarded to its destination router. Inside the router Grant /acknowledgement signals are used to access the FIFO .The read and write operation of FIFO is controlled by FSM. FSM controls the read and write operation of FIFO according to its status. If FIFO is empty and having space to store the data, FSM will generate acknowledgement signal in respect to the request coming to input channel, thus write operation starts. If FIFO is full or not having space to store the data, the write operation stops and the acknowledgement signal goes low. When the FIFO is full, FSM will send request to output channel of other port, if grant signal is received by it then read operation starts and continues until grant signal goes low or FIFO empties. Thus empty status of indicates the end of communication. XY logic is the deterministic logic which analyses the header of data and send it to its destination port. The first four bits of the header are the coordinates of destination port. In XY logic a comparator is used which compares the header of the data to the locally stored X and Y coordinate and send the packet according to its destination address. Let the coordinates stored in header be Hx and Hy and locally stored coordinates be X and Y. So according to XY logic if Hx >X then packet will move to east port otherwise move to west port. If Hx=X then Y coordinate is compared, If Hy >Y then packet will move to north port otherwise move to south port, when Hy=Y then packet will move to local port. Thus in this way XY logic will send the packet to the output channel of its destination port.

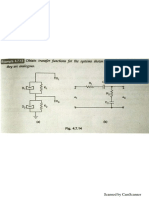

Figure 2 Input Channel b. Output Channel Each port of the router contains one output channel which has its control and decoding logic. It also consists of three parts i.e. FIFO, FSM and arbiter. FIFO and FSM are same as in input channel but in place of XY logic, arbiter is used in output channel. FIFO in output channels used as output buffer to store the data temporarily. FIFO is of size 8 bits and is of depth 16 bits. The first 8 bits are the header which is the coordinates of destination router. Thus size of packet varies from 8 bits to 120 bits. The status of FIFO decides the communication can start or not. If the FIFO is empty the data can be write and communication can start. If FIFO is full, data can be read or can be forwarded to its destination router. Inside the router the Grant/Acknowledgement signals are used to access the FIFO. The read and write operation of FIFO is controlled by FSM. FSM controls the read and write operation of FIFO according to its status. If FIFO is empty or having enough space to store the data, FSM will give acknowledgement signal in respect to the request

106

coming from input channel, thus write operation starts. If FIFO is full or not having enough space to store the data, write operation terminates and the acknowledgement signal goes low. When FIFO is full, FSM will send request to other router, if grant signal is received by it, then read operation starts and continues until grant goes low or FIFO empties. Arbiter is used in output channel in place of XY logic in input channel. Arbiter is used to solve the problem of multiple requests coming at single output port. When there are more than one request coming from one input channels to a single output channel, arbiter selects one of the request and serve it. Arbiter is used in rotating priority scheme in which east has highest priority, then west, north, south and then local port. As it is rotating priority scheme, the priority of port reduces once it has been served. Thus this sheme increases the performance of router as each port gets chance to send its data.

Figure 3 Output Channel c. Crosspoint Matrix

Crosspoint matrix is the important and central component of router. It consists of various multiplexers and demultiplexers and interconnection of all 5 input channels and 5 output channel. It allows all five connections at the same time by configuring input and output channel. The control of crosspoint matrix is under output channel as while granting the request of any input channel, output channel configures the multiplexers and demultiplexers of it. Since each input channel has FSM and XY logic and each output channel has its FSM and arbiter, there is no time lag in making the connection and all five requests can be granted at the same time simultaneously, which increases the performance of the router.

107

Figure 4 Crossbar Switch 4. Conclusion Here we have proposed the router which supports five connections at the same time without any communication bottleneck. We have used simplest decoding logic, store and forward flow mechanism, packet switching, XY deterministic routing, input and output buffering which increases the performance of router. In future we intend to build advanced router prototype supporting high level protocol(HLP)having flit size of 16 bits and all 8 bits of header to be used. 5. References 1. D.M. Chapiro Globally Asynchronous Locally Synchronous Systems. PhD thesis, 1984. 2. W. J. Dally and B. Towles. Route Packets, Not Wires: On-Chip Interconnection Networks. In Design Automation Conference, pages 684689, 2001. 3. J. Duato and L. Ni S. Yalamanchili. Interconnect Networks: An Engineering Approach. In IEEE CS Press, 1998. 4. Fernando Moraes et. al. A Low Area Overhead Packet-switched Network On Chip: 5. Architecture and Prototyping. In IFIP VLSI-SOC 2003, pages 318323, 2003. 6. S. Kumar et al. A Network on Chip Architecture and Design Methodology. In Annual Symposium on VLSI2002, IEEE CS Press, pages 105112, 2002. 7. T.A. Bartic et al. Highly Scalable Network on Chip for Reconfigurable Systems. In Proceedings of the International Conference on System-On-Chip 2003, pages 7982, Nov. 2003. 8. Theodore Marescaux et. al. Interconnection Networks Enable Fine-Grain Dynamic MultiTasking on FPGAs. In FPL2002, pages 795805, September 2002.

108

9. Nikolay Kavaldjiev and Gerard J.M. Smit. A survey of efficient on-chip communications for SoC. In PROGRESS 2003 Embedded Systems Symposium, October 2003. 10. International Sematech. International Technology Roadmap for Semiconductors - 2002 Update. In http://public.itrs.net, 2002. 11. Xilinx Inc. http://www.xilinx.com, 2004. 12. C.A. Zerferino, M.E. Kreutz, and A.A. Susin. RASoC: A Router Soft-Core for Networks-onChip. In DATE2004-Designers Forum. IEEE CS Press, 2004. 13. C.A. Zerferino and A.A. Susin. SoCIN: A Parametric and Scalable Network on Chip. In SBCCI2003, pages 169174.IEEE CS Press, 2003.

109

Das könnte Ihnen auch gefallen

- Design and Verification8Dokument5 SeitenDesign and Verification8SamNoch keine Bewertungen

- Traffic Control SystemDokument3 SeitenTraffic Control SystemSandhya DeviNoch keine Bewertungen

- Projectreport ForwardingDokument12 SeitenProjectreport ForwardingAbhishekKoneruNoch keine Bewertungen

- Router 1X3 - RTL Design and VerificationDokument10 SeitenRouter 1X3 - RTL Design and VerificationIJERDNoch keine Bewertungen

- Implementation of A Multi-Channel UART Controller Based On FIFO Technique and FPGADokument5 SeitenImplementation of A Multi-Channel UART Controller Based On FIFO Technique and FPGAJNRNoch keine Bewertungen

- Operation of Pci BusDokument7 SeitenOperation of Pci BusRohini JosephNoch keine Bewertungen

- Project PresentationDokument17 SeitenProject PresentationKhevana PurohitNoch keine Bewertungen

- Lab-02 (R&S)Dokument4 SeitenLab-02 (R&S)Amjad hassanNoch keine Bewertungen

- Unit 7 NotesDokument15 SeitenUnit 7 NotesDiponegoro Muhammad KhanNoch keine Bewertungen

- S O N (Sonet) : Ynchronous Ptical EtworkDokument18 SeitenS O N (Sonet) : Ynchronous Ptical EtworkKarthikRam KvNoch keine Bewertungen

- IEEE Standards4Dokument29 SeitenIEEE Standards4Ruchi AgrawalNoch keine Bewertungen

- Automotive Interview QuestionsDokument61 SeitenAutomotive Interview Questionskrajasekarantuti50% (2)

- Routing Protocols CTDokument70 SeitenRouting Protocols CTgaurav_juneja_4Noch keine Bewertungen

- Study Material Subject: Microprocessor and Microcontroller V Semester Electronics by Prof. Mrs. J. S. GawaiDokument25 SeitenStudy Material Subject: Microprocessor and Microcontroller V Semester Electronics by Prof. Mrs. J. S. GawaidukeNoch keine Bewertungen

- CN Unit Iv QBSDokument17 SeitenCN Unit Iv QBS82Neha PalNoch keine Bewertungen

- 20.verification of Four Port Router For Network On Chip (Noc)Dokument5 Seiten20.verification of Four Port Router For Network On Chip (Noc)vijaykannamallaNoch keine Bewertungen

- Home Agent (HA) :: Chapter - 1 1. What Is TTL in IP Header?Dokument9 SeitenHome Agent (HA) :: Chapter - 1 1. What Is TTL in IP Header?Group ThreeNoch keine Bewertungen

- Open Access: High Throughput Compact Delay Insensitive Asynchronous NOC RouterDokument3 SeitenOpen Access: High Throughput Compact Delay Insensitive Asynchronous NOC RouterAshok Siva Kumar PoojalaNoch keine Bewertungen

- Otherwise Do The Extra Configurations: Static RoutingDokument3 SeitenOtherwise Do The Extra Configurations: Static RoutingThushara Chaminda DassanayakeNoch keine Bewertungen

- DCN Unit VDokument6 SeitenDCN Unit VNexusNoch keine Bewertungen

- Serial InterfaceDokument19 SeitenSerial InterfaceHafizNoch keine Bewertungen

- Understand Open Shortest Path First (OSPF) - Design Guide - CiscoDokument117 SeitenUnderstand Open Shortest Path First (OSPF) - Design Guide - Ciscojaymalaviya48Noch keine Bewertungen

- Data TransmissionDokument15 SeitenData TransmissionLemar C. ManarpaacNoch keine Bewertungen

- Asghari CsiDokument6 SeitenAsghari CsiMarwan AhmedNoch keine Bewertungen

- OSFP Intro and ConfigurationDokument63 SeitenOSFP Intro and Configurationathartanveer31Noch keine Bewertungen

- Telecommunication Networks 15B11EC611: Dr. Bhagirath Sahu Assistant Professor, JIIT, NoidaDokument29 SeitenTelecommunication Networks 15B11EC611: Dr. Bhagirath Sahu Assistant Professor, JIIT, NoidaMOHAMMED FAYEZ KHANNoch keine Bewertungen

- CN-Unit-1 - Part2 NotesDokument9 SeitenCN-Unit-1 - Part2 NotesMeghnadhNoch keine Bewertungen

- Lecture #5 THRDokument45 SeitenLecture #5 THRZainab ShahzadNoch keine Bewertungen

- Unit III Day 1Dokument22 SeitenUnit III Day 1Pavan ParthikNoch keine Bewertungen

- z-IP OVER SONETDokument10 Seitenz-IP OVER SONETSurangma ParasharNoch keine Bewertungen

- Router1X3 RTLDesignandVerificationDokument11 SeitenRouter1X3 RTLDesignandVerificationSudeep KrishnappaNoch keine Bewertungen

- Internet Protocol RoutingDokument6 SeitenInternet Protocol RoutingAnmol ChitranshNoch keine Bewertungen

- CCN VivaDokument6 SeitenCCN VivaPurvaNoch keine Bewertungen

- Chap 5Dokument16 SeitenChap 5Ravi Raj DNoch keine Bewertungen

- Ethernet Frame FormatDokument4 SeitenEthernet Frame FormatSwapnil Sunil ShendageNoch keine Bewertungen

- IPv4 HeaderDokument18 SeitenIPv4 Headerjsk244807Noch keine Bewertungen

- Can Interview Questions: 1. What Is CAN and Its Uses? Answer: 1. CAN Is A Multi-Master Broadcast Serial Bus Standard ForDokument90 SeitenCan Interview Questions: 1. What Is CAN and Its Uses? Answer: 1. CAN Is A Multi-Master Broadcast Serial Bus Standard ForsidduNoch keine Bewertungen

- Hello, and Welcome To This Presentation of The STM32 Serial Peripheral InterfaceDokument31 SeitenHello, and Welcome To This Presentation of The STM32 Serial Peripheral InterfacelinkskilNoch keine Bewertungen

- Chapter 4-2Dokument71 SeitenChapter 4-2ajitsah110920Noch keine Bewertungen

- Unit-1 (Part 1) PDFDokument36 SeitenUnit-1 (Part 1) PDFPranjal NagarNoch keine Bewertungen

- It 1Dokument48 SeitenIt 1mitalisgawadeNoch keine Bewertungen

- LAN and Ethernet Basics - Deepak George: OSI Network LayersDokument12 SeitenLAN and Ethernet Basics - Deepak George: OSI Network LayersUseful Videos DevotionalNoch keine Bewertungen

- Network Layer - IP - MukeshDokument19 SeitenNetwork Layer - IP - MukeshMukesh100% (2)

- 3rd Module CN NotesDokument57 Seiten3rd Module CN NotesChandan SubramanyaNoch keine Bewertungen

- Hello, and Welcome To This Presentation of The STM32 Serial Peripheral InterfaceDokument27 SeitenHello, and Welcome To This Presentation of The STM32 Serial Peripheral Interfacecansu100% (1)

- Computer Organization & Architecture Lecture #15 A View of Computer Function and Interconnection Interconnections StructuresDokument12 SeitenComputer Organization & Architecture Lecture #15 A View of Computer Function and Interconnection Interconnections Structuresavdheshg_1Noch keine Bewertungen

- Practical 4Dokument6 SeitenPractical 4Louis StephenNoch keine Bewertungen

- 1.A. Sonet Frame 1.B. Atm Cell 1.C. Ip Packet 1.D. Fiber Channel FrameDokument17 Seiten1.A. Sonet Frame 1.B. Atm Cell 1.C. Ip Packet 1.D. Fiber Channel Frameరాహుల్ దేవ్Noch keine Bewertungen

- Ijert Ijert: Implementation of Interleaving Switch Based Architecture For System On ChipDokument7 SeitenIjert Ijert: Implementation of Interleaving Switch Based Architecture For System On ChipAkhila ReddyNoch keine Bewertungen

- Documents - Pub Hyper Transport Technology 5584a1e483247Dokument26 SeitenDocuments - Pub Hyper Transport Technology 5584a1e483247shaheen sayyad 463Noch keine Bewertungen

- Ответы Unit 1. Lesson 5. Static vs dynamic rDokument3 SeitenОтветы Unit 1. Lesson 5. Static vs dynamic rМакс КальмусNoch keine Bewertungen

- Chapter 4 ACNDokument20 SeitenChapter 4 ACNcdhvvgybfNoch keine Bewertungen

- Group - 4 Advanced Network AssignmentDokument12 SeitenGroup - 4 Advanced Network AssignmentANTENEHNoch keine Bewertungen

- Es IiiDokument12 SeitenEs IiiGopinathan MNoch keine Bewertungen

- Forouzan Sol 20Dokument4 SeitenForouzan Sol 20Anurag UpadhyayNoch keine Bewertungen

- Unit 6 MCDokument44 SeitenUnit 6 MCkaustubhNoch keine Bewertungen

- OTN Framer Project BookDokument54 SeitenOTN Framer Project Bookfrancisco moralesNoch keine Bewertungen

- Parallel Communication Interface & StandardsDokument17 SeitenParallel Communication Interface & StandardsKunal DeshmukhNoch keine Bewertungen

- 14 FpgaDokument11 Seiten14 FpgaHayatun NufusNoch keine Bewertungen

- Compliments RulesDokument3 SeitenCompliments RulesAnonymous VASS3z0wTHNoch keine Bewertungen

- Assignment1 Number System and Radix FormatDokument1 SeiteAssignment1 Number System and Radix FormatAnonymous VASS3z0wTHNoch keine Bewertungen

- FileDokument2 SeitenFileAnonymous VASS3z0wTHNoch keine Bewertungen

- Digital AssignmentDokument1 SeiteDigital AssignmentAnonymous VASS3z0wTHNoch keine Bewertungen

- EmtDokument13 SeitenEmtAnonymous VASS3z0wTHNoch keine Bewertungen

- Ses 3Dokument5 SeitenSes 3Anonymous VASS3z0wTHNoch keine Bewertungen

- Command HistoryDokument9 SeitenCommand HistoryAnonymous VASS3z0wTHNoch keine Bewertungen

- SFG1Dokument2 SeitenSFG1Anonymous VASS3z0wTHNoch keine Bewertungen

- Ses 4Dokument3 SeitenSes 4Anonymous VASS3z0wTHNoch keine Bewertungen

- Ses 2Dokument3 SeitenSes 2Anonymous VASS3z0wTHNoch keine Bewertungen

- Imp Unix CommandDokument4 SeitenImp Unix CommandAnonymous VASS3z0wTHNoch keine Bewertungen

- Ses 1Dokument4 SeitenSes 1Anonymous VASS3z0wTHNoch keine Bewertungen

- Ses 6Dokument3 SeitenSes 6Anonymous VASS3z0wTHNoch keine Bewertungen

- Scan 10 Sep 2020Dokument2 SeitenScan 10 Sep 2020Anonymous VASS3z0wTHNoch keine Bewertungen

- Elirections.: Clíscussi Depre30 Ntalions Ecto Form)Dokument3 SeitenElirections.: Clíscussi Depre30 Ntalions Ecto Form)Anonymous VASS3z0wTHNoch keine Bewertungen

- Module 3 2Dokument5 SeitenModule 3 2Anonymous VASS3z0wTHNoch keine Bewertungen

- Vishwanathrao Deshpande Institute of Technology, Haliyal: in Today'sDokument8 SeitenVishwanathrao Deshpande Institute of Technology, Haliyal: in Today'sAnonymous VASS3z0wTH100% (1)

- Ia 3QBDokument2 SeitenIa 3QBAnonymous VASS3z0wTHNoch keine Bewertungen

- Counseling Report ACADEMIC YEAR 2019-2020Dokument1 SeiteCounseling Report ACADEMIC YEAR 2019-2020Anonymous VASS3z0wTHNoch keine Bewertungen

- Module 3 1Dokument8 SeitenModule 3 1Anonymous VASS3z0wTHNoch keine Bewertungen

- VTU Eligibility Test For Research (VTU-ETR) Syllabii: Syllabus in MathematicsDokument3 SeitenVTU Eligibility Test For Research (VTU-ETR) Syllabii: Syllabus in MathematicsAnonymous VASS3z0wTHNoch keine Bewertungen

- Program SchedulesDokument1 SeiteProgram SchedulesAnonymous VASS3z0wTHNoch keine Bewertungen

- Counseling Report ACADEMIC YEAR 2018-2019Dokument1 SeiteCounseling Report ACADEMIC YEAR 2018-2019Anonymous VASS3z0wTHNoch keine Bewertungen

- NA Assignments 1 Source TransformationDokument2 SeitenNA Assignments 1 Source TransformationAnonymous VASS3z0wTHNoch keine Bewertungen

- Find Vo Using Nodal AnalysisDokument3 SeitenFind Vo Using Nodal AnalysisAnonymous VASS3z0wTHNoch keine Bewertungen

- Syllabus For Screening Test and Interviews: Research Topics (My Choice)Dokument2 SeitenSyllabus For Screening Test and Interviews: Research Topics (My Choice)Anonymous VASS3z0wTHNoch keine Bewertungen

- 3.2graph TheoryDokument1 Seite3.2graph TheoryAnonymous VASS3z0wTHNoch keine Bewertungen

- Course Plan Semester: Year: 2018-19: Vishwanathrao Deshpande Institute of Technology, HaliyalDokument7 SeitenCourse Plan Semester: Year: 2018-19: Vishwanathrao Deshpande Institute of Technology, HaliyalAnonymous VASS3z0wTHNoch keine Bewertungen

- Alternative Network Letter Vol 7 No.1-Apr 1991-EQUATIONSDokument16 SeitenAlternative Network Letter Vol 7 No.1-Apr 1991-EQUATIONSEquitable Tourism Options (EQUATIONS)Noch keine Bewertungen

- Soil NailingDokument6 SeitenSoil Nailingvinodreddy146Noch keine Bewertungen

- Asterisk NowDokument82 SeitenAsterisk Nowkambojk100% (1)

- A Medium-Rise Residential Building: A B C E D F G HDokument3 SeitenA Medium-Rise Residential Building: A B C E D F G HBabyjhaneTanItmanNoch keine Bewertungen

- The Wayland News October 2014Dokument16 SeitenThe Wayland News October 2014Julian HornNoch keine Bewertungen

- Jee MainsDokument32 SeitenJee Mainsjhaayushbhardwaj9632Noch keine Bewertungen

- Transportasi Distribusi MigasDokument25 SeitenTransportasi Distribusi MigasDian Permatasari100% (1)

- Intelligent DesignDokument21 SeitenIntelligent DesignDan W ReynoldsNoch keine Bewertungen

- Individual Career Plan: DIRECTIONS: Answer The Following Questions in Paragraph Form (3-4 Sentences) Per QuestionDokument2 SeitenIndividual Career Plan: DIRECTIONS: Answer The Following Questions in Paragraph Form (3-4 Sentences) Per Questionapi-526813290Noch keine Bewertungen

- Bandhan Neft Rtgs FormDokument2 SeitenBandhan Neft Rtgs FormMohit Goyal50% (4)

- Pantalla MTA 100Dokument84 SeitenPantalla MTA 100dariocontrolNoch keine Bewertungen

- Ci Thai RiceDokument4 SeitenCi Thai RiceMakkah Madina riceNoch keine Bewertungen

- Financial Management 2E: Rajiv Srivastava - Dr. Anil Misra Solutions To Numerical ProblemsDokument5 SeitenFinancial Management 2E: Rajiv Srivastava - Dr. Anil Misra Solutions To Numerical ProblemsParesh ShahNoch keine Bewertungen

- Math Review CompilationDokument9 SeitenMath Review CompilationJessa Laika CastardoNoch keine Bewertungen

- Syllabus PDFDokument3 SeitenSyllabus PDFBibin Raj B SNoch keine Bewertungen

- Futures Volume 1 Issue 3 1969 (Doi 10.1016/0016-3287 (69) 90026-3) Dennis Livingston - Science Fiction As A Source of Forecast MaterialDokument7 SeitenFutures Volume 1 Issue 3 1969 (Doi 10.1016/0016-3287 (69) 90026-3) Dennis Livingston - Science Fiction As A Source of Forecast MaterialManticora VenerabilisNoch keine Bewertungen

- MEd TG G07 EN 04-Oct Digital PDFDokument94 SeitenMEd TG G07 EN 04-Oct Digital PDFMadhan GanesanNoch keine Bewertungen

- Design and Analysis of Modified Front Double Wishbone Suspension For A Three Wheel Hybrid VehicleDokument4 SeitenDesign and Analysis of Modified Front Double Wishbone Suspension For A Three Wheel Hybrid VehicleRima AroraNoch keine Bewertungen

- Implications of A Distributed Environment Part 2Dokument38 SeitenImplications of A Distributed Environment Part 2Joel wakhunguNoch keine Bewertungen

- Semi Detailed Lesson PlanDokument2 SeitenSemi Detailed Lesson PlanJean-jean Dela Cruz CamatNoch keine Bewertungen

- Stone As A Building Material: LateriteDokument13 SeitenStone As A Building Material: LateriteSatyajeet ChavanNoch keine Bewertungen

- Decision Trees For Management of An Avulsed Permanent ToothDokument2 SeitenDecision Trees For Management of An Avulsed Permanent ToothAbhi ThakkarNoch keine Bewertungen

- Feasibility Study For Cowboy Cricket Farms Final Report: Prepared For Prospera Business Network Bozeman, MTDokument42 SeitenFeasibility Study For Cowboy Cricket Farms Final Report: Prepared For Prospera Business Network Bozeman, MTMyself IreneNoch keine Bewertungen

- Airport & Harbour Engg-AssignmentDokument3 SeitenAirport & Harbour Engg-AssignmentAshok Kumar RajanavarNoch keine Bewertungen

- When A Snobbish Gangster Meets A Pervert CassanovaDokument62 SeitenWhen A Snobbish Gangster Meets A Pervert CassanovaMaria Shiela Mae Baratas100% (1)

- BIAN How To Guide Developing Content V7.0 Final V1.0 PDFDokument72 SeitenBIAN How To Guide Developing Content V7.0 Final V1.0 PDFميلاد نوروزي رهبرNoch keine Bewertungen

- Cetie Guide No1 EngDokument55 SeitenCetie Guide No1 EngJose Manuel Sepulveda RomanNoch keine Bewertungen

- Ring and Johnson CounterDokument5 SeitenRing and Johnson CounterkrsekarNoch keine Bewertungen

- Ajmera - Treon - FF - R4 - 13-11-17 FinalDokument45 SeitenAjmera - Treon - FF - R4 - 13-11-17 FinalNikita KadamNoch keine Bewertungen

- Resume 1Dokument2 SeitenResume 1Aidie HerreraNoch keine Bewertungen

- iPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsVon EverandiPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsBewertung: 5 von 5 Sternen5/5 (4)

- Chip War: The Fight for the World's Most Critical TechnologyVon EverandChip War: The Fight for the World's Most Critical TechnologyBewertung: 4.5 von 5 Sternen4.5/5 (82)

- Chip War: The Quest to Dominate the World's Most Critical TechnologyVon EverandChip War: The Quest to Dominate the World's Most Critical TechnologyBewertung: 4.5 von 5 Sternen4.5/5 (229)

- CISSP All-in-One Exam Guide, Ninth EditionVon EverandCISSP All-in-One Exam Guide, Ninth EditionBewertung: 5 von 5 Sternen5/5 (1)

- Cyber-Physical Systems: Foundations, Principles and ApplicationsVon EverandCyber-Physical Systems: Foundations, Principles and ApplicationsHoubing H. SongNoch keine Bewertungen

- CompTIA A+ Certification All-in-One Exam Guide, Eleventh Edition (Exams 220-1101 & 220-1102)Von EverandCompTIA A+ Certification All-in-One Exam Guide, Eleventh Edition (Exams 220-1101 & 220-1102)Bewertung: 5 von 5 Sternen5/5 (2)

- Samsung Galaxy S22 Ultra User Guide For Beginners: The Complete User Manual For Getting Started And Mastering The Galaxy S22 Ultra Android PhoneVon EverandSamsung Galaxy S22 Ultra User Guide For Beginners: The Complete User Manual For Getting Started And Mastering The Galaxy S22 Ultra Android PhoneNoch keine Bewertungen

- CompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Von EverandCompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Bewertung: 5 von 5 Sternen5/5 (2)

- iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]Von EverandiPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]Bewertung: 5 von 5 Sternen5/5 (4)

- CompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002Von EverandCompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002Bewertung: 5 von 5 Sternen5/5 (1)

- CompTIA A+ Complete Practice Tests: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Von EverandCompTIA A+ Complete Practice Tests: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Noch keine Bewertungen

- iPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XVon EverandiPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XBewertung: 3 von 5 Sternen3/5 (2)

- Computer Science: A Concise IntroductionVon EverandComputer Science: A Concise IntroductionBewertung: 4.5 von 5 Sternen4.5/5 (14)

- Cancer and EMF Radiation: How to Protect Yourself from the Silent Carcinogen of ElectropollutionVon EverandCancer and EMF Radiation: How to Protect Yourself from the Silent Carcinogen of ElectropollutionBewertung: 5 von 5 Sternen5/5 (2)

- Jensen Huang's Nvidia: Processing the Mind of Artificial IntelligenceVon EverandJensen Huang's Nvidia: Processing the Mind of Artificial IntelligenceNoch keine Bewertungen

- Raspberry PI: Learn Rasberry Pi Programming the Easy Way, A Beginner Friendly User GuideVon EverandRaspberry PI: Learn Rasberry Pi Programming the Easy Way, A Beginner Friendly User GuideNoch keine Bewertungen

- Arduino and Raspberry Pi Sensor Projects for the Evil GeniusVon EverandArduino and Raspberry Pi Sensor Projects for the Evil GeniusNoch keine Bewertungen

- A Beginner's Guide To IPhone 14 Pro Max Mastering: The Comprehensive User Guide And Illustrated Owner's Manual With Tips And Advanced Tricks For New BeVon EverandA Beginner's Guide To IPhone 14 Pro Max Mastering: The Comprehensive User Guide And Illustrated Owner's Manual With Tips And Advanced Tricks For New BeNoch keine Bewertungen

- The comprehensive guide to build Raspberry Pi 5 RoboticsVon EverandThe comprehensive guide to build Raspberry Pi 5 RoboticsNoch keine Bewertungen

- iPhone Photography: A Ridiculously Simple Guide To Taking Photos With Your iPhoneVon EverandiPhone Photography: A Ridiculously Simple Guide To Taking Photos With Your iPhoneNoch keine Bewertungen

- Debugging Embedded and Real-Time Systems: The Art, Science, Technology, and Tools of Real-Time System DebuggingVon EverandDebugging Embedded and Real-Time Systems: The Art, Science, Technology, and Tools of Real-Time System DebuggingBewertung: 5 von 5 Sternen5/5 (1)

- The User's Directory of Computer NetworksVon EverandThe User's Directory of Computer NetworksTracy LaqueyNoch keine Bewertungen

![iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]](https://imgv2-2-f.scribdassets.com/img/audiobook_square_badge/728318688/198x198/f3385cbfef/1715431191?v=1)