Beruflich Dokumente

Kultur Dokumente

Adc0804 1

Hochgeladen von

Alex AndresOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Adc0804 1

Hochgeladen von

Alex AndresCopyright:

Verfügbare Formate

Philips Semiconductors Linear Products

Product specification

CMOS 8-bit A/D converters

ADC0803/4-1

DESCRIPTION

The ADC0803 family is a series of three CMOS 8-bit successive approximation A/D converters using a resistive ladder and capacitive array together with an auto-zero comparator. These converters are designed to operate with microprocessor-controlled buses using a minimum of external circuitry. The 3-State output data lines can be connected directly to the data bus. The differential analog voltage input allows for increased common-mode rejection and provides a means to adjust the zero-scale offset. Additionally, the voltage reference input provides a means of encoding small analog voltages to the full 8 bits of resolution.

PIN CONFIGURATION

D1, N PACKAGES CS 1 RD 2 WR 3 CLK IN 4 20 VCC 19 CLK R 18 D0 17 D1 16 D2 15 D3 14 D4 13 D5 12 D6 11 D7

INTR 5 VIN(+) 6 VIN() 7 A GND 8

FEATURES

VREF/2 9 D GND 10 TOP VIEW NOTE: SOL Released in large SO package only.

Compatible with most microprocessors Differential inputs 3-State outputs Logic levels TTL and MOS compatible Can be used with internal or external clock Analog input range 0V to VCC Single 5V supply Guaranteed specification with 1MHz clock

APPLICATIONS

Transducer-to-microprocessor interface Digital thermometer Digitally-controlled thermostat Microprocessor-based monitoring and control systems

ORDERING INFORMATION

DESCRIPTION 20-Pin Plastic Dual In-Line Package (DIP) 20-Pin Plastic Dual In-Line Package (DIP) 20-Pin Plastic Small Outline (SO) Package 20-Pin Plastic Small Outline (SO) Package TEMPERATURE RANGE -40 to +85C 0 to 70C 0 to 70C -40 to 85C ORDER CODE ADC0803/04-1 LCN ADC0803/04-1 CN ADC0803/04-1 CD ADC0803/04-1 LCD DWG # 0408B 0408B 1021B 1021B

ABSOLUTE MAXIMUM RATINGS

SYMBOL VCC Supply voltage Logic control input voltages All other input voltages TA Operating temperature range ADC0803/04-1 LCD ADC0803/04-1 LCN ADC0803/04-1 CD ADC0803/04-1 CN TSTG TSOLD PD Storage temperature Lead soldering temperature (10 seconds) Maximum power dissipation TA=25C (still air)1 N package D package NOTES: 1. Derate above 25C, at the following rates: N package at 13.5mW/C; D package at 11.1mW/C 1690 1390 mW mW -40 to +85 -40 to +85 0 to +70 0 to +70 -65 to +150 300 C C C C C C PARAMETER RATING 6.5 -0.3 to +16 -0.3 to (VCC +0.3) UNIT V V V

August 31, 1994

555

853-0034 13721

Philips Semiconductors Linear Products

Product specification

CMOS 8-bit A/D converters

ADC0803/4-1

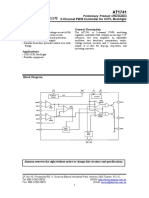

BLOCK DIAGRAM

VIN (+) 6 VIN () 7

9

VREF/2 LADDER AND DECODER

8 A GND

AUTO ZERO COMPARATOR

VCC

20

D7 (MSB) (11) D6 D5 D4 D3 D2 D1 D0 (LSB) (12) (13) (14) (15) (16) (17) (18)

OUTPUT LATCHES SAR 10 D GND LE OE

3 WR 8BIT SHIFT REGISTER CLOCK

1 CS S INTR FF R 2 RD Q

5 INTR

4 CLK IN

19 CLK R

August 31, 1994

556

Philips Semiconductors Linear Products

Product specification

CMOS 8-bit A/D converters

ADC0803/4-1

DC ELECTRICAL CHARACTERISTICS

VCC = 5.0V, fCLK = 1MHz, TMIN TA TMAX, unless otherwise specified. SYMBOL PARAMETER ADC0803 relative accuracy error (adjusted) ADC0804 relative accuracy error (unadjusted) RIN VREF/2 input resistance3 Analog input voltage range3 DC common-mode error Power supply sensitivity Control inputs VIH VIL IIH IIL VT+ VT VH VOL VOH VOL Logical 1 input voltage Logical 0 input voltage Logical 1 input current Logical 0 input current VCC = 5.25VDC VCC = 4.75VDC VIN = 5VDC VIN = 0VDC 1 0.005 0.005 2.0 15 0.8 1 VDC VDC ADC ADC 3.5 2.1 2.0 0.4 2.4 VDC VDC VDC VDC VDC Over analog input voltage range VCC = 5V 10%1 TEST CONDITIONS Full-Scale adjusted VREF/2 = 2.500VDC VCC = 0V2 400 0.05 1/16 1/16 680 VCC+0.05 1/8 ADC0803/4 Min Typ Max 0.50 1 UNIT LSB LSB V LSB LSB

Clock in and clock R Clock in positive-going threshold voltage Clock in negative-going threshold voltage Clock in hysteresis (VT+)(VT) Logical 0 clock R output voltage Logical 1 clock R output voltage IOL = 360A, VCC = 4.75VDC IOH = 360A, VCC = 4.75VDC 2.7 1.5 0.6 3.1 1.8 1.3

Data output and INTR Logical 0 output voltage Data outputs INTR outputs VOH IOZL IOZH ISC ISC ICC Logical 1 output voltage 3-state output leakage 3-state output leakage +Output short-circuit current Output short-circuit current Power supply current IOL = 1.6mA, VCC = 4.75VDC IOL = 1.0mA, VCC = 4.75VDC IOH = 360A, VCC = 4.75VDC IOH = 10A, VCC = 4.75VDC VOUT = 0VDC, CS = logical 1 VOUT = 5VDC, CS = logical 1 VOUT = 0V, TA = 25C VOUT = VCC, TA = 25C fCLK = 1MHz, VREF/2 = OPEN, CS = Logical 1, TA = 25C 4.5 9.0 12 30 3.0 3.5 2.4 4.5 3 3 0.4 0.4 VDC VDC VDC ADC ADC mADC mADC mA

NOTES: 1. Analog inputs must remain within the range: 0.05 VIN VCC + 0.05V. 2. See typical performance characteristics for input resistance at VCC = 5V. 3. VREF/2 and VIN must be applied after the VCC has been turned on to prevent the possibility of latching.

August 31, 1994

557

Philips Semiconductors Linear Products

Product specification

CMOS 8-bit A/D converters

ADC0803/4-1

AC ELECTRICAL CHARACTERISTICS

SYMBOL PARAMETER Conversion time fCLK Clock frequency1 Clock duty cycle1 CR tW(WR)L tACC t1H, t0H tW1, tR1 CIN COUT Free-running conversion rate Start pulse width Access time 3-State control INTR delay Logic input=capacitance 3-State output capacitance Output Output INTR RD RD WD or RD CS=0, fCLK=1MHz INTR tied to WR CS=0 CS=0, CL=100pF CL=10pF, RL=10k See 3-State test circuit 30 75 70 100 5 5 100 100 150 7.5 7.5 TO FROM TEST CONDITIONS fCLK=1MHz1 ADC0803/4 Min 66 0.1 40 1.0 Typ Max 73 3.0 60 13690 UNIT s MHz % conv/s ns ns ns ns pF pF

NOTES: 1. Accuracy is guaranteed at fCLK=1MHz. Accuracy may degrade at higher clock frequencies.

FUNCTIONAL DESCRIPTION

These devices operate on the Successive Approximation principle. Analog switches are closed sequentially by successive approximation logic until the input to the auto-zero comparator [ VIN(+)-VIN(-) ] matches the voltage from the decoder. After all bits are tested and determined, the 8-bit binary code corresponding to the input voltage is transferred to an output latch. Conversion begins with the arrival of a pulse at the WR input if the CS input is low. On the High-to-Low transition of the signal at the WR or the CS input, the SAR is initialized, the shift register is reset, and the INTR output is set high. The A/D will remain in the reset state as long as the CS and WR inputs remain low. Conversion will start from one to eight clock periods after one or both of these inputs makes a Low-to-High transition. After the conversion is complete, the INTR pin will make a High-to-Low transition. This can be used to interrupt a processor, or otherwise signal the availability of a new conversion result. A read (RD) operation (with CS low) will clear the INTR line and enable the output latches. The device may be run in the free-running mode as described later. A conversion in progress can be interrupted by issuing another start command.

ANALOG OPERATION Analog Input Current

The analog comparisons are performed by a capacitive charge summing circuit. The input capacitor is switched between VIN(+)4 and VIN(-), while reference capacitors are switched between taps on the reference voltage divider string. The net charge corresponds to the weighted difference between the input and the most recent total value set by the successive approximation register. The internal switching action causes displacement currents to flow at the analog inputs. The voltage on the on-chip capacitance is switched through the analog differential input voltage, resulting in proportional currents entering the VIN(+) input and leaving the VIN(-) input. These transient currents occur at the leading edge of the internal clock pulses. They decay rapidly so do not inherently cause errors as the on-chip comparator is strobed at the end of the clock period.

Input Bypass Capacitors and Source Resistance

Bypass capacitors at the input will average the charges mentioned above, causing a DC and an AC current to flow through the output resistance of the analog signal sources. This charge pumping action is worse for continuous conversions with the VIN(+) input at full scale. This current can be a few microamps, so bypass capacitors should NOT be used at the analog inputs of the VREF/2 input for high resistance sources (> 1k). If input bypass capacitors are desired for noise filtering and a high source resistance is desired to minimize capacitor size, detrimental effects of the voltage drop across the input resistance can be eliminated by adjusting the full scale with both the input resistance and the input bypass capacitor in place. This is possible because the magnitude of the input current is a precise linear function of the differential voltage.

Digital Control Inputs

The digital control inputs (CS, WR, RD) are compatible with standard TTL logic voltage levels. The required signals at these inputs correspond to Chip Select, START Conversion, and Output Enable control signals, respectively. They are active-Low for easy interface to microprocessor and microcontroller control buses. For applications not using microprocessors, the CS input (Pin 1) can be grounded and the A/D START function is achieved by a negative-going pulse to the WR input (Pin 3). The Output Enable function is achieved by a logic low signal at the RD input (Pin 2), which may be grounded to constantly have the latest conversion present at the output.

August 31, 1994

558

Philips Semiconductors Linear Products

Product specification

CMOS 8-bit A/D converters

ADC0803/4-1

Large values of source resistance where an input bypass capacitor is not used will not cause errors as the input currents settle out prior to the comparison time. If a low pass filter is required in the system, use a low valued series resistor (< 1k) for a passive RC section or add an op amp active filter (low pass). For applications with source resistances at or below 1k, a 0.1F bypass capacitor at the inputs will prevent pickup due to series lead inductance or a long wire. A 100 series resistor can be used to isolate this capacitor (both the resistor and capacitor should be placed out of the feedback loop) from the output of the op amp, if used.

Reference Voltage Span Adjust

Note that the Pin 9 (VREF/2) voltage is either 1/2 the voltage applied to the VCC supply pin, or is equal to the voltage which is externally forced at the VREF/2 pin. In addition to allowing for flexible references and full span voltages, this also allows for a ratiometric voltage reference. The internal gain of the VREF/2 input is 2, making the full-scale differential input voltage twice the voltage at Pin 9. For example, a dynamic voltage range of the analog input voltage that extends from 0 to 4V gives a span of 4V (4-0), so the VREF/2 voltage can be made equal to 2V (half of the 4V span) and full scale output would correspond to 4V at the input. On the other hand, if the dynamic input voltage had a range of 0.5 to 3.5V, the span or dynamic input range is 3V (3.5-0.5). To encode this 3V span with 0.5V yielding a code of zero, the minimum expected input (0.5V, in this case) is applied to the VIN(-) pin to account for the offset, and the VREF/2 pin is set to 1/2 the 3V span, or 1.5V. The A/D converter will now encode the VIN(+) signal between 0.5 and 3.5V with 0.5V at the input corresponding to a code of zero and 3.5V at the input producing a full scale output code. The full 8 bits of resolution are thus applied over this reduced input voltage range. The required connections are shown in Figure 2.

Analog Differential Voltage Inputs and CommonMode Rejection

These A/D converters have additional flexibility due to the analog differential voltage input. The VIN(-) input (Pin 7) can be used to subtract a fixed voltage from the input reading (tare correction). This is also useful in a 4/20mA current loop conversion. Common-mode noise can also be reduced by the use of the differential input. The time interval between sampling VIN(+) and VIN(-) is 4.5 clock periods. The maximum error due to this time difference is given by: V(max)=(VP) (2fCM) (4.5/fCLK), where: V=error voltage due to sampling delay VP=peak value of common-mode voltage fCM=common mode frequency For example, with a 60Hz common-mode frequency, fcm, and a 1MHz A/D clock, FCLK, keeping this error to 1/4 LSB (about 5mV) would allow a common-mode voltage, VP, which is given by: VP + or VP + (5 x 10 *3) (10 4) + 2.95V (6.28) (60) (4.5) [V(max) (f CLK) (2f CM)(4.5)

Operating Mode

These converters can be operated in two modes: 1) absolute mode 2) ratiometric mode In absolute mode applications, both the initial accuracy and the temperature stability of the reference voltage are important factors in the accuracy of the conversion. For VREF/2 voltages of 2.5V, initial errors of 10mV will cause conversion errors of 1 LSB due to the gain of 2 at the VREF/2 input. In reduced span applications, the initial value and stability of the VREF/2 input voltage become even more important as the same error is a larger percentage of the VREF/2 nominal value. See Figure 3. In ratiometric converter applications, the magnitude of the reference voltage is a factor in both the output of the source transducer and the output of the A/D converter, and, therefore, cancels out in the final digital code. See Figure 4. Generally, the reference voltage will require an initial adjustment. Errors due to an improper reference voltage value appear as full-scale errors in the A/D transfer function.

The allowed range of analog input voltages usually places more severe restrictions on input common-mode voltage levels than this, however. An analog input span less than the full 5V capability of the device, together with a relatively large zero offset, can be easily handled by use of the differential input. (See Reference Voltage Span Adjust).

ERRORS AND INPUT SPAN ADJUSTMENTS

There are many sources of error in any data converter, some of which can be adjusted out. Inherent errors, such as relative accuracy, cannot be eliminated, but such errors as full-scale and zero scale offset errors can be eliminated quite easily. See Figure 2.

Noise and Stray Pickup

The leads of the analog inputs (Pins 6 and 7) should be kept as short as possible to minimize input noise coupling and stray signal pick-up. Both EMI and undesired digital signal coupling to these inputs can cause system errors. The source resistance for these inputs should generally be below 5k to help avoid undesired noise pickup. Input bypass capacitors at the analog inputs can create errors as described previously. Full scale adjustment with any input bypass capacitors in place will eliminate these errors.

Zero Scale Error

Zero scale error of an A/D is the difference of potential between the ideal 1/2 LSB value (9.8mV for VREF/2=2.500V) and that input voltage which just causes an output transition from code 0000 0000 to a code of 0000 0001. If the minimum input value is not ground potential, a zero offset can be made. The converter can be made to output a digital code of 0000 0000 for the minimum expected input voltage by biasing the VIN(-) input to that minimum value expected at the VIN(-) input to that minimum value expected at the VIN(+) input. This uses the

Reference Voltage

For application flexibility, these A/D converters have been designed to accommodate fixed reference voltages of 5V to Pin 20 or 2.5V to Pin 9, or an adjusted reference voltage at Pin 9. The reference can be set by forcing it at VREF/2 input, or can be determined by the supply voltage (Pin 20). Figure 1 indicates how this is accomplished.

August 31, 1994

559

Philips Semiconductors Linear Products

Product specification

CMOS 8-bit A/D converters

ADC0803/4-1

differential mode of the converter. Any offset adjustment should be done prior to full scale adjustment.

Full Scale Adjustment

Full scale gain is adjusted by applying any desired offset voltage to VIN(-), then applying the VIN(+) a voltage that is 1-1/2 LSB less than the desired analog full-scale voltage range and then adjusting the magnitude of VREF/2 input voltage (or the VCC supply if there is no VREF/2 input connection) for a digital output code which just changes from 1111 1110 to 1111 1111. The ideal VIN(+) voltage for this full-scale adjustment is given by: V IN() ) + V IN(*) * 1.5 x where: VMAX=high end of analog input range (ground referenced) VMIN=low end (zero offset) of analog input (ground referenced) V MAX * V MIN 255

At higher CPU clock frequencies, time can be extended for I/O reads (and/or writes) by inserting wait states (8880) or using clock-extending circuits (6800, 8035). Finally, if time is critical and capacitive loading is high, external bus drivers must be used. These can be 3-State buffers (low power Schottky is recommended, such as the N74LS240 series) or special higher current drive products designed as bus drivers. High current bipolar bus drivers with PNP inputs are recommended as the PNP input offers low loading of the A/D output, allowing better response time.

POWER SUPPLIES

Noise spikes on the VCC line can cause conversion errors as the internal comparator will respond to them. A low inductance filter capacitor should be used close to the converter VCC pin and values of 1F or greater are recommended. A separate 5V regulator for the converter (and other 5V linear circuitry) will greatly reduce digital noise on the VCC supply and the attendant problems.

WIRING AND LAYOUT PRECAUTIONS CLOCKING OPTION

The clock signal for these A/Ds can be derived from external sources, such as a system clock, or self-clocking can be accomplished by adding an external resistor and capacitor, as shown in Figure 6. Heavy capacitive or DC loading of the CLK R pin should be avoided as this will disturb normal converter operation. Loads less than 50pF are allowed. This permits driving up to seven A/D converter CLK IN pins of this family from a single CLK R pin of one converter. For larger loading of the clock line, a CMOS or low power TTL buffer or PNP input logic should be used to minimize the loading on the CLK R pin. Digital wire-wrap sockets and connections are not satisfactory for breadboarding this (or any) A/D converter. Sockets on PC boards can be used. All logic signal wires and leads should be grouped or kept as far as possible from the analog signal leads. Single wire analog input leads may pick up undesired hum and noise, requiring the use of shielded leads to the analog inputs in many applications. A single-point analog ground separate from the logic or digital ground points should be used. The power supply bypass capacitor and the self-clocking capacitor, if used, should be returned to digital ground. Any VREF/2 bypass capacitor, analog input filter capacitors, and any input shielding should be returned to the analog ground point. Proper grounding will minimize zero-scale errors which are present in every code. Zero-scale errors can usually be traced to improper board layout and wiring.

Restart During a Conversion

A conversion in process can be halted and a new conversion began by bringing the CS and WR inputs low and allowing at least one of them to go high again. The output data latch is not updated if the conversion in progress is not completed; the data from the previously completed conversion will remain in the output data latches until a subsequent conversion is completed.

APPLICATIONS Microprocessor Interfacing

This family of A/D converters was designed for easy microprocessor interfacing. These converters can be memory mapped with appropriate memory address decoding for CS (read) input. The active-Low write pulse from the processor is then connected to the WR input of the A/D converter, while the processor active-Low read pulse is fed to the converter RD input to read the converted data. If the clock signal is derived from the microprocessor system clock, the designer/programmer should be sure that there is no attempt to read the converter until 74 converter clock pulses after the start pulse goes high. Alternatively, the INTR pin may be used to interrupt the processor to cause reading of the converted data. Of course, the converter can be connected and addressed as a peripheral (in I/O space), as shown in Figure 7. A bus driver should be used as a buffer to the A/D output in large microprocessor systems where the data leaves the PC board and/or must drive capacitive loads in excess of 100pF. See Figure 9. Interfacing the SCN8048 microcomputer family is pretty simple, as shown in Figure 8. Since the SCN8048 family has 24 I/O lines, one of these (shown here as bit 0 or port 1) can be used as the chip select signal to the converter, eliminating the need for an address

Continuous Conversion

To provide continuous conversion of input data, the CS and RD inputs are grounded and INTR output is tied to the WR input. This INTR/WR connection should be momentarily forced to a logic low upon power-up to insure circuit operation. See Figure 5 for one way to accomplish this.

DRIVING THE DATA BUS

This CMOS A/D converter, like MOS microprocessors and memories, will require a bus driver when the total capacitance of the data bus gets large. Other circuitry tied to the data bus will add to the total capacitive loading, even in the high impedance mode. There are alternatives in handling this problem. The capacitive loading of the data bus slows down the response time, although DC specifications are still met. For systems with a relatively low CPU clock frequency, more time is available in which to establish proper logic levels on the bus, allowing higher capacitive loads to be driven (see Typical Performance Characteristics).

August 31, 1994

560

Philips Semiconductors Linear Products

Product specification

CMOS 8-bit A/D converters

ADC0803/4-1

decoder. The RD and WR signals are generated by reading from and writing to a dummy address.

A Digital Thermostat

Circuit Description The schematic of a Digital Thermostat is shown in Figure 11. The A/D digitizes the output of the LM35, a temperature transducer IC with an output of 10mV per C. With VREF/2 set for 2.56V, this 10mV corresponds to 1/2 LSB and the circuit resolution is 2C. Reducing VREF/2 to 1.28 yields a resolution of 1C. Of course, the lower VREF/2 is, the more sensitive the A/D will be to noise. The desired temperature is set by holding either of the set buttons closed. The SCC80C451 programming could cause the desired (set) temperature to be displayed while either button is depressed and for a short time after it is released. At other times the ambient temperature could be displayed. The set temperature is stored in an SCN8051 internal register. The A/D conversion is started by writing anything at all to the A/D with port pin P10 set high. The desired temperature is compared with the digitized actual temperature, and the heater is turned on or off by clearing setting port pin P12. If desired, another port pin could be used to turn on or off an air conditioner. The display drivers are NE587s if common anode LED displays are used. Of course, it is possible to interface to LCD displays as well.

Digitizing a Transducer Interface Output

Circuit Description Figure 10 shows an example of digitizing transducer interface output voltage. In this case, the transducer interface is the NE5521, an LVDT (Linear Variable Differential Transformer) Signal Conditioner. The diode at the A/D input is used to insure that the input to the A/D does not go excessively beyond the supply voltage of the A/D. See the NE5521 data sheet for a complete description of the operation of that part. Circuit Adjustment To adjust the full scale and zero scale of the A/D, determine the range of voltages that the transducer interface output will take on. Set the LVDT core for null and set the Zero Scale Scale Adjust Potentiometer for a digital output from the A/D of 1000 000. Set the LVDT core for maximum voltage from the interface and set the Full Scale Adjust potentiometer so the A/D output is just barely 1111 1111.

August 31, 1994

561

Philips Semiconductors Linear Products

Product specification

CMOS 8-bit A/D converters

ADC0803/4-1

TYPICAL PERFORMANCE CHARACTERISTICS

Power Supply Current vs Temperature

3.2 POWER SUPPLY CURRENT (mA) 3.0 2.8 2.6 2.4 5.0V 2.2 2.0 1.8 50 25 0 25 50 75 100 125 AMBIENT TEMPERATURE (Co) 4.5V fCLK = 1MHz CS = H CLOCK FRQ (MHz) 10.0 8.0 6.0 4.0 2.0 1.0 0.8 0.6 0.4 0.2 MIN. 0.1 10 20 40 60 80100 200 400 600 1000 CLOCK CAP (pF) TYP. 3 4 5 0 1 2 3 4 5 APPLIED VREF/2 (V)

Clock Frequency vs Clock Capacitor

5 4 3 2 (mA) MAX. 1 0 1 2

Input Current vs Applied Voltage at VREF/2 Pin

VCC = 5.0V TA = 25oC

5.5V

REF/2

Logic Input Threshold Voltage vs Supply Voltage

4.5 1.70 55oC CLKIN THRESHOLD VOLTAGE (V) 4.0 3.5

CLKIN Threshold Voltage vs Supply Voltage

18 55oC < TA 125oC OUTPUT CURRENT (mA) VT+ 3.0 2.5 2.0 1.5 1.0 4.50 VT

Output Current vs Temperature

VCC = 5.0V 16 14 12 10 VO = 0.4V

LOGIC INPUT (V)

1.60

+25oC +125oC

1.50

VO = 2.5V

1.40

8 6 50

1.30 4.50

4.75

5.00

5.25

5.50

4.75

5.00

5.25

5.50

25

25

50

75

100

125

VCC SUPPLY VOLTAGE (V)

VCC SUPPLY VOLTAGE (V)

AMBIENT TEMPERATURE (oC)

Full Scale Error vs Conversion Time

4 VCC = 5.0V VREF/2 = 3 ERROR (LSB) 350 300 250 DEALY (ns) 200 150 100 1 50 0 0 20 40 60 80 100 120 CONVERSION TIME (s) 0 0

Delay From RD Falling Edge to Data Valid vs Load Capacitance

VCC = 5.0V TA = 25oC

2.5V

200

400

600

800

1000

LOAD CAPACITANCE (pF)

August 31, 1994

562

Philips Semiconductors Linear Products

Product specification

CMOS 8-bit A/D converters

ADC0803/4-1

3-STATE TEST CIRCUITS AND WAVEFORMS (ADC0801-1)

20ns VCC VCC RD CS CL 10pF 10K DATA OUTPUT DATA OUTPUT tr 90% 50% 10% t1H VOH 90% RD CS CL VCC VCC VCC 10K DATA OUTPUT 10pF DATA OUTPUT tr 90% 50% 10% t0H 10%

RD GND

RD GND

VOH

GND

GND

t1H

tOH

TIMING DIAGRAMS (All timing is measured from the 50% voltage points)

START CONVERSION CS

WR

tWI tW(WR)L BUSY ACTUAL INTERNAL STATUS OF THE CONVERTER INTR (LAST DATA WAS NOT READ) INT ASSERTED 1/2 TCLK NOT BUSY (LAST DATA WAS READ) 1 TO 8 X 1/fCLK INTERNAL TC DATA IS VALID IN OUTPUT LATCHES

INTR

INTR RESET

CS

tRI

RD NOTE DATA OUTPUTS tACC t1H, t0H THREESTATE

Output Enable and Reset INTR

NOTE: Read strobe must occur 8 clock periods (8/fCLK) after assertion of interrupt to guarantee reset of INTR.

August 31, 1994

563

Philips Semiconductors Linear Products

Product specification

CMOS 8-bit A/D converters

ADC0803/4-1

VCC

20

VREF

(5V) VREF

R VREF/2 9 FS OFFSET ADJUST DIGITAL CIRCUITS ZS OFFSET ADJUST + 330 TO VREF/2 0.1F

ANALOG CIRCUITS

TO VIN()

Figure 2. Offsetting the Zero Scale and Adjusting the Input Range (Span)

8 10

NOTE: The VREF/2 voltage is either 1/2 the VCC voltage or is that which is forced at Pin 9.

Figure 1. Internal Reference Design

+5V +5V

VCC VIN(+) A/D VOLTAGE REFERENCE VREF/2 VIN() VIN(+) VCC

+5V

+

10F A/D

2k 2k

10F

VREF/2 VREF/2

100

VIN()

2k

2k

a. Fixed Reference

b. Fixed Reference Derived from VCC

c. Optional Full Scale Adjustment

Figure 3. Absolute Mode of Operation

VCC

VIN(+) TRANSDUCER A/D

VCC

+

10F

2k

VIN()

VREF/2

FULL SCALE 100 OPTIONAL

2k

Figure 4. Ratiometric Mode of Operation with Optional Full Scale Adjustment

August 31, 1994

564

Philips Semiconductors Linear Products

Product specification

CMOS 8-bit A/D converters

ADC0803/4-1

10k +5V CS RD WR 10K 2.7k CLK IN INTR 10k 47F TO 100F VIN(+) 56pF VIN() A GND VREF/2 1 2 3 4 5 6 7 8 9 A/D 20 VCC 19 CLK R 18 D0 17 D1 16 D2 15 D3 14 D4 13 D5 12 D6 11 D7 DB1 DB2 DB3 DB4 DB5 DB6 DB7 DB0

+5V

D GND 10

Figure 5. Connection for Continuous Conversion

+5V

CLK R 19

R CLK IN 4 VCC 40 1 fCLK = 1/1.7 R C R = 10K 2 3 4 5 6 P1.0 P1.1 P1.2 P1.3 P1.4 P1.5 P1.6 P1.7 D0 18 D1 17 D2 16 D3 15 D4 14 D5 13 D6 12 D7 11 A/D 6 VIN(+) 7 VREF/2 12 A GND 11 D GND ANALOG INPUTS 4 CLK IN 56pF 10k VCC

20

19 CLK R

CLK

C

A/D

Figure 6. Self-Clocking the Converter

INT I/O WR I/O RD 10k CS RD WR CLK IN INTR ANALOG INPUTS 56pF 1 2 3 4 5 A/D 20 VCC 19 CLK R 18 D0 17 D1 16 D2 15 D3 DB3 14 D4 13 D5 12 D6 11 D7 DB5 DB6 DB7 DB4 DB1 DB2 DB0 +5V

SCN8051 OR SCN80C51

7 8

17 RD 16 WR 12 INTO 39 P0.0

RD 2 WR 3 INTR CS 5 1

Figure 8. SCN8051 Interfacing

18 D0 17 D1 16 D2 15 D3 14 D4 A/D 13 D5 12 D6 11 D7 N74LS241 N74LS244 N74LS541 8BIT BUFFER DATA BUS

VIN(+) 6 VIN() 7 A GND 8 VREF/2 9 D GND 10

ADDRESS DECODE LOGIC

Figure 7. Interfacing to 8080A Microprocessor

OE

Figure 9. Buffering the A/D Output to Drive High Capacitance Loads and for Driving Off-Board Loads

August 31, 1994

565

Philips Semiconductors Linear Products

Product specification

CMOS 8-bit A/D converters

ADC0803/4-1

+5V

Ct

18k 4.7k 1.5k 820 NE5521 LVDT

1F

4.7k

0.47F

22k +5V IN4148

470

VCC VIN(+)

3.3k A/D 2k VIN() VREF/2

2k FULL 100 SCALE ADJUST 2k

Figure 10. Digitizing a Transducer Interface Output

August 31, 1994

566

Philips Semiconductors Linear Products

Product specification

CMOS 8-bit A/D converters

ADC0803/4-1

6 2 1 1/4 HEF4071 7 3

RBI 5

NE587

8 RBO 4

10K

6 2 1 1/4 HEF4071 7 3

RBI 5

NE587

8 10K

LOWER P15 RAISE P16

13

14 18 17 16 15 14 13 DB0 DB1 DB2 DB3 DB4 DB5 DB6 DB7 D0 18 D1 17 D2 16 D3 15 D4 14 D5 13 D6 12 D7 11 A/D 4 10K CLK IN 56pF 8 10 6 27 RD WR INT P10 RD 2 WR INTR CS 3 5 1 D GND 10 8 6 VIN(+) 7 VIN() A GND LM35 19 CLK R 20 VCC + 10F +5V

SCC80C51

12 11

+V 2N3906

29 P12 20 GND

1N4148

TO HEATER

Figure 11. Digital Thermostat

August 31, 1994

567

Das könnte Ihnen auch gefallen

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (587)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (265)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (119)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- MDS I ManualDokument41 SeitenMDS I ManualPanku RangareeNoch keine Bewertungen

- LPA1 Schematic and LayoutDokument4 SeitenLPA1 Schematic and LayoutgusregoNoch keine Bewertungen

- Bipolar Junction Transistor: ELAC 223/221L Electronics 1Dokument25 SeitenBipolar Junction Transistor: ELAC 223/221L Electronics 1Sepillo RandelNoch keine Bewertungen

- 2-Channel PWM Controller for CCFL Backlight RegulationDokument11 Seiten2-Channel PWM Controller for CCFL Backlight RegulationMorales Avila NiorgeNoch keine Bewertungen

- ECE 385 Fall 2014 Lab Manual 20140829Dokument308 SeitenECE 385 Fall 2014 Lab Manual 20140829x y0% (1)

- EC8392-DE Question Bank With Answers 1Dokument44 SeitenEC8392-DE Question Bank With Answers 1shanthiantony100% (1)

- Assignment # 2 Introduction To Computer Bscs-1A: Name: Roll No.: Instructor: Q.1)Dokument3 SeitenAssignment # 2 Introduction To Computer Bscs-1A: Name: Roll No.: Instructor: Q.1)Obaidullah MansoorNoch keine Bewertungen

- Pulse Amplitude Modulation and Demodulation AimDokument3 SeitenPulse Amplitude Modulation and Demodulation AimpravsvizagNoch keine Bewertungen

- Cmos Inverter CharacteristicsDokument5 SeitenCmos Inverter CharacteristicsRichu Jose CyriacNoch keine Bewertungen

- Topic 1 - Introduction To IcDokument40 SeitenTopic 1 - Introduction To IcPojee Tasek100% (1)

- Learn Electronics with Affordable DIY ProjectsDokument6 SeitenLearn Electronics with Affordable DIY ProjectsMomNoch keine Bewertungen

- Ele Lab ReportDokument42 SeitenEle Lab ReportDik Man RyNoch keine Bewertungen

- DEE 20023 SEMICONDUCTOR DEVICES SESI II 2021/2022 FET AMPLIFIERDokument14 SeitenDEE 20023 SEMICONDUCTOR DEVICES SESI II 2021/2022 FET AMPLIFIERmbagavan 0712Noch keine Bewertungen

- TL494 Class D Amplifier Circuit - 500w Amplifier - SolderingmindDokument18 SeitenTL494 Class D Amplifier Circuit - 500w Amplifier - Solderingmindquad electronicsNoch keine Bewertungen

- Crossed-Field Amplifier (CFA)Dokument3 SeitenCrossed-Field Amplifier (CFA)Raúl VargasNoch keine Bewertungen

- Project MicroprocessoresDokument22 SeitenProject Microprocessoresshahd dawoodNoch keine Bewertungen

- EEG Circuit Design and SimulationDokument20 SeitenEEG Circuit Design and SimulationlaibaNoch keine Bewertungen

- 8-Comparator-Assembler BlockDokument17 Seiten8-Comparator-Assembler BlockTam PhamNoch keine Bewertungen

- Phase Locking in High Performance Systems PDFDokument512 SeitenPhase Locking in High Performance Systems PDFShahzad IslahiNoch keine Bewertungen

- Cs2100 4 Logic Gates and CircuitsDokument27 SeitenCs2100 4 Logic Gates and CircuitsamandaNoch keine Bewertungen

- Data Sheet Tda 4800Dokument16 SeitenData Sheet Tda 4800fabioboogNoch keine Bewertungen

- 3.5. Example: Inclusion of Semiconductor Conduction Losses in The Boost Converter ModelDokument8 Seiten3.5. Example: Inclusion of Semiconductor Conduction Losses in The Boost Converter ModelDeepak BishtNoch keine Bewertungen

- Light Activated AlarmDokument8 SeitenLight Activated Alarmpatricia0% (1)

- PWM Top221-227Dokument21 SeitenPWM Top221-227gilsonNoch keine Bewertungen

- Hyundai H-LCD700 LCD Mini TV PDFDokument9 SeitenHyundai H-LCD700 LCD Mini TV PDFkilol0Noch keine Bewertungen

- DC Voltmeter Block DiagramDokument8 SeitenDC Voltmeter Block Diagrammanu0% (1)

- LCDF3 Chap 03 P1Dokument54 SeitenLCDF3 Chap 03 P1boymatterNoch keine Bewertungen

- LPVLSI Unit 3 NotesDokument49 SeitenLPVLSI Unit 3 NotesSai Sreeja100% (1)

- Instrumentation AmplifierDokument7 SeitenInstrumentation AmplifierChandan Kumar ChoubeyNoch keine Bewertungen

- Source Degeneration TheoryDokument9 SeitenSource Degeneration TheoryAbhishek KumarNoch keine Bewertungen