Beruflich Dokumente

Kultur Dokumente

Part 4

Hochgeladen von

bhushanchittaragiOriginalbeschreibung:

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Part 4

Hochgeladen von

bhushanchittaragiCopyright:

Verfügbare Formate

1

October 2010 Fabian Kung Wai Lee 1

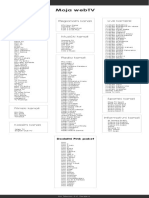

Part 4 PCB LAYOUT

RULES FOR SIGNAL

INTEGRITY

The information in this work has been obtained from sources believed to be reliable.

The author does not guarantee the accuracy or completeness of any information

presented herein, and shall not be responsible for any errors, omissions or damages

as a result of the use of this information.

October 2010 Fabian Kung Wai Lee 2

References

[1] H. Johnson, M. Graham, High-speed digital design A handbook of black

magic, Prentice-Hall, 1993.

[2] D.M. Pozar, Microwave engineering, 2nd edition, 1998 John-Wiley & Sons.

[3] M. I. Montrose, EMC and printed circuit board design theory and layout

made simple, IEEE Press, 1999.

[4] T. C. Edwards, Foundations for microstrip circuit design, 2nd edition, 1992

John-Wiley & Sons.

[5] T. C. Edwards, Foundations of interconnect and microstrip design, 3

rd

edition, 2000, John-Wiley & Sons.

[6] H. Howe, Stripline circuit design, 1974, Artech House.

[7] I. Bahl, P. Bhartia, Microwave solid state circuit design, 2

nd

edition, 2003,

John-Wiley & Sons.

[8] http://pesona.mmu.edu.my/~wlkung/Master/mthesis.htm

[9] S. H. Hall, G. W. Hall, J. A. McCall, High-speed digital system design,

2000, John-Wiley & Sons.

[10] T. Williams, EMC for product designers, 2001, Butterworth-Heinemann.

[11] H. W. Ott, Noise reduction techniques in electronic systems, 1988, John-

Wiley & Sons.

[12] D. Brooks, Signal integrity issues and printed circuit board design, 2003,

Prentice Hall.

2

Introduction

By PCB layout we imply the designing the pattern or the shape of the

conducting structures on the PCB, stacking up the various layers of the

PCB, placement of components and vias.

The purpose of a good PCB layout tends to achieve the following

objectives:

(A) Provide a means of sending electrical energy from one

component to the other with as little obstacle as possible.

(B) Provide sufficient isolation such that electrical signal in

one path does not affect other, and vice versa. This means we

want to reduce electric/magnetic field coupling, and also common

impedance coupling.

We can achieve objective A by reducing unnecessary reflections or

distortion and loading along the signal path for high-speed signal.

We can achieve objective B by providing proper grounding and noise

suppression on the power delivery system of the circuit (and also

sufficient spatial separation).

October 2010 Fabian Kung Wai Lee 3

October 2010 Fabian Kung Wai Lee 4

4.1 Introduction to the

Concept of Discontinuities

in Transmission Line Circuit

3

October 2010 Fabian Kung Wai Lee 5

Practical Transmission Line Design

and Discontinuities

Discontinuities in Tline are changes in the Tline geometry to

accommodate layout and other requirements on the printed circuit

board.

Virtually all practical distributed circuits, whether in waveguide, coaxial

cables, microstrip line etc. must inherently contains discontinuities. A

straight uninterrupted length of waveguide or Tline would be of little

engineering use.

The following discussion consider the effect and compensation for

discontinuities in PCB layout. This discussion is restricted to TEM or

quasi-TEM propagation modes.

October 2010 Fabian Kung Wai Lee 6

Ground plane gap

trace

plane

gap

trace

ground plane Bend

bend

Socket-trace interconnection

socket

pin

trace

via

Via

plane

cylinder

trace

pad

Junction

Bend

Line to Component

Interface

Step

Open

Transmission Line Discontinuities

Found in PCB (1)

Here we illustrate the

discontinuities using

microstripline. Similar

structures apply to

other transmission line

configuration as well.

4

October 2010 Fabian Kung Wai Lee 7

Transmission Line Discontinuities

Found in PCB (2)

Further examples of microstrip and co-planar line discontinuities.

Gap

Pad or Stub

Coupled lines

Examples of bend and via

on co-planar Tline.

October 2010 Fabian Kung Wai Lee 8

Discontinuities and EM Fields (1)

Introduction of discontinuities will distort the uniform EM fields present

in the infinite length Tline. Assuming the propagation mode is TEM or

quasi-TEM, the discontinuity will create a multitude of higher modes

(such as TM

11

, TM

12

, TE

11

, ) in its vicinity in order to fulfill the

boundary conditions (Note - there is only one type of TEM mode !!).

Most of these induced higher order modes are evanescent or non-

propagating as their cut-off frequencies are higher than the operating

frequency of the circuit. Thus the fields of the higher order modes are

known as local fields.

The effect of discontinuity is usually reactive (the energy stored in the

local fields is returned back to the system) since loss is negligible.

The effect of reactive system to the voltage and current can be

modeled using LC circuits (which are reactive elements).

For TEM or quasi-TEM mode, we can consider the discontinuity as a 2-

port network containing inductors and capacitors.

5

October 2010 Fabian Kung Wai Lee 9

See Chapter 5, T.C. Edwards, Foundation

for microstrip circuit design [4], or Chapter 3 [8]

Discontinuities and EM Fields (2)

Modeling a discontinuity using circuit theory element such as RLCG is a

good approximation for operating frequency up to 6 -20 GHz. This upper

limit depends on substrate thickness and size of discontinuity.

The smaller the dimension of the discontinuity as compared to the

wavelength, the higher will be the upper usable frequency.

As a example, the 2-port model for a microstrip bend is usually accurate

up to 10 GHz.

A

A

B B

0.25

0.25

Minimum distance

A

A

B

B

Two port

networks

0.25

October 2010 Fabian Kung Wai Lee 10

Discontinuities and EM Fields (3)

For instance for a microstrip bend, a snapshot of the EM fields at a

particular instant in time:

Non-TEM mode

field here*

Quasi-TEM

field

H field

E field

*This field can be decomposed into

TEM and non-TEM components

Direction of propagation

6

October 2010 Fabian Kung Wai Lee 11

Methods of Obtaining Equivalent

Circuit Model for Discontinuities (1)

3 Typical approaches

Method 1: Analytical solution - see Chapter 4, reference [3] on Modal

Analysis for waveguide discontinuities.

Method 2: Numerical methods, for example:

Method of Moments (MOM).

Finite Element Method (FEM).

Finite Difference Time Domain Method (FDTD).

And many others.

Numerical methods are used to find the quasi-static EM fields of a 3D

model containing the discontinuity. The EM field in the vicinity of the

discontinuity is split into TEM and non-TEM fields. LC elements are

then associated with the non-TEM fields using formula similar to (3.1)

in Part 3.

Agilents Momentum

Ansofts HFSS CSTs Microwave

Studio

Sonnet

October 2010 Fabian Kung Wai Lee 12

Methods of Obtaining Equivalent Circuit

Model for Discontinuities (2)

Method 3: Fitting measurement with circuit models. By proposing an

equivalent circuit model, we can try to tune the parameters of the circuit

elements in the model so that frequency/time domain response from

theoretical analysis and measurement match.

Measurement can be done in time domain using time-domain

reflectometry (TDR) and frequency domain measurement using a

vector network analyzer (VNA) (see Chapter 3 of Ref [4] for details).

7

October 2010 Fabian Kung Wai Lee 13

4.2 - Practical Stripline

Discontinuities

October 2010 Fabian Kung Wai Lee 14

Microstrip Line Discontinuity Models

(1)

Through hole:

|

|

\

|

+ |

\

|

1

4

ln 2 . 0

d

h

h L

s

(2.1a)

L

s

in nH

C

p

in pF

h in mm

d and d

2

in mm

r

= dielectric constant of PCB

N = number of GND planes

N C

d d

hd

r

p

2

056 . 0

(2.1b)

L

s

0.5C

p

0.5C

p

h

d = diameter of via or

internal pad

Cross section

of a Via

GND planes

d

2

= diameter

of relief or

antipad

This is the capacitance between the via and

internal plane. If there are multiple internal

conducting planes, then there should be one

C

p

corresponding to each internal plane.

8

October 2010 Fabian Kung Wai Lee 15

Microstrip Line Discontinuity Models

(2)

90

o

Bend:

L

C

L

See Edwards [4], Chapter 5

Approximate quasi-static expressions for L

1

, L

2

and C:

( ) ( )

pF/m

/

25 . 2 83 . 1 5 . 12 14

d w

w

C

r

d

w

r

+

=

T

2

T

1

w

( ) pF/m 0 . 7 2 . 5 25 . 1 5 . 9 + + + =

r

d

w

r

w

C

1 <

d

w

1 >

d

w

nH/m 21 . 4 4 100

(

=

d

w

d

L

for

for

r

= dielectric constant of substrate,

assume non-magnetic.

d = thickness of dielectric in meter.

(2.2a)

(2.2b)

October 2010 Fabian Kung Wai Lee 16

Example 2.1 - Microstrip Line Bend

For a 90

o

microstrip line bend, with w = 0.92mm, d = 0.51mm,

r

= 4.6

(non-magnetic substrate). Find the value of L and C for the bend.

( )

0.10pF 0.00092 111.83 C

pF/m 111.83

0 . 7 6 . 4 2 . 5 8 . 1 25 . 1 6 . 4 5 . 9

= =

=

+ + + =

w

C

834 . 1 =

d

w

[ ]

60pH L

nH/m 115.66 21 . 4 8 . 1 4 100

= =

d

L

0.10pF

30.0pH 30.0pH

At 1GHz:

Reactance of C

Reactance of L

1592

2

1

=

fC c

X

38 . 0 2 = fL X

L

Typically the effect of bend is not

important for frequency below 1 GHz.

This is also true for discontinuities like

step and T-junction.

9

October 2010 Fabian Kung Wai Lee 17

Microstrip Line Discontinuity Models

(3)

Step:

L

1

C

L

2

( ) pF/m 17 . 3 log 6 . 12 33 . 2 log 1 . 10

2

1

2 1

+ =

r

w

w

r

w w

C

T

2

T

1

w

2

w

1

See Edwards [4] Chapter 5

Approximate quasi-static expressions for L

1

, L

2

and C:

pF/m 44 - log 130

1

2

2 1

|

\

|

=

w

w

w w

C

10 5 . 1 ; 10

1

2

w

w

r

10 5 . 3 ; 6 . 9

1

2

=

w

w

r

nH/m 0 . 1 2 . 0 75 0 . 1 5 . 40

2

2

1

2

1

2

1

|

\

|

+ |

\

|

=

w

w

w

w

w

w

d

L

L

L L

L

L

m m

m

2 1

1

1

+

=

L

L L

L

L

m m

m

2 1

2

2

+

=

L

m1

and L

m2

are the per unit length

inductance of T

1

and T

2

respectively.

for

for

(2.3a)

(2.3b)

October 2010 Fabian Kung Wai Lee 18

Microstrip Line Discontinuity Models

(4)

T-Junction:

T

1

T

3

T

2

L

1

C

1

L

1

T

1

T

2

T

3

L

3

See Edwards [4], Chapter 5

for alternative model and

further details.

10

October 2010 Fabian Kung Wai Lee 19

Connector Discontinuity: Coaxial -

Microstrip Line Transition (1)

Since most microstrip line invariably leads to external connection from

the printed circuit board, an interface is needed. Usually the microstrip

line is connected to a co-axial cable.

An adapter usually used for microstrip to co-axial transistion is the SMA

to PCB adapter, also called the SMA End-launcher.

October 2010 Fabian Kung Wai Lee 20

Connector Discontinuity: Coaxial -

Microstrip Line Transition (2)

Again the coaxial-to-microstrip transition is a form of discontinuity, care

must be taken to reduce the abruptness of the discontinuity. For a

properly designed transition such as shown in the previous slide, the

operating frequency could go as high as 6 GHz for the coaxial to

microstrip line transition and 9 GHz for the coaxial to co-planar line

transition.

11

October 2010 Fabian Kung Wai Lee 21

Effect of Discontinuities

Looking at the equivalent circuit models for the microstrip

discontinuities, the sharp reader will immediately notice that all these

networks can be interpreted as Low-Pass Filters. The inductor

attenuates the electrical signal at high frequency while the capacitor

shunts electrical energy at high frequency.

Thus the effect of having too many discontinuities in a high-frequency

circuit reduces the overall bandwidth of the interconnection.

Another consequence of discontinuities is attenuation due to radiation

from the discontinuity.

f

|H(f)|

0

f

|H(f)|

0

October 2010 Fabian Kung Wai Lee 22

Radiation Loss from Discontinuities

At higher frequency, say > 5 GHz, the assumption of lossless

discontinuity becomes flawed. This is because the higher order mode

EM fields can induce surface wave on the printed circuit board, this

wave radiates out so energy is loss.

Furthermore the acceleration or deceleration of electric charge also

generates radiation.

The losses due to radiation can be included in the equivalent circuit

model for the discontinuity by adding series resistance or shunt

conductance.

12

October 2010 Fabian Kung Wai Lee 23

Exercise 2.1

What do you expect the equivalent circuit of the following discontinuity

to be ?

October 2010 Fabian Kung Wai Lee 24

4.3 PCB Layout Rules for

Reducing the Effect of

Discontinuity

13

October 2010 Fabian Kung Wai Lee 25

Reducing the Effects of Discontinuity

(1)

To reduce the effect of discontinuity, we must reduce the values of the

associated inductance and capacitance. This can be achieved by

decreasing the abruptness of the discontinuity, so that current flow will

not be disrupted and charge will not accumulate.

Chamfering of bends

W

b

For 90

o

bend:

It is seen that the optimum

chamfering is b=0.57W

(see Chapter 5, Edwards [4])

For further examples see

Chapter 2, Bahl [7].

W

1.42W

W

W

NOTE:

Generally these are not needed for frequency < 300 MHz

October 2010 Fabian Kung Wai Lee 26

Reducing the Effects of Discontinuity

(2)

T

2

T

1

Mitering of junction Mitering of step

For more details of compensation for discontinuity,

please refer to Chapter 5 of Edwards [4] and

Chapter 2 of Bahl [7].

T

1

T

3

T

2

W

2

W

1

0.7W

1

T

1

T

3

T

2

W

2

W

1

2W

2

0.5W

2

or

smaller

NOTE:

Generally these are not needed for frequency < 300 MHz

14

Reducing the Effects of Discontinuity

(3)

October 2010 Fabian Kung Wai Lee 27

Reduce the length

of the via by using

inner trace layer

and remove the stub

(e.g. use buried or

blind via).

Top view of a Via

Side view of a Via

A tear-drop shape pad (typically only

recommended for frequency above 1 GHz).

The extra capacitance

of the tear-drop shape

balance the effect of

the inductance associated

with the via.

The tear-drop shape also

improves reliability of

contact between trace and

pad.

Handling Stubs (1)

Stubs are short trace segment that extend from the main trace. Most

often they connect to a solder pad and a component.

October 2010 Fabian Kung Wai Lee 28

Keep branching stub and unterminated

stub short, less than 0.1, where is the

shortest wavelength encountered

15

Handling Stubs (2)

October 2010 Fabian Kung Wai Lee 29

Add compensation to bend

if necessary

October 2010 Fabian Kung Wai Lee 30

Exercise 3.1

Explain qualitatively the effect of compensation on the equivalent

electrical circuits of the discontinuity in the previous slides.

16

October 2010 Fabian Kung Wai Lee 31

Example 3.1

A Z

c

= 50 microstrip Tline is used to drive a resistive termination as

shown.

MSUB

MSub1

Rough=0 mi l

TanD=0.02

T=1.38 mi l

Hu=3.9e+034 mi l

Cond=5.8E+7

Mur=1

Er=4.6

H=0.8 mm

MSub

VIAHS

V1

T=1.0 mi l

H=0.0 mm

D=20.0 mi l

VIAHS

V2

T=1.0 mi l

H=0.8 mm

D=20.0 mi l

VIAHS

V3

T=1.0 mi l

H=0.8 mm

D=20.0 mi l

VIAHS

V4

T=1.0 mi l

H=0.8 mm

D=20.0 mi l

VIAHS

V5

T=1.0 mi l

H=0.8 mm

D=20.0 mi l

VIAHS

V6

T=1.0 mi l

H=0.8 mm

D=20.0 mi l

R

R2

R=100 Ohm

R

R1

R=100 Ohm

C

C1

C=0.47 pF

MLIN

TL3

L=15.0 mm

W=1.45 mm

Subst="MSub1"

MLIN

TL2

L=10.0 mm

W=1.45 mm

Subst="MSub1"

MLIN

TL1

L=25.0 mm

W=1.45 mm

Subst="MSub1"

MSOBND_MDS

Bend1

W=1.45 mm

Subst="MSub1"

MSOBND_MDS

Bend2

W=1.45 mm

Subst="MSub1"

L

LSMA1

R=

L=1.2 nH

C

CSMA2

C=0.33 pF

C

CSMA1

C=0.33 pF

Port

P1

Num=1

Example of schematic with discontinuity

Elements (Agilents ADS software)

October 2010 Fabian Kung Wai Lee 32

Example 3.2 Photomicrographs of

PCB

Photomicrograph of microstrip line bend and step (60X).

graticules in mm

Bend in microstrip line

Step in microstrip line

Narrower traces

to BGA IC package

17

October 2010 Fabian Kung Wai Lee 33

4.4 PCB Layout Rules for

Isolation: Grounding

October 2010 Fabian Kung Wai Lee 34

The Ground (GND)

A SINGLE conductor in the PCB or system is called the Ground (GND).

It is assumed the GND has a stable electric potential (with respect to

infinity) and this potential is uniform throughout the conductor. This can

be enforced by using a good conductor (low impedance) and limiting the

GND conductor size to as small as practical.

All electric potential in the PCB or system is measured with respect to

GND, and we can arbitrarily assign a value of 0V to the GND potential.

This 0V GND conductor is what we assumed when drawing schematics.

The process of creating the GND conductor is called Grounding. An

ideal GND is just a concept, as all real conductor has finite impedance

and we cannot ensure uniform potential throughout the GND conductor

for high frequency signals.

18

October 2010 Fabian Kung Wai Lee 35

Example of Ground - Earth and Signal

Ground

A simplified view of typical instrument powered via mains supply.

Voltage

Regulator

Step-down

transformer

Circuit

V

CC

I/O

to other

hardware

Live

Neutral

Earth

110V /240V AC

Service

Outlet

Earth connection

Metal Chassis

Safety Ground

or Earth

Signal Ground

Note that only ONE point on the

signal ground is connected to the

chassis of the instrument

Fuse

October 2010 Fabian Kung Wai Lee 36

Signal Ground

The aims of grounding are:

To allow electric charge and current to flow from source to load and

back to the source, i.e. provide a return path.

For low frequency circuit, to provide a stable reference potential

(0V).

To control electromagnetic interference due to electric and magnetic

field coupling, i.e. provide reasonable isolation. We have already

seen this in action in our discussion on multiconductor transmission

line and crosstalk in Part 3.

Tx

Rx

A Tx/Rx System

Ground

Signal

Conductor

Good layout practices on the PCB

are of utmost importance in

ensuring the circuit works properly.

19

October 2010 Fabian Kung Wai Lee 37

Signal Ground: Single-Point Ground

Series Ground System

- Easy to implement.

- Suffers from common-impedance coupling.

Parallel Ground System

- Less common-impedance coupling.

- Mutual coupling (inductive and capacitive) between

ground leads should be minimised.

1 2 3 1 2 3

Series Ground Parallel Ground

Can be signal or earth ground

GND

Usually a bus-bar as in

high voltage circuits

October 2010 Fabian Kung Wai Lee 38

Signal Ground: Multi-point Ground

Uses large ground plane as common ground conductor.

Circuits that require ground connection are connected to the nearest

available ground plane.

Also suffer from common impedance coupling but it can be reduced

by lowering the ground-impedance.

Typically used in multilayer PCB.

1 2 3

20

October 2010 Fabian Kung Wai Lee 39

Grounding Consideration: Common-

Impedance Coupling (1)

The same GND impedance is seen by all modules.

Inclusive of the resistance

and partial inductance

of the GND

1 2 3

I

1

I

2

I

3

I

3 I

2

+I

3

I

1

+I

2

+I

3

Source

V

1

V

s

Z

g

( )

( )

g s

g s

Z I I I V V

V Z I I I V

3 2 1 1

1 3 2 1

+ + =

+ + + =

Voltage across module 1 is modulated by the changes

in other modules. This effect is also known as Ground

Bounce.

October 2010 Fabian Kung Wai Lee 40

Grounding Consideration: Common-

Impedance Coupling (2)

Common-impedance coupling can occurs on both source (i.e. the V

CC

)

and return path in a PCB assembly. It is more serious in system which

uses series or multi-point ground scheme.

Common-impedance coupling can be reduced by using low impedance

source and ground path, reduce Z

g

and Z

p

(V

CC

path impedance), i.e.

use power plane and ground plane instead of power and ground

traces/buses.

Segmentation of the circuits and ground planes reduces common-

impedance coupling.

Using decoupling capacitors and RF chokes can help filter out large

voltage fluctuations.

21

October 2010 Fabian Kung Wai Lee 41

Reducing Common-Impedance Coupling

with Decoupling Capacitors

If common-impedance coupling is mainly due to large transient/AC

current, adding decoupling capacitors on each block will helps.

Block here can means a group of components or an integrated circuit.

1

I

1

2

I

2

3

I

3

Source

V

s

Z

g

Loop for AC current

Decoupling capacitor, good quality capacitor

(with low ESR, ESL) placed near the module.

Putting decoupling

capacitors near

each IC in

through-hole and

SMD components

October 2010 Fabian Kung Wai Lee 42

Grounding Consideration: Current Return

Path (1)

Coupling is minimised if current returns via a path as near as possible

to the incident path (to reduce the effect of stray fields).

Current will always follows the path with least impedance, this is a

consequent of the law of physics where the energy of a system will

tend towards lowest energy state.

At low frequency, the resistance of a path dominates the impedance,

while at high frequency, the reactance of a path dominates. This is

best summarized as follows:

Low frequency current flows through the path with least resistance.

High frequency current flows through the path with least

impedance.

Current that flows on least impedance path will create less fringing EM

fields, thus less opportunity to interfere with other circuits.

Least impedance path usually correspond to the signal and return path

which minimizes the loop area.

22

October 2010 Fabian Kung Wai Lee 43

Grounding Consideration: Current Return

Path (2)

Low frequency content

current

Least resistance path

High frequency content

current

Least impedance

path

Minimize the area between

signal and return path

October 2010 Fabian Kung Wai Lee 44

Grounding Consideration: Ground Break

Ground break

Detour for return current, more magnetic flux

linkage. This will manifest as extra inductance in

the interconnect circuit.

Furthermore the E and H fields will extend further from

the circuit, making it easier for this circuit to interfere

and be interfered.

23

October 2010 Fabian Kung Wai Lee 45

Equivalent circuit due to ground break

Effect of Ground Break (1)

A break in ground plane for transmission line is not desirable, return

current will have to flow a longer distance, this manifests as extra

inductance (because of extra magnetic field generated in the vicinity of

the break). However, from measurement, it is observed that this effect is

only important for frequencies of 2 GHz and above if a,b > 3W.

In system where a ground plane is not possible, then the use of ground

grid is encouraged. Usage of grid provides a number of return path for

the signal current, thus allowing the return current to choose the path

that is of lowest impedance.

Top Trace

W = width of

transmission line

Gnd plane

a

b

Signal current

Return

current

October 2010 Fabian Kung Wai Lee 46

Effect of Ground Break (2)

Ground break also increases coupling between traces.

Ground break

Trace 1

Trace 2

EM fields due to return signal

and return current from

Trace 1 coupled to Trace 2

24

October 2010 Fabian Kung Wai Lee 47

Example 4.1

A numerical experiment is performed using Maxwell SV software. The

figure below shows the 2D plot of the E field magnitude for 2

conductors sandwiching a FR4 substrate.

Top conductor has 1V potential while bottom is GND at 0V.

When the conductors are

misalligned.

If another conductor is

placed here, E field

coupling would occur.

Same argument can be shown

for H field too!

October 2010 Fabian Kung Wai Lee 48

Ground Scheme 1 - Power Distribution

and Ground on Same Layer

The power and ground wires can be considered as a signal-ground

combination. Therefore based on previous discussion on current return

path, these must be near each other.

V

CC GND

GND

V

CC

Not Encouraged

Good Practice

25

October 2010 Fabian Kung Wai Lee 49

Ground Scheme 2 Using Ground Grid

Reduce ground path impedance

Allow shorter return path.

October 2010 Fabian Kung Wai Lee 50

Ground Scheme 3 Using Ground

Ring

GND

trace

Circuit module 1

Circuit

module 2

Circuit

module 3

Circuit

module 4

You can use similar

scheme for the power

distribution, the VCC

bus on another layer.

Bear in mind to keep

the traces as close as

possible.

26

October 2010 Fabian Kung Wai Lee 51

Ground Scheme 4 - Ground Plane and

Segmentation for Hybrid System

+12V

+5V

Link to maintain

same d.c. ground

potential

Electromechanical

Analog

Digital

Separation of ground plane allows isolation of

each module from the effect of common-impedance

coupling.

This is the best scheme as it allows return current to

flow directly beneath the power lines.

October 2010 Fabian Kung Wai Lee 52

Using Ground Plane

To reduce common impedance coupling and promote return current to

flow as near as source current, ground plane should be used wherever

possible.

Ground plane has much lower partial self inductance and resistance as

compared to ground trace. Thus common impedance effect is vastly

reduced.

Source and return current near each other results in small loop area,

this in turn reduces mutual inductance between different current loop.

Flooded ground on top side and ground

plane on bottom side of PCB to

ensure return current

follows the signal current

closely. A GND plane

is on the bottom to provide

further isolation.

27

October 2010 Fabian Kung Wai Lee 53

Example 4.2 - Isolating Noisy or

Critical Current

If there are only a few traces that carry high-speed signal, we can

control the flow of the return current by removing part of the GND

conductor.

Top View

GND

Trace

Example 4.3 Signal Trace Crossing

Unrelated GND Plane

October 2010 Fabian Kung Wai Lee 54

IC1

IC2

Analog GND

plane

Digital GND

plane

Signal Trace

Possible return

current paths,

both are equally

undesirable

28

October 2010 Fabian Kung Wai Lee 55

Using Multi-Layer PCB

The advantages:

More trace layers for routing.

Can minimize crosstalk by having critical traces on different trace

layers isolated by conducting planes, or having the critical traces

perpendicular to each other.

The GND and Power planes provide the return path, return current

flows near source current.

The planes have low self impedance.

The planes serve to isolate traces (top and bottom trace layer).

The planes form a good decoupling capacitor.

October 2010 Fabian Kung Wai Lee 56

Some Suggestions for Layer Stacking in

Multi-layer PCB

Bottom signal

trace

Top signal

trace

Power plane

V

CC

Ground plane

GND

Dielectric

Power plane

Ground plane

Internal signal

trace

Use Top and Bottom

traces for high-speed

signals. The planes

serve to isolate the

high-speed traces.

Use internal signal

trace 1 for high-speed

signals. These internal

trace acts as striplines,

with the added benefits

of very low dispersion.

GND

GND

Internal signal

trace 1

GND

V

CC

Internal signal

trace 2

These form a

good decoupling

capacitor for the

power supply

4 Layers Board

6 Layers Board

8 Layers Board

29

October 2010 Fabian Kung Wai Lee 57

Return Current Path for Multi-Layer PCB (1)

For a signal trace which is sandwiched by two conducting planes, the

return current exist on both planes.

GND

Plane

V

cc

Plane

Decoupling capacitor

If we use stripline configuration with

V

CC

and GND planes, always place

sufficient decoupling capacitors near

the driver to provide an AC short

between both planes.

Return current

on GND plane

Return current

on V

cc

plane

October 2010 Fabian Kung Wai Lee 58

Return Current Path for Multi-Layer PCB (2)

There are occasions when the return current has to switch GND

planes.

Signal current

GND1

GND2

Signal

Trace

Coupling capacitor

to AC short both GND planes

30

October 2010 Fabian Kung Wai Lee 59

Example 4.4 - Minimizing Noise on Sensitive

Circuits: Connecting I/O Lines to Outside World

Critical

Circuits

Medium critical circuits

Clean interface

Ground (a separate ground plane or metal on chasis)

Earth or

External ground

Low impedance

path

Single-point link, can insert

an RF choke

I/O lines

Suppresion/filter

components

Break in

GND plane

Example 4.5 Recommended Way to Pin

Assignment on Connector

October 2010 Fabian Kung Wai Lee 60

Signal1

Signal2

Signal3

GND

GND

PCB

Connector/

Receptacle

31

Example 4.6 Changing Trace Layers

for a Bus

The vias are staggered to reduce crosstalk between them.

October 2010 Fabian Kung Wai Lee 61

Trace on top side

Inner or bottom

trace

Top View

Example 4.7 Usign Feed-Through

Capacitor Filters to Slow Down Signals

October 2010 Fabian Kung Wai Lee 62

Example of feed-through

capacitor filter from Murata Corp.

Example of feed-through

capacitor filter from AVX Corp.

Insertion loss versus

frequency for various

parts

32

October 2010 Fabian Kung Wai Lee 63

Example 4.8 - Minimizing Noise on Sensitive

Circuits: Preventing Unwanted GND Current

Be careful of accidental current loop due to multi-point ground

connections.

Voltage

Regulator

Step-down

transformer

Circuit

V

CC

I/O

to other

hardware

Live

Neutral

Earth

110V /240V AC

Service

Outlet

Earth connection

Metal Chassis

Safety Ground

or Earth

Signal Ground

Fuse

Ground loop: Current can be induced

in this loop by external magnetic field.

This induced current can cause fluctuation

of GND potential and stray current to flow

into the circuit (common-mode current).

October 2010 Fabian Kung Wai Lee 64

Grounding Rules

Identify circuits with high rate-of-change (di/dt, dv/dt, for emissions),

e.g. clocks, bus buffers/drivers and high-power oscillators.

Identify sensitive circuits (for susceptibility), e.g. low-level analog signal

or high-speed digital data.

Minimize ground impedance by 1) Keeping sensitive circuits away from

the edge of the PCB, 2) Minimize loop area, 3) Use ground plane.

Ensure that internal and external ground noise cannot couple in or out

of the system, incorporate a clean interface ground.

Segmentation of circuits and ground.

No crossing of signal trace from one region to another.

33

October 2010 Fabian Kung Wai Lee 65

Other Topics of Interests in this Part

Here are some other topics that are deemed important but are not

covered due to time constraint:

Power supply noise filtering and decoupling.

Simultaneous switching noise.

Placement and selection of capacitors for decoupling.

Decoupling performance analysis.

Using active voltage regulator onboard PCB.

October 2010 Fabian Kung Wai Lee 66

Key Learning of Part 4

Concept of discontinuity in interconnect.

Equivalent electrical circuit of discontinuity.

Effect of discontinuity on signal propagation along interconnect.

How to compensate for the effect of discontinuity.

Type of ground.

Current return path high and low-frequency condition.

Common-impedance coupling.

Ground break and its effect.

Ground and power distribution scheme.

Use of multi-layer PCB and conductor layers stacking.

Das könnte Ihnen auch gefallen

- Design Microwave Filters Using Ansoft DesignerDokument50 SeitenDesign Microwave Filters Using Ansoft Designersimsook91100% (1)

- Band Stop Filter TodayDokument4 SeitenBand Stop Filter TodayrehanNoch keine Bewertungen

- 12dDokument67 Seiten12dDan FarrisNoch keine Bewertungen

- Reducing MOSFET Consumption by Switched Biasing: 1 F Noise and PowerDokument8 SeitenReducing MOSFET Consumption by Switched Biasing: 1 F Noise and PowerkurabyqldNoch keine Bewertungen

- Microwave Engineering exam questionsDokument2 SeitenMicrowave Engineering exam questionsgunmnkrNoch keine Bewertungen

- Microwave Transmission LineDokument28 SeitenMicrowave Transmission Lineshagunbhatnagar2Noch keine Bewertungen

- Design Patch Good PDFDokument6 SeitenDesign Patch Good PDFJuliana NepembeNoch keine Bewertungen

- Micro Mag PowerDokument10 SeitenMicro Mag Powerjahan69Noch keine Bewertungen

- Stripline Design for Microwave CharacterizationDokument4 SeitenStripline Design for Microwave CharacterizationPaul ShineNoch keine Bewertungen

- Aperture Coupled Fed Micro-Strip Patch AntennaDokument5 SeitenAperture Coupled Fed Micro-Strip Patch AntennaemremiranNoch keine Bewertungen

- Mesh Antennas With Reduced Size: July 2004Dokument5 SeitenMesh Antennas With Reduced Size: July 2004sheng-huang WuNoch keine Bewertungen

- A Fully Integrated CMOS DCS-1800 Frequency Synthesizer: Jan Craninckx,, and Michel S. J. SteyaertDokument12 SeitenA Fully Integrated CMOS DCS-1800 Frequency Synthesizer: Jan Craninckx,, and Michel S. J. SteyaertgopipatNoch keine Bewertungen

- Microstrip Low Pass Filter DesignDokument22 SeitenMicrostrip Low Pass Filter DesignSakshiKoul100% (1)

- Midterm Exam: 1 Cellular PrinciplesDokument5 SeitenMidterm Exam: 1 Cellular PrinciplesAbdelhakim KhlifiNoch keine Bewertungen

- Performance Analysis of Phase Noise Impaired Ofdm Systeminamultipath Fading ChannelDokument6 SeitenPerformance Analysis of Phase Noise Impaired Ofdm Systeminamultipath Fading Channeljagadeesh jagadeNoch keine Bewertungen

- Improvement of Efficiency Parameter of A Microstrip Patch Antenna Operating at 2.4 GHZ For WlanDokument6 SeitenImprovement of Efficiency Parameter of A Microstrip Patch Antenna Operating at 2.4 GHZ For Wlanavneet sandhuuuNoch keine Bewertungen

- RF-Microwave PCB Design and LayoutDokument33 SeitenRF-Microwave PCB Design and LayoutName100% (8)

- Cross Talk Details and RoutingDokument29 SeitenCross Talk Details and RoutingRohith RajNoch keine Bewertungen

- UWB Electric and Magnetic Monopole AntennasDokument7 SeitenUWB Electric and Magnetic Monopole Antennasputin208Noch keine Bewertungen

- 4P4 1135Dokument4 Seiten4P4 1135Tomislav JukićNoch keine Bewertungen

- Design and Analysis of A 2.4 GHZ, Fifth - Order Chebyshev Microstrip LPFDokument6 SeitenDesign and Analysis of A 2.4 GHZ, Fifth - Order Chebyshev Microstrip LPFJournal of TelecommunicationsNoch keine Bewertungen

- Planar Transmission Line Technologies for CMB PolarizationDokument15 SeitenPlanar Transmission Line Technologies for CMB PolarizationsumantaboseNoch keine Bewertungen

- Radiation Pattern Improvement of Patch Antennas Using Compact Soft Surface StructuresDokument28 SeitenRadiation Pattern Improvement of Patch Antennas Using Compact Soft Surface StructuresRaman KanaaNoch keine Bewertungen

- Theory and Analysis of Leaky Coaxial Cables With Periodic SlotsDokument10 SeitenTheory and Analysis of Leaky Coaxial Cables With Periodic SlotsSamruddha ThakurNoch keine Bewertungen

- Coverage Evaluations in TunnelsDokument16 SeitenCoverage Evaluations in TunnelsRaúl Domínguez BastidasNoch keine Bewertungen

- Hollow Rectangular WaveguideDokument6 SeitenHollow Rectangular Waveguidemoluewli100% (1)

- RF and Microwave Systems IntroductionDokument38 SeitenRF and Microwave Systems IntroductionAbdul Hafiz AnuarNoch keine Bewertungen

- Progress in Studies of Transients Analysis Method of Multiconductor Transmission LinesDokument5 SeitenProgress in Studies of Transients Analysis Method of Multiconductor Transmission LinesKushtrim MalaNoch keine Bewertungen

- Assignment 4awpDokument10 SeitenAssignment 4awpbrgaming656Noch keine Bewertungen

- CSD HCMUT Chapter5 - 6 2012Dokument65 SeitenCSD HCMUT Chapter5 - 6 2012nhungdieubatchotNoch keine Bewertungen

- GSM TDMA Engineering OptimizationDokument20 SeitenGSM TDMA Engineering OptimizationvcaswellNoch keine Bewertungen

- Phase 2 ReportDokument59 SeitenPhase 2 ReportMurugeswariNoch keine Bewertungen

- Minimisation of Crosstalk in VLSI Routing: Chandrajit Pal University of Calcutta Spring 2010Dokument35 SeitenMinimisation of Crosstalk in VLSI Routing: Chandrajit Pal University of Calcutta Spring 2010KAMARUDHEEN KPNoch keine Bewertungen

- An Ten ADokument13 SeitenAn Ten At.sin48Noch keine Bewertungen

- Aperture Antenna DéignDokument4 SeitenAperture Antenna DéignCuongNoch keine Bewertungen

- Transmission Overview-Final11Dokument173 SeitenTransmission Overview-Final11Anonymous ITG3EeNNoch keine Bewertungen

- Modeling of Power Line Communications Using MIMO Coding Scheme For Indoor SystemDokument11 SeitenModeling of Power Line Communications Using MIMO Coding Scheme For Indoor SystemNoorianah LollmahamodNoch keine Bewertungen

- Coax 2 Formal LabReportDokument15 SeitenCoax 2 Formal LabReportAndres MavareNoch keine Bewertungen

- Introduction to Microstrip AntennasDokument205 SeitenIntroduction to Microstrip AntennasDipole AntennaNoch keine Bewertungen

- Fast Prediction of Transmission Line Radiated Emissions Using The Hertzian Dipole Method and Line-End Discontinuity ModelsDokument9 SeitenFast Prediction of Transmission Line Radiated Emissions Using The Hertzian Dipole Method and Line-End Discontinuity ModelsJuanNoch keine Bewertungen

- Rectangular Patch Antenna Performance FeedsDokument13 SeitenRectangular Patch Antenna Performance FeedsyaswanthNoch keine Bewertungen

- Huang Slides 6V08Dokument49 SeitenHuang Slides 6V08Shanaz AmanNoch keine Bewertungen

- Overspread Digital Transmission Over Wireless Linear Time-Varying MIMO SystemsDokument13 SeitenOverspread Digital Transmission Over Wireless Linear Time-Varying MIMO SystemsRaghavendra Prasad ReddyNoch keine Bewertungen

- Low Power Design and Simulation of 7T SRAM Cell Using Various Circuit TechniquesDokument6 SeitenLow Power Design and Simulation of 7T SRAM Cell Using Various Circuit TechniquesseventhsensegroupNoch keine Bewertungen

- A Novel Periodic CPW UWB Low Pass Filter With Large Rejected BandDokument8 SeitenA Novel Periodic CPW UWB Low Pass Filter With Large Rejected BandFa Mido ChemseddineNoch keine Bewertungen

- Strip LineDokument9 SeitenStrip LineMikeLesterCalolotNoch keine Bewertungen

- 2013 Broadband Characterization of On-Chip RF Spiral Inductor Using Multi-Line TRL CalibrationDokument4 Seiten2013 Broadband Characterization of On-Chip RF Spiral Inductor Using Multi-Line TRL CalibrationPhạmThanhSơnNoch keine Bewertungen

- IEEE Transactions on Microwave Filters ReviewedDokument20 SeitenIEEE Transactions on Microwave Filters Reviewedalokcena007Noch keine Bewertungen

- (SPRO (ADAIUG6December: Nca0Iieigu0IappuDokument4 Seiten(SPRO (ADAIUG6December: Nca0Iieigu0IappuAbhineet KumarNoch keine Bewertungen

- Tunable Microwave and Millimeter-Wave Band-Pass Filters: Jaroslaw Uher, and Wolfgang J. R. HoeferDokument11 SeitenTunable Microwave and Millimeter-Wave Band-Pass Filters: Jaroslaw Uher, and Wolfgang J. R. HoeferJeenert Espinoza ValenzuelaNoch keine Bewertungen

- Ultra-Wideband Coplanar-Fed Monopoles: A Comparative Study: Jana JILKOVÁ, Zbyněk RAIDADokument6 SeitenUltra-Wideband Coplanar-Fed Monopoles: A Comparative Study: Jana JILKOVÁ, Zbyněk RAIDAabdo-dzNoch keine Bewertungen

- Femtocell Macrocell Interference Analysis For Mobile WiMAX SystemDokument5 SeitenFemtocell Macrocell Interference Analysis For Mobile WiMAX Systemsameh04Noch keine Bewertungen

- An Efficient Layout Style For ThreeDokument12 SeitenAn Efficient Layout Style For Threejhchon2000Noch keine Bewertungen

- Conradi Probe ExercisesDokument13 SeitenConradi Probe ExercisesEray ArıkNoch keine Bewertungen

- Lower-Power: LayoutDokument11 SeitenLower-Power: LayoutmturadagiNoch keine Bewertungen

- Alpha Particle Effect On Multi-Nanosheet Tunneling Field-Effect Transistor at 3-nm Technology NodeDokument11 SeitenAlpha Particle Effect On Multi-Nanosheet Tunneling Field-Effect Transistor at 3-nm Technology Node전종욱Noch keine Bewertungen

- RF PlanarDokument6 SeitenRF PlanarVishal ManwaniNoch keine Bewertungen

- MOS Integrated Circuit DesignVon EverandMOS Integrated Circuit DesignE. WolfendaleNoch keine Bewertungen

- Signal Integrity: From High-Speed to Radiofrequency ApplicationsVon EverandSignal Integrity: From High-Speed to Radiofrequency ApplicationsNoch keine Bewertungen

- Teaching Digital Signal Processing Using PSpice PDFDokument6 SeitenTeaching Digital Signal Processing Using PSpice PDFbhushanchittaragiNoch keine Bewertungen

- ASCO, A SPICE Circuit Optimizer Written by Jo ̃o RamosDokument78 SeitenASCO, A SPICE Circuit Optimizer Written by Jo ̃o RamosbhushanchittaragiNoch keine Bewertungen

- ASCO, A SPICE Circuit Optimizer Written by Jo ̃o RamosDokument78 SeitenASCO, A SPICE Circuit Optimizer Written by Jo ̃o RamosbhushanchittaragiNoch keine Bewertungen

- Ngspice ManualDokument564 SeitenNgspice ManualbhushanchittaragiNoch keine Bewertungen

- Ngspice ManualDokument564 SeitenNgspice ManualbhushanchittaragiNoch keine Bewertungen

- LM5007 High Voltage (80V) Step Down Switching Regulator: FeaturesDokument17 SeitenLM5007 High Voltage (80V) Step Down Switching Regulator: FeaturesbhushanchittaragiNoch keine Bewertungen

- Ngspice ManualDokument564 SeitenNgspice ManualbhushanchittaragiNoch keine Bewertungen

- CMOS Transistor Layout KungFuDokument39 SeitenCMOS Transistor Layout KungFuAyo Iji100% (5)

- Dimensions in MM (Inches) .: TO39 (TO205AD) PinoutsDokument2 SeitenDimensions in MM (Inches) .: TO39 (TO205AD) PinoutsoiraviniciusNoch keine Bewertungen

- Us 5113363Dokument21 SeitenUs 5113363bhushanchittaragiNoch keine Bewertungen

- 1.5 The Modulus of A Number: - This Is Known As TheDokument1 Seite1.5 The Modulus of A Number: - This Is Known As ThebhushanchittaragiNoch keine Bewertungen

- Transistor LevelsDokument8 SeitenTransistor LevelsbhushanchittaragiNoch keine Bewertungen

- Ups Technical OverwiewDokument51 SeitenUps Technical Overwiewlug21100% (1)

- DiscoverDokument16 SeitenDiscoverEmmanuelNoch keine Bewertungen

- LCR-Meter ElektorDokument5 SeitenLCR-Meter ElektorFernando VidalNoch keine Bewertungen

- Semitic Music Theory 2600-500 BCDokument82 SeitenSemitic Music Theory 2600-500 BCmedeskiwood1Noch keine Bewertungen

- Basic Satellite Telecom Theory and Concepts: Arabsat, EscDokument74 SeitenBasic Satellite Telecom Theory and Concepts: Arabsat, EscElfatih HashimNoch keine Bewertungen

- Rock Hill ChristmasVille EventsDokument5 SeitenRock Hill ChristmasVille EventsEmma KoryntaNoch keine Bewertungen

- IPTV Channels GuideDokument19 SeitenIPTV Channels GuideEugenio HernánNoch keine Bewertungen

- 40E3500ADokument53 Seiten40E3500Asamsularief03Noch keine Bewertungen

- 10 Las Abejas (The Bees) : Agustin Barrios Mangore (1885-1944)Dokument3 Seiten10 Las Abejas (The Bees) : Agustin Barrios Mangore (1885-1944)chenchenNoch keine Bewertungen

- Your Name High-Hillsong Worship-This Is Our God.ADokument4 SeitenYour Name High-Hillsong Worship-This Is Our God.AAndres Felipe Suarez GualdronNoch keine Bewertungen

- O Holy Night Choral Sheet MusicDokument4 SeitenO Holy Night Choral Sheet MusicMhel Andrew Valbuena MelitanteNoch keine Bewertungen

- 317 East 32nd Street - Lead SheetDokument2 Seiten317 East 32nd Street - Lead SheetSteinar RefsdalNoch keine Bewertungen

- Aleix AlbaredaCVeng04-2013Dokument3 SeitenAleix AlbaredaCVeng04-2013aleixalbaredaNoch keine Bewertungen

- Filipino Folk DancesDokument8 SeitenFilipino Folk DancesLadie VelascoNoch keine Bewertungen

- Auditorium Seating CollectionDokument13 SeitenAuditorium Seating CollectionVivek MishraNoch keine Bewertungen

- Sandvik Crusher Qe341 Operators ManualDokument22 SeitenSandvik Crusher Qe341 Operators Manualstephennelson021099xsc100% (126)

- AM Broadcasting BasicsDokument5 SeitenAM Broadcasting BasicsRavi LimayeNoch keine Bewertungen

- Week 6 Living With ArtistDokument25 SeitenWeek 6 Living With ArtistGrechen CabusaoNoch keine Bewertungen

- 78#bluetooth Based Smart Sensor Networks Sree Man ColDokument24 Seiten78#bluetooth Based Smart Sensor Networks Sree Man ColPraveen Puthuparambil0% (1)

- Anger - The Modern Enharmonic Scale As The Basis of The Chromatic Element in MusicDokument62 SeitenAnger - The Modern Enharmonic Scale As The Basis of The Chromatic Element in MusicGregory MooreNoch keine Bewertungen

- Insight into Rossini's The Thieving Magpie OvertureDokument2 SeitenInsight into Rossini's The Thieving Magpie OvertureNektarNoch keine Bewertungen

- Mobile Communications Chapter 3: Media AccessDokument25 SeitenMobile Communications Chapter 3: Media AccessKumar VivekNoch keine Bewertungen

- Blues People Negro Music in White AmericaDokument47 SeitenBlues People Negro Music in White Americajazzclub78% (9)

- SM Pre-Show Check List Example 1Dokument1 SeiteSM Pre-Show Check List Example 1Gabrielle SilveroliNoch keine Bewertungen

- Philips 200p7Dokument107 SeitenPhilips 200p7IvaneWahyuHidayatNoch keine Bewertungen

- CPARDokument2 SeitenCPARNei QuiNoch keine Bewertungen

- 24-GHz Microstrip Grid Array Antenna For Automotive Radar ApplicationsDokument3 Seiten24-GHz Microstrip Grid Array Antenna For Automotive Radar ApplicationsWesley GeorgeNoch keine Bewertungen

- Design of TeslaDokument4 SeitenDesign of TeslaSaahib ReddyNoch keine Bewertungen

- Fairy Tail Sad ThemeDokument2 SeitenFairy Tail Sad ThemeSymphonic100% (1)

- Unit 5 - Surround and 3D Sound SystemsDokument124 SeitenUnit 5 - Surround and 3D Sound SystemsJavier BledaNoch keine Bewertungen

- Web TV Kanali 07-01-2020 PDFDokument1 SeiteWeb TV Kanali 07-01-2020 PDFFaris BegicNoch keine Bewertungen