Beruflich Dokumente

Kultur Dokumente

Spi Datasheet

Hochgeladen von

Anees UllahOriginalbeschreibung:

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Spi Datasheet

Hochgeladen von

Anees UllahCopyright:

Verfügbare Formate

Nios SPI

January 2003, Version 2.1

Data Sheet

General Description

The Nios serial peripheral interface (SPI) module is an Altera SOPC Builder library component included in the Nios development kit. The SPI module is a simple, industry standard communications interface commonly used in embedded systems. Many semiconductor manufacturers sell a variety of sensor, conversion, and control devices that use an SPI. The SOPC Builder SPI library component has available system choices to define device logic and interface signals on the Nios development board. The SPIs Verilog HDL or VHDL source code is available for development and includes the necessary software subroutines for easy system integration. The Nios SPI peripheral is 3-wired and can be used as either a master or slave device. It allows software to communicate with one or more external devices over an SPI bus. Software controls and communicates with the SPI peripheral through five memory-mapped, 16-bit registers accessed by a standard Nios peripheral bus connection. When configured as a master device, the SPI can interface with up to 16 independent SPI slave devices.

Functional Description

The SPI peripheral extends the conventional protocol by allowing more than one external SPI peripheral to share the same miso, mosi, and sclk pins. Each SPI peripheral instantiated within a Nios system has at least four interface signals (that is, physical I/O pins on the Altera programmable logic device): miso, mosi, sclk, and ss_n. Master devices interfacing with multiple SPI slave devices have one ss_n signal for each slave device. The function of these signals depends on whether the SPI peripheral is operating as a master or slave device.

Altera Corporation

DS-NIOSSPI-2.1

Nios SPI Data Sheet

Table 1 lists pin names, numbers, and types for both master and slave configurations. Table 1. Pin Descriptions Pin Polarity Name

miso mosi sclk ss_n High High Low

Master Device Number of Pins

1 1 1 116

Slave Device Number of Pins

1 1 1 1

Pin Type

Input Output Output Output

Pin Type

Output Input Input Input

The miso (master in, slave out) signal carries synchronous data from the slave to the master device. The mosi (master out, slave in) signal carries synchronous data from the master to the slave device. The sclk signal is driven by the master, synchronizing all data transfers. Each SPI slave device has one ss_n signal. The ss_n signal is an active-low slave input/master output pin. Slave devices do not respond to transactions unless their ss_n input signal is driven low. 1 Typical SPI peripherals set their miso output pinswhen not selectedto high impedance. The Altera-provided SPI slave peripheral drives an undefined value on its miso output pin when not selected. If an SPI slave device is connected to an external (off-chip) SPI master device, the select input can be used to control a tri-state pin outside the Nios system module. This option is necessary when multiple slave devices share the same SPI bus.

The SPI peripheral can be used in conjunction with the DMA peripheral to allow streaming data transfers between the SPI and memory.

See the Nios DMA Data Sheet for details on the DMA library component. The SPI peripheral consists of these user-visible components: I I A memory-mapped register space (software interface) SPI bus interface pins (hardware interface to other SPI devices)

The register control bits determine when data can be read from and written to the memory-mapped registers. All data is transmitted via the SPI bus interface pins, miso, mosi, sclk, and ss_n.

Altera Corporation

Nios SPI Data Sheet

Master Mode Operation

The SPI peripheral operates as a master device if it is configured as such in the PTF at design time. In general, the SPI protocol does not support multi-master systems. The master initiates all data transactions, and every transaction is both a receive and transmit operation. The master device transmits a new data bit on the mosi pin and the slave device drives a new data bit on the miso pin on each active clock edge. The SPI peripheral transmitter logic consists of an n-bit (where n is a value from 1 to 16) txdata transmit holding register and an n-bit transmit shift register (the number of data bits is determined by the databits PTF assignment). Software starts an SPI transaction by writing a transmit-data value to the txdata register. The transmit shift register directly feeds the mosi data pin. Data is shifted out to mosi either least significant bit (LSB) first or most significant bit (MSB) first, depending on the lsbfirst PTF assignment. The transmit shift register is loaded automatically from the txdata register whenever a serial transmit shift operation is not currently in process. 1 The transmit shift register and the txdata register provide double buffering during data transmission; that is, software can write a new value into the txdata register while the previously written character is being shifted out of the transmit shift register.

The SPI peripheral receive logic consists of an n-bit (where n is a value from 116) rxdata receive holding register and an n-bit receive shift register (the number of data bits is determined by the databits PTF assignment). The rxdata receive holding register is read directly by software. The receive shift register is fed directly by the miso data pin. The rxdata holding register is loaded from the receive shift register automatically every time data is fully received. 1 The receive shift register and the rxdata register provide double buffering during data receiving; that is, the rxdata register can hold a previously received data byte while the subsequent data byte is being shifted into the receive shift register.

Software can monitor the status of a master write operation by reading the trdy, tmt, and toe bits in the status register. Similarly, software can monitor the status of a slave read operation by reading the roe and rrdy bits in the status register.

Altera Corporation

Nios SPI Data Sheet

Slave Mode Operation

The SPI peripheral slave device behaves similarly to the master device, except it cannot initiate a data transaction. Before a transaction begins, the slave device polls its ss_n pin waiting for the pin to be driven low, which indicates the device is being addressed by an SPI master device. The SPI slave device immediately begins sending the transmit shift register contents to the miso pin. The slave device also reads the receive shift register simultaneously, polling for data on the mosi pin. Thus, a read and write transaction are carried out simultaneously.

SPI Registers

Software controls the SPI peripheral by reading from and writing to memory-mapped registers inside the Altera device. Table 2 shows a register map for SPI master and slave devices with an n-bit transmit/receive shift register operating as master and slave devices.

Table 2. SPI Register Map A2..A0 Register Name

rxdata txdata status

(1)

R/W 15...

RO WO RW RW RW

sso

(2)

Description/Register Bits 10 9 8 7 6 5 4 3 2 1 0

0 1 2 3 4 5 Notes

(1) (2)

rxdata(n-1..0) txdata(n-1..0) e ie rrdy irrdy trdy itrdy tmt toe itoe roe iroe

control reserved slaveselect

Present only on master Slave select maskpresent only on master

A write operation to the status register clears the roe, toe, and e bits. Only for SPI masters.

rxdata Register

Software reads received data from the rxdata register. When new data is fully received via the miso input, the status registers rrdy bit is set to 1 and the data is transferred into the rxdata register. When software reads a value from the rxdata, the status registers rrdy bit is cleared. If data is transferred into the rxdata register when the rrdy bit is set (that is, when software has not retrieved the previous data), a receive-overrun error occurs and the status registers roe bit is set to 1. New data is always transferred into the rxdata register, whether or not software retrieved the previous data.

Altera Corporation

Nios SPI Data Sheet

Writing data to the rxdata register has no effect.

txdata Register

Software writes data to be transmitted directly into the txdata register. Data should not be written to the txdata register until the transmitter is ready for new data, as indicated by the status registers trdy bit. If data is written to the txdata register when trdy is 0, a toe error is generated and the contents of the txdata register are undefined. The trdy bit is set to 0 whenever software writes data into the txdata register. The trdy bit is set to 1 when data is transferred from the txdata register into the transmitter shift register, indicating an empty txdata holding register. For example, assume that the SPI peripheral is idle and software writes data into the txdata holding register. During the idle phase, the trdy bit is set to 0, but after the data is transferred into the transmitter shift register, trdy is immediately set to 1. Software begins writing a second data byte into the txdata register, and again the trdy bit is set to 0. However, this time the original data byte is still in the process of being transmitted over the serial mosi pin. Accordingly, the trdy bit remains at 0 until the transaction cycle ends. When the cycle ends, the second data byte is transferred into the transmitter shift register and the trdy bit is again set to 1.

status Register

The status register consists of bits that indicate particular conditions inside the SPI peripheral. The status register can be read at any time by software, and doing so does not change the value of any of the bits. Each bit is associated with a corresponding interrupt-enable bit in the control register, as discussed in control Register on page 7. If a status bits corresponding interrupt-enable bit equals 1 at the same time the status bit equals 1, an interrupt request is sent to software.

Altera Corporation

Nios SPI Data Sheet

The status register bits are shown in Table 3: Table 3. status Register Bits Bit Number Bit Name

3 4 5 6 7 8 roe toe tmt trdy rrdy e

Description

Receive overrun error. Transmitter overrun error. Transmitter shift register empty. Transmitter ready. Receive ready. Error

roe Bit

The roe bit is set to 1 if data is received while the rxdata register is full (that is, while the rrdy bit is set to 1). If the receive overrun error (ROE) occurs, the new data overwrites the old. The roe bit is set to 0 when software performs a write operation to the status register.

toe Bit

The toe bit is set to 1 when data is written to txdata while the register is still full (that is, while the trdy bit is set to 0). If the transmitter overrun error (TOE) occurs, the new data is ignored. The toe bit is set to 0 when software performs a write operation to the status register.

tmt Bit

The tmt bit is set to 0 while a transaction is in progress and set to 1 when the shift register is empty.

trdy Bit

The trdy bit is set to 1 when the txdata register is empty.

rrdy Bit

The rrdy bit is set to 1 when the rxdata register is full.

e Bit

The e bit is set to 1 when either toe or roe is set. This is a convenience for the programmer. The e bit is set to 0 when software performs a write operation to the status register.

Altera Corporation

Nios SPI Data Sheet

control Register

The control register consists of data bits that control the SPI peripherals internal operation. Each bit in the control register enables an interrupt for the corresponding bit in the status register. The value in the control register can be read at any time by software. The control register bits are shown in Table 4: Table 4. control Register Bits Bit Number

3 4 6 7 8 10

Bit Name

iroe itoe itrdy irrdy ie sso

Description

Enable interrupt for a receive overrun error. Enable interrupt for a transmitter overrun error. Enable interrupt for a transmitter ready. Enable interrupt for a receiver ready. Enable interrupt for an error. Override SS_n output.

The control bits iroe, itoe, itrdy, irrdy, and ie allow software to determine which, if any, of the SPI peripherals internal conditions result in an interrupt request. Each bit in the status register has a corresponding interrupt-enable bit at the same bit position in the control register (see SPI Register Map on page 4). For example, the status registers bit 7 is rrdy, and the control registers corresponding bit 7 is irrdy (interrupt-enable, receiver ready). For each status register bit, an interrupt request to software is generated if both the status bit and its corresponding interrupt-enable bit are set to 1. Bit 10 of the control register, sso, does not enable an interrupt source. Instead, it can be used to force the SS_n output or outputs active at any time. sso can be used to transmit or receive data of arbitrary size on the SPI link. See Figure 1 on page 8 for an example that demonstrates sending 24-bit data over an 8-bit SPI master. 1 The received data is read, but not saved, which is not strictly necessary, but avoids receive overrun errors.

Altera Corporation

Nios SPI Data Sheet

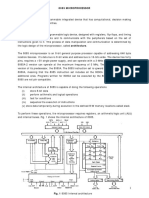

Figure 1: Code Example for sso Control Register

// Force SS_n active: na_spi_0-> np_spicontrol |= np_spicontrol_sso_mask; for (i = 0; i < 3; ++i) { // Transmit a byte: while (!(na_spi_0->np_spistatus & np_spistatus_trdy_mask)); na_spi_0->np_spitxdata = data[i]; // Read and throw away the received data: while (!(na_spi_0->np_spistatus & np_spistatus_rrdy_mask)); na_spi_0->np_spirxdata; } // Wait until the last byte is transmitted: while (!(na_spi_0->np_spistatus & np_spistatus_tmt_mask)); // Release SS_n: na_spi_0-> np_spicontrol &=~np_spicontrol_sso_mask;

slaveselect Register

The slaveselect register sets the select bit mask for slave devices driven by the SPI bus master device. The slaveselect register is only present when the SPI peripheral is configured as a master device. The slaveselect register can be used to address up to 16 slave devices by setting the corresponding bit. For example, to select slave device 0, bit 0 in the slaveselect register must be set to 1. The SPI master device can also interface to multiple slave devices simultaneously by setting the slaveselect bits for each desired device. For example, to select slave devices 1, 5, and 6, the slaveselect register bits 1, 5, and 6 must be set to 1. 1 Exercise caution when selecting multiple slaves simultaneously. Contention may result on the miso pin.

A reset sets bit 0 and clears every other bit of the slaveselect register. Thus, after a device reset, slave device 0 is automatically selected.

Software Data Structure

typedef volatile struct { int np_spirxdata; int np_spitxdata; int np_spistatus; int np_spicontrol; int np_spireserved; int np_spislaveselect; } np_spi;

// // // // // //

Read-only, 1-16 bit Write-only, 1-16 bit Read-only, 9-bit Read/Write, 9-bit reserved Read/Write, 1-16 bit, master only

Altera Corporation

Nios SPI Data Sheet

Software Subroutines

Table 5 lists the SPI software subroutines available in the Nios library (lib directory in the custom SDK) when one or more SPI peripherals are present in the Nios system. These functions are declared in the include file nios.h. Table 5. SPI Software Subroutines Subroutine

nr_spi_rxchar nr_spi_txchar

Description

Reads a character from the SPI peripheral whose address is passed as an argument. Sends a single character to the SPI peripheral whose address is passed as an argument.

nr_spi_rxchar

This subroutine reads a character from the SPI peripheral whose address is passed as pSPI.

Syntax

int nr_spi_rxchar(np_spi *pSPI);

Parameter

The pSPI parameter is a pointer to the SPI peripheral.

nr_spi_txchar

This subroutine sends a single character, i, to the SPI peripheral whose address is passed as pSPI.

Syntax

int nr_spi_txchar(int i, np_spi *pSPI);

Parameters

Parameter

i pSPI

Description

Character to be sent Pointer to the SPI peripheral

Altera Corporation

Nios SPI Data Sheet

PTF Assignments

Table 6 lists the SPIs PTF parameters. Detailed descriptions follow the table.

Table 6. SPI PTF Parameters Parameter

clock_freq ismaster databits targetclock numslaves clockpolarity clockphase lsbfirst extradelay targetssdelay delayunits clockunits Notes

(1) The Section column describes the parameters location in the PTF: S/WSA = SYSTEM/WIZARD_SCRIPT_ARGUMENTS M/WSA = MODULE/WIZARD_SCRIPT_ARGUMENTS

Section(1)

S/WSA M/WSA M/WSA M/WSA M/WSA M/WSA M/WSA M/WSA M/WSA M/WSA M/WSA M/WSA

Type

Integer Boolean Integer Integer Integer Integer Integer Boolean Boolean Decimal String String

Allowed Values x1

1, 0 1 .. 16 >0 1 .. 16 1, 0 1, 0 1, 0 1, 0

Default

33333000 1 8 128 1 0 0 0 0 100 us kHz

Units

Hz bits kHz bits seconds

0

ns, us, ms, s MHz, kHz, Hz

clock_freq

The clock_freq assignment is the global system clock frequency. This setting is derived from the system PTF, and is not set by SOPC Builder.

ismaster

When ismaster is set to 1, the SPI peripheral is a master device. When ismaster is set to 0, the SPI peripheral is a slave device.

databits

The databits assignment determines the SPI peripherals send and receive size. That is, it sets the number of bits transmitted or received by the SPI peripheral. The databits assignment also determines the rxdata and txdata register sizes. For a master and slave SPI to work together, databits must have the same value for both peripherals.

10

Altera Corporation

Nios SPI Data Sheet

targetclock

The targetclock assignment determines the SPI peripherals target clock frequency. The SPI devices actual frequency may not actually be the targetclock value. The only possible values for the achieved clock frequency are: ( <system clock frequency> ) [ 2, 4, 6, 8, ] The actual frequency achieved will not be greater than the targetclock value, based on the system frequency specified. For example, if the system clock frequency is 33333000 Hz and the targetclock value is 16000000 Hz, then the actual clock frequency is 8333250 Hz, or a clock divisor of 4 (because a clock divisor of 2 would create a clock frequency greater than 16,000,000 Hz). 1 When ismaster is set to 0, this assignment is ignored.

numslaves

The numslaves assignment determines the number of slaves a master can address. For every slave specified, a chip select pin is added to the SPI master peripheral. 1 When ismaster is set to 0, this assignment is ignored.

clockpolarity

When clockpolarity is 1, the clocks idle state is high. When clockpolarity is 0, the clocks idle state is low.

clockphase

When clockphase is 0, data is latched on the SPI clocks leading edge, and data changes on the SPI clocks trailing edge. When clockphase is 1, data is latched on the SPI clocks trailing edge, and data changes on the SPI clocks rising edge. Figure 2 through Figure 5 on page 12 illustrate the SPI pins possible behaviors based on the clockpolarity and clockphase values.

Altera Corporation

11

Nios SPI Data Sheet

Figure 2. clockpolarity = 0, clockphase = 0

SS_n SCLK DATA_OUT MSB LSB

Figure 3. clockpolarity = 0, clockphase = 1

SS_n SCLK DATA_OUT MSB LSB

Figure 4. clockpolarity = 1, clockphase = 0

SS_n SCLK DATA_OUT MSB LSB

Figure 5. clockpolarity = 1, clockphase = 1

SS_n SCLK DATA_OUT MSB LSB

lsbfirst

When lsbfirst is set to 1, data is transferred LSB-first. When lsbfirst is set to 0, data is transferred MSB-first.

extradelay

When extradelay is set to 1, a master SPI peripheral inserts a delay between the falling edge of a chip select to a slave peripheral and the first shift transaction, as shown: Figure 6. extradelay=1

SS_n SCLK

12

Altera Corporation

Nios SPI Data Sheet

When extradelay is set to 1, the targetssdelay assignment is enabled. 1 When ismaster is set to 0, this assignment is ignored.

targetssdelay

The targetssdelay assignment determines how much extra delay a master SPI peripheral requires between the falling edge of a chip select to a slave peripheral and the first shift transaction. The SPI peripheral, however, utilizes a delay granularity equal to SPI clock period. Thus, the actual ssdelay is the targetssdelay rounded up to the nearest multiple of the SPI clock period, as shown in the following equation: p = sclk_period ; delay = t arg etssdelay p ---------------------------------p sclk_period is the period of the sclk frequency. See targetclock on page 11 for details. 1 When either ismaster or extradelay are set to 0, this assignment is ignored.

delayunits

The delayunits assignment determines the unit of measure to be used for the targetssdelay assignment.

clockunits

The clockunits assignment determines the unit of measure to be used for the targetclock assignment.

Altera Corporation

13

Nios SPI Data Sheet

101 Innovation Drive San Jose, CA 95134 (408) 544-7000 http://www.altera.com Applications Hotline: (800) 800-EPLD Literature Services: lit_req@altera.com 14

Copyright 2003 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, mask work rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Alteras standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Altera Corporation

Das könnte Ihnen auch gefallen

- Digilent ChipKIT SPI LibraryDokument8 SeitenDigilent ChipKIT SPI LibrarySalvador MoralesNoch keine Bewertungen

- Unit - Iv Syllabus 8051 MicrocontrollerDokument52 SeitenUnit - Iv Syllabus 8051 MicrocontrollerSakthivel Palani100% (1)

- SPI Using The Rabbit Clocked Serial Ports: SPI I/O SignalsDokument9 SeitenSPI Using The Rabbit Clocked Serial Ports: SPI I/O SignalsYaseen Ghulam100% (3)

- Welcome To International Journal of Engineering Research and Development (IJERD)Dokument7 SeitenWelcome To International Journal of Engineering Research and Development (IJERD)IJERDNoch keine Bewertungen

- Short NotesDokument14 SeitenShort NotesAman Ethio LijNoch keine Bewertungen

- Serial Pheripheral InterfaceDokument12 SeitenSerial Pheripheral InterfaceK.R.RaguramNoch keine Bewertungen

- Serial Peripheral InterfaceDokument5 SeitenSerial Peripheral InterfaceabhinavbitNoch keine Bewertungen

- Unit 5 - Microprocessor & Its Application - WWW - Rgpvnotes.inDokument12 SeitenUnit 5 - Microprocessor & Its Application - WWW - Rgpvnotes.inPrayag ParasharNoch keine Bewertungen

- Tutorial - How To Use SPI in TI F28335 TargetDokument19 SeitenTutorial - How To Use SPI in TI F28335 TargetReginey BarbosaNoch keine Bewertungen

- Embedded SystemsDokument9 SeitenEmbedded SystemsqasdfghjklwertyNoch keine Bewertungen

- Universal Asynchronous Receiver/Transmitter: April 2011 Reference Design 1011Dokument11 SeitenUniversal Asynchronous Receiver/Transmitter: April 2011 Reference Design 1011rishi_lvNoch keine Bewertungen

- Serial Communication With 8051Dokument25 SeitenSerial Communication With 8051prakriti sankhlaNoch keine Bewertungen

- An Over View of 8085Dokument12 SeitenAn Over View of 8085nskprasad89Noch keine Bewertungen

- Shift Registrs and UartDokument13 SeitenShift Registrs and UartSarath ChandraNoch keine Bewertungen

- Unit 4Dokument48 SeitenUnit 4formyywork17Noch keine Bewertungen

- Dspic33 SpiDokument30 SeitenDspic33 Spidanielrb18Noch keine Bewertungen

- Read Me Slave 2.1Dokument7 SeitenRead Me Slave 2.1Prasad VylaleNoch keine Bewertungen

- Uart, Spi & I2cDokument12 SeitenUart, Spi & I2cdeepakacharya424Noch keine Bewertungen

- A Microcontroller Is A Small Computer On A Single Integrated Circuit Containing A Processor CoreDokument40 SeitenA Microcontroller Is A Small Computer On A Single Integrated Circuit Containing A Processor CoreranaNoch keine Bewertungen

- Architecture and Instruction SetDokument50 SeitenArchitecture and Instruction SetVantharAlaNoch keine Bewertungen

- Microprocessor 8085 NotesDokument48 SeitenMicroprocessor 8085 NotesDewal ChaturvediNoch keine Bewertungen

- Unit 5 - Microprocessor & Its Application - WWW - Rgpvnotes.inDokument13 SeitenUnit 5 - Microprocessor & Its Application - WWW - Rgpvnotes.inJayesh JoshiNoch keine Bewertungen

- Labview Serial CommunicationDokument0 SeitenLabview Serial Communicationmajidkhan04Noch keine Bewertungen

- Mic Project ReportDokument11 SeitenMic Project ReportDivya BansodeNoch keine Bewertungen

- Serial Peripheral Interface (SPI)Dokument5 SeitenSerial Peripheral Interface (SPI)Benin JacobNoch keine Bewertungen

- 2.1 LPC2129 Microcontroller: 2.1.1 FeaturesDokument14 Seiten2.1 LPC2129 Microcontroller: 2.1.1 FeaturesBhaskar Rao PNoch keine Bewertungen

- MPMC Unit 2Dokument31 SeitenMPMC Unit 2nikitaNoch keine Bewertungen

- SPI ProtocolDokument2 SeitenSPI ProtocolMohanNoch keine Bewertungen

- Ch17 Spi Protocol and Max7221 Display InterfacingDokument51 SeitenCh17 Spi Protocol and Max7221 Display InterfacingSimple knowledgeNoch keine Bewertungen

- Mo MC 3 ChapDokument21 SeitenMo MC 3 ChapHarsha MkrNoch keine Bewertungen

- Symax ProtocolDokument13 SeitenSymax ProtocolCesar Garcia100% (2)

- MY BOOK For MicroprocessorDokument53 SeitenMY BOOK For Microprocessorbharat patelNoch keine Bewertungen

- Using The Serial Peripheral Interface (SPI) Module On 68HC (9) 08 MicrocontrollersDokument8 SeitenUsing The Serial Peripheral Interface (SPI) Module On 68HC (9) 08 MicrocontrollersJackson Dias RochaNoch keine Bewertungen

- Peripheral Interfacing: 1 Parallel Interface AdapterDokument5 SeitenPeripheral Interfacing: 1 Parallel Interface Adapteratmroo9Noch keine Bewertungen

- Answers of Microprocessor (8085) & Electronics FAQDokument21 SeitenAnswers of Microprocessor (8085) & Electronics FAQsoumyadev100% (23)

- Serial Peripheral Interface in DSP: by Nayana Soni & Neha RajputDokument19 SeitenSerial Peripheral Interface in DSP: by Nayana Soni & Neha RajputNeha RajputNoch keine Bewertungen

- Microprocessor Lab Manual EE0310Dokument44 SeitenMicroprocessor Lab Manual EE0310sathishkumar.vNoch keine Bewertungen

- 8P-ESP8266 I2S Module Description en v1.0Dokument12 Seiten8P-ESP8266 I2S Module Description en v1.0zaleksNoch keine Bewertungen

- MC8085Dokument7 SeitenMC8085Bhavani BhavanNoch keine Bewertungen

- Risabh Tyagi Rithik PrakashDokument16 SeitenRisabh Tyagi Rithik PrakashSuryadev Kumar SinhaNoch keine Bewertungen

- Micro U1Dokument43 SeitenMicro U1Avinash SharmaNoch keine Bewertungen

- Notes Unit 1Dokument25 SeitenNotes Unit 1Ashish YadavNoch keine Bewertungen

- ScriptkoDokument3 SeitenScriptkolaarnie graceNoch keine Bewertungen

- SPI EmbeddedDokument16 SeitenSPI EmbeddedSrivatsanNoch keine Bewertungen

- SPI ProtocolDokument8 SeitenSPI Protocolpraveenbc100% (2)

- 8085 MaterialDokument12 Seiten8085 MaterialsameerNoch keine Bewertungen

- College of Electronics Technology Bani Walid: Presented By: Mohamed Awad Mohamed AbolobaidhDokument10 SeitenCollege of Electronics Technology Bani Walid: Presented By: Mohamed Awad Mohamed AbolobaidhMohammedAwadAlwarfleNoch keine Bewertungen

- SCBDokument5 SeitenSCBAshok ChakravarthyNoch keine Bewertungen

- 8051 MicrocontrollerDokument7 Seiten8051 Microcontrollersabin3sNoch keine Bewertungen

- UART ArchitectureDokument23 SeitenUART ArchitectureEdgar Mugabi Tusuubira100% (4)

- 8051 Microcontroller ArchitectureDokument3 Seiten8051 Microcontroller Architecturenirmal_inboxNoch keine Bewertungen

- SPI-openlog - User ManualDokument5 SeitenSPI-openlog - User ManualsavantzpcdmaNoch keine Bewertungen

- Spi ModuleDokument13 SeitenSpi ModuleMuhammadSaeedTahir100% (2)

- Millman Halkias - Integrated ElectronicsDokument28 SeitenMillman Halkias - Integrated ElectronicsPranav SinhaNoch keine Bewertungen

- MPDokument34 SeitenMPAbhinandan JainNoch keine Bewertungen

- SDA - Serial Data, SCL - Serial ClockDokument10 SeitenSDA - Serial Data, SCL - Serial ClockPavan Kulkarni100% (3)

- Viva Questions and Answers in MP Lab - 1Dokument6 SeitenViva Questions and Answers in MP Lab - 1Sai KrishnaNoch keine Bewertungen

- CISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkVon EverandCISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkNoch keine Bewertungen

- IDOC Process in SAP:: EventsDokument2 SeitenIDOC Process in SAP:: EventsPrateek0% (1)

- Time Table Summer Term Exam 2023 - Revised05.07.2023Dokument2 SeitenTime Table Summer Term Exam 2023 - Revised05.07.2023vivek meenaNoch keine Bewertungen

- DL Unit 4 NotesDokument21 SeitenDL Unit 4 NotesMynapati PrasudhaNoch keine Bewertungen

- OO Analysis and Design and UMLDokument9 SeitenOO Analysis and Design and UMLMayank SharmaNoch keine Bewertungen

- Unit 5 Software Development, Design and Testing: StructureDokument24 SeitenUnit 5 Software Development, Design and Testing: StructureAnonymous bTh744z7E6Noch keine Bewertungen

- Visual Basic and AutoCAD PDFDokument672 SeitenVisual Basic and AutoCAD PDFRajendra K KarkiNoch keine Bewertungen

- Chapter 14 ProjectsDokument9 SeitenChapter 14 ProjectsDeepakKattimaniNoch keine Bewertungen

- Fundamentals of Programming - Chapter#5Dokument62 SeitenFundamentals of Programming - Chapter#5thunderbeastakNoch keine Bewertungen

- Digital Base1 - HandbookDokument23 SeitenDigital Base1 - HandbookKeerthi SenthilNoch keine Bewertungen

- Session 14 - 15 - Introduction MongoDBDokument29 SeitenSession 14 - 15 - Introduction MongoDBTrung NguyễnNoch keine Bewertungen

- Hakin9 TBO 04 2013Dokument121 SeitenHakin9 TBO 04 2013Maria Belen LopezNoch keine Bewertungen

- Onlinefiletools Logo Https://Onlinefil Online CSV Toolsonline TSV Toolsonline Json Toolsonline Yaml Toolsonlinexml ToolsonlineDokument23 SeitenOnlinefiletools Logo Https://Onlinefil Online CSV Toolsonline TSV Toolsonline Json Toolsonline Yaml Toolsonlinexml ToolsonlineglabolhumarNoch keine Bewertungen

- Bit3202 Internet Programming Regular Reg SuppDokument4 SeitenBit3202 Internet Programming Regular Reg Suppashleykiki.keNoch keine Bewertungen

- Bca 402Dokument4 SeitenBca 402Tapamalya SanyalNoch keine Bewertungen

- HAAS - Kiwicon7-Automating Advanced XPath Injection Attacks PDFDokument39 SeitenHAAS - Kiwicon7-Automating Advanced XPath Injection Attacks PDFTesty testyNoch keine Bewertungen

- 58-Browser Tests (Laravel Dusk) - Laravel - The PHP Framework For Web ArtisansDokument24 Seiten58-Browser Tests (Laravel Dusk) - Laravel - The PHP Framework For Web ArtisansMomo Semerkhet0% (1)

- ST 20 ProgramingDokument212 SeitenST 20 PrograminggatopanNoch keine Bewertungen

- Presentation On Hybrid Application Development at IT Himalaya Pvt. LTDDokument11 SeitenPresentation On Hybrid Application Development at IT Himalaya Pvt. LTDDhiraj JhaNoch keine Bewertungen

- iOS Developer - KavyaDokument4 SeiteniOS Developer - KavyaMadhav GarikapatiNoch keine Bewertungen

- Transcad: Managing Data TablesDokument16 SeitenTranscad: Managing Data TablesjhonNoch keine Bewertungen

- TAFJ UnitTestFrameworkDokument35 SeitenTAFJ UnitTestFrameworkMrCHANTHANoch keine Bewertungen

- Oracle Final TestDokument16 SeitenOracle Final TestRoxana Drăguţescu100% (2)

- CIS 103 Study GuideDokument13 SeitenCIS 103 Study GuideguidodiorNoch keine Bewertungen

- DebugDokument12 SeitenDebugSebastian IvanovNoch keine Bewertungen

- Bee31101 Lab2 v20142015Dokument17 SeitenBee31101 Lab2 v20142015api-317625367Noch keine Bewertungen

- Strings AssignmentDokument3 SeitenStrings AssignmentDAKSH SACHDEVNoch keine Bewertungen

- Odb2vtk User GuideDokument3 SeitenOdb2vtk User GuideSandy YansikuNoch keine Bewertungen

- HEC-RAS 507 UnsteadyDokument9 SeitenHEC-RAS 507 Unsteadykendo_tNoch keine Bewertungen

- BCS 031 PDFDokument37 SeitenBCS 031 PDFGurjeet KaurNoch keine Bewertungen

- 1.create Chat Application Using Either TCP or UDP Protocol.: Server CodeDokument10 Seiten1.create Chat Application Using Either TCP or UDP Protocol.: Server CodeKevin VaghasiyaNoch keine Bewertungen