Beruflich Dokumente

Kultur Dokumente

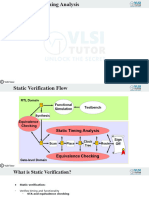

Timing Analysis

Hochgeladen von

genx142Originalbeschreibung:

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Timing Analysis

Hochgeladen von

genx142Copyright:

Verfügbare Formate

Timing Analysis

Introduction

The goal of timing analysis is to verify that a design meets timing requirements under a specified set of timing constraints, such as arrival and required times, operating conditions, slew rates, false paths, and path delays. Performing timing analysis lets you determine how fast a design can run without incurring timing violations. You can use the results of timing analysis to fine tune and debug the speed-limiting, critical paths in a design Where timing analysis is used in the flow:

Procedure

Before running timing analysis, read in the timing libraries, timing constraints, and the netlist. 1. Prior to running timing analysis, set your desired mode setting using setAnalysisMode. To select timing type of on-chip variation use: setAnalysisMode -analysisType onChipVariation For more information, see command setAnalysisMode in the "Timing Analysis Commands" chapter of the Encounter Digital Implementation System Text Command Reference. 2. The timeDesign command encapsulates several sub-commands to run extraction, delay calculation and timing analysis. The command generates several types of timing reports based on the options that you choose. The common timeDesign options are: {-prePlace | -preCTS | -postCTS | -postRoute [-si] | -signoff[-si] | -reportOnly[-si]} Use the options to specify the state of the design when you run timing analysis. These options determine the default extraction and delay calculaton engines which will be used for generating the timing reports. For more information, see command timeDesign in the "Timing Analysis Commands" chapter of the Encounter Digital Implementation System Text Command Reference. 3. Use the following command to generate an aggregated timing report on the entire design after detailed routing. By default the detailed timing reports are saved in directory ./timingReports or the directory that you specify using the -outDir parameter. timeDesign -postRoute -outDir postRoute_timing When no path groups are defined, timeDesign will report a summary table based on temporarily created reg2reg, in2reg, reg2out, in2out and clkgate path groups. When at least one path group is created, timeDesign will report a summary table based on the path group

Nov 01, 2010 11:01

Copyright 2010, Cadence Design Systems, Inc. All rights reserved.

By default, timeDesign reports setup timing. To report hold checks, -hold option needs to be used. timeDesign -hold For Multi-Mode Multi-Corner (MMMC) designs, timeDesign reports the timing for each active analysis view, as well as an aggregated summary. 4. Use command report_timing to generate timing reports on specific paths. You can use the -format option to customize the report fields

Examples

To generate an aggregated timing report summary prior to CTS, use the following command. This command runs Trial Route, native default extraction, and timing analysis to generate timing reports before clock tree synthesis: timeDesign -preCTS The following example shows an aggregated summary report generated by timeDesign:

The following command ignores the net load and runs timing analysis before the design is placed. timeDesign -prePlace The following commands use native detailed extraction and timing analysis to generate timing reports for both setup and hold after the design has been routed. timeDesign -postRoute timeDesign -postRoute -hold The following command runs timing analysis for signoff taking into account effects of signal integrity and using QRC engine for extraction: timeDesign -signoff -si

Nov 01, 2010 11:01

Copyright 2010, Cadence Design Systems, Inc. All rights reserved.

The following command specifies the use of existing extraction and timing analysis data to generate timing reports. When you use this parameter, the software does not run extraction or timing analysis; instead it uses data that is already in memory. timeDesign -reportOnly To generate a timing report on the most critical path which traces complete launch and capture clock paths, run the following command: report_timing -path_type full_clock You can use the -format parameter to customize which columns displayed when running command report_timing. Valid format columns are: adjustment, annotation, arc, arrival, cell, delay, direction, edge, fanin, fanout, incr_delay, instance, instance_location, load, locv_derate, net, phase, pin, hpin, pin_location, required, retime_delay, retime_slew, slew, stolen, and user_derate. To display columns: cell, delay, fanout, instance, load, net and slew, run the following command: report_timing -format {cell delay fanout instance load net slew} By default, the following columns are displayed when running report_timing: {instance arc cell delay arrival required} Alternatively, you can permanently set the desired columns using : set_global report_timing_format This will display the specified columns each time report_timing is called. For example: set_global report_timing_format {cell delay fanout instance load net slew} report_timing

Nov 01, 2010 11:01

Copyright 2010, Cadence Design Systems, Inc. All rights reserved.

Das könnte Ihnen auch gefallen

- Document ControlDokument42 SeitenDocument ControlRenoMasr83% (12)

- Frank/Vahid Embedded-Design Solution ManualDokument92 SeitenFrank/Vahid Embedded-Design Solution ManualPriyatam Kumar Kanak92% (25)

- Application Engine TracingDokument16 SeitenApplication Engine TracingnagasankarNoch keine Bewertungen

- Module 10 Generating and Running The Foundation Flow ScriptsDokument3 SeitenModule 10 Generating and Running The Foundation Flow ScriptsveeruNoch keine Bewertungen

- 10R80 Transmission IdentificationDokument2 Seiten10R80 Transmission Identificationmedicaluv60% (5)

- TCL 2 2015.00 LG 03Dokument8 SeitenTCL 2 2015.00 LG 03kehrenNoch keine Bewertungen

- Communication Matrix TemplateDokument3 SeitenCommunication Matrix TemplateNursula TaalaiNoch keine Bewertungen

- Inspection and Test Plan For Shell and Tube Heat ExchangerDokument2 SeitenInspection and Test Plan For Shell and Tube Heat Exchangeralokbdas100% (1)

- Introduction To Liberty - CCS, ECSM and NDLMDokument7 SeitenIntroduction To Liberty - CCS, ECSM and NDLMStudentNoch keine Bewertungen

- Shorts FixedDokument18 SeitenShorts FixedKirankumar ChavanNoch keine Bewertungen

- PTISTA SG Unit 06.exceptionsDokument24 SeitenPTISTA SG Unit 06.exceptionsAnonymous CTRhtz94Noch keine Bewertungen

- Sap PM End User Manual Breakdown MaintenanceDokument48 SeitenSap PM End User Manual Breakdown Maintenanceوسام توفيقNoch keine Bewertungen

- What Is Useful Skew and When We Use It ?Dokument7 SeitenWhat Is Useful Skew and When We Use It ?RAZNoch keine Bewertungen

- Addwelltap: ParametersDokument5 SeitenAddwelltap: ParameterssagarNoch keine Bewertungen

- Physical DesignDokument111 SeitenPhysical DesignanuhyaNoch keine Bewertungen

- File FormatsDokument24 SeitenFile Formatssravan100% (1)

- 10 Ways To Fix SETUP and HOLD Violation - Static Timing Analysis (STA) Basic (Part-8) - VLSI ConceptsDokument10 Seiten10 Ways To Fix SETUP and HOLD Violation - Static Timing Analysis (STA) Basic (Part-8) - VLSI ConceptsIlaiyaveni IyanduraiNoch keine Bewertungen

- Module 3 Extraction Timing Analysis Optmization and CTSDokument7 SeitenModule 3 Extraction Timing Analysis Optmization and CTSVenkateshNoch keine Bewertungen

- How Does The Clock Skew Violate Setup and Hold Time Contraints? What Are The Common Errors in Constraints?Dokument11 SeitenHow Does The Clock Skew Violate Setup and Hold Time Contraints? What Are The Common Errors in Constraints?Sai KumarNoch keine Bewertungen

- Timing ClosureDokument23 SeitenTiming ClosureSasank VenkataNoch keine Bewertungen

- 7 CLK Tree Synthesis PDFDokument64 Seiten7 CLK Tree Synthesis PDFpnaveen460Noch keine Bewertungen

- Open STADokument75 SeitenOpen STAEthan Mahintorabi100% (1)

- Ostrich RC CorrelationDokument41 SeitenOstrich RC CorrelationSrinivas Krishna100% (1)

- Dbget EDI10 PDFDokument26 SeitenDbget EDI10 PDFMahmood Vdn100% (1)

- PD Comand ObulDokument84 SeitenPD Comand Obuldinesh reddy100% (1)

- Optcts SetupDokument29 SeitenOptcts SetupsrajeceNoch keine Bewertungen

- Questions BankDokument47 SeitenQuestions Bank1am17ec014 ashnal ahmedNoch keine Bewertungen

- ALLtime SynthesisDokument18 SeitenALLtime SynthesisAgnathavasiNoch keine Bewertungen

- Synopsis Design Constraints: SDC Timing Constraints Clock ConstraintsDokument2 SeitenSynopsis Design Constraints: SDC Timing Constraints Clock ConstraintsHistPro WebNoch keine Bewertungen

- Pulsed Latch Timing Analysis: Product Version: Tempus 15.1 October, 2015Dokument21 SeitenPulsed Latch Timing Analysis: Product Version: Tempus 15.1 October, 2015Anshita AgarwalNoch keine Bewertungen

- Emcee ScriptDokument2 SeitenEmcee ScriptAzlan PspNoch keine Bewertungen

- Innovus Mixed Signal Implementation Update TrainingDokument22 SeitenInnovus Mixed Signal Implementation Update TrainingLu ROm100% (1)

- Clock Tree Synthesis - Why Clock Tree Synthesis Is Necessary - CSDN BlogDokument21 SeitenClock Tree Synthesis - Why Clock Tree Synthesis Is Necessary - CSDN BlogAgnathavasiNoch keine Bewertungen

- Checking The Timing Between Asynchronous Clock Group PathsDokument2 SeitenChecking The Timing Between Asynchronous Clock Group PathsmanojkumarNoch keine Bewertungen

- Net Delay Is Calculated Using Rs and CsDokument12 SeitenNet Delay Is Calculated Using Rs and CsemaNoch keine Bewertungen

- Scia Nemetschek - Tutorial ShellDokument55 SeitenScia Nemetschek - Tutorial ShellEugen DincuNoch keine Bewertungen

- FP To Route Commands ListDokument4 SeitenFP To Route Commands ListNishanth GowdaNoch keine Bewertungen

- Clock Opt OptoDokument5 SeitenClock Opt Optothulasi reddyNoch keine Bewertungen

- ICC2Design Planning01initial - DPDokument22 SeitenICC2Design Planning01initial - DPRAZNoch keine Bewertungen

- How Can I Exclude Registers From Check - Timing's No - Clock ReportDokument2 SeitenHow Can I Exclude Registers From Check - Timing's No - Clock ReportLoc Tran VinhNoch keine Bewertungen

- Secondary PG Routing Using NanoRouteDokument2 SeitenSecondary PG Routing Using NanoRoutepragya mitaNoch keine Bewertungen

- Synt&timeDokument33 SeitenSynt&timePavin KaNoch keine Bewertungen

- Script EncDokument3 SeitenScript EncpdnoobNoch keine Bewertungen

- INVS191 DBTCL LabsDokument66 SeitenINVS191 DBTCL LabsLu ROmNoch keine Bewertungen

- Ccopt DesignDokument2 SeitenCcopt DesignStudentNoch keine Bewertungen

- IC Compiler™ II Tool Invocation CommandsDokument5 SeitenIC Compiler™ II Tool Invocation CommandsThai NguyenNoch keine Bewertungen

- Clock Tree SynthesisDokument2 SeitenClock Tree Synthesisrazu100% (1)

- Global Routing: VLSI Physical Design: From Graph Partitioning To Timing ClosureDokument72 SeitenGlobal Routing: VLSI Physical Design: From Graph Partitioning To Timing ClosureGorantala Anil KumarNoch keine Bewertungen

- IcvrefmanDokument2.585 SeitenIcvrefmanSai GouthamNoch keine Bewertungen

- AOCVDokument9 SeitenAOCVcherry987100% (1)

- Min Period Violation in Vlsi - Google Search PDFDokument1 SeiteMin Period Violation in Vlsi - Google Search PDFManjesh Gowda0% (1)

- Ex 11Dokument10 SeitenEx 11Siam HasanNoch keine Bewertungen

- Digital Physical Design: Hierarchical and Low Power Implementation FlowsDokument37 SeitenDigital Physical Design: Hierarchical and Low Power Implementation Flowsprakashthamankar100% (2)

- 5.script To Report The Filler Cells in A DesignDokument2 Seiten5.script To Report The Filler Cells in A DesignmanojkumarNoch keine Bewertungen

- Icc - Basic CommandsDokument73 SeitenIcc - Basic CommandssatNoch keine Bewertungen

- Tutorial For Cadence Innovus Place & RouteDokument26 SeitenTutorial For Cadence Innovus Place & RouteNaveen KuramNoch keine Bewertungen

- Synthesis AlDokument7 SeitenSynthesis AlAgnathavasiNoch keine Bewertungen

- CCD CTSDokument55 SeitenCCD CTSAgnathavasiNoch keine Bewertungen

- Age, Lda: Lntroduction and LabDokument36 SeitenAge, Lda: Lntroduction and Labsandip sugandhiNoch keine Bewertungen

- Tempus Timing Signoff Solution Ds PDFDokument3 SeitenTempus Timing Signoff Solution Ds PDFSudheer Gangisetty0% (1)

- 2 PT M1612-SP3 ECODokument33 Seiten2 PT M1612-SP3 ECOmanojkumar100% (1)

- Understanding The UPF Power Domain and Domain Boundary - Mentor GraphicsDokument15 SeitenUnderstanding The UPF Power Domain and Domain Boundary - Mentor GraphicsmanojkumarNoch keine Bewertungen

- 3.script For Reporting The Number of Different Buffer References Used For Fixing Hold ViolationsDokument2 Seiten3.script For Reporting The Number of Different Buffer References Used For Fixing Hold ViolationsmanojkumarNoch keine Bewertungen

- Dbget EDI10Dokument26 SeitenDbget EDI10Raja Ravi SankarNoch keine Bewertungen

- Clock Tree SynthesisDokument7 SeitenClock Tree Synthesiskaushik vkNoch keine Bewertungen

- Basis ArticlesDokument11 SeitenBasis ArticlesKrishna PrasadNoch keine Bewertungen

- STA Prime TimeDokument125 SeitenSTA Prime TimeNishanth GowdaNoch keine Bewertungen

- VerilogDokument80 SeitenVeriloggenx142Noch keine Bewertungen

- Chip Finish Icc TCLDokument5 SeitenChip Finish Icc TCLgenx142Noch keine Bewertungen

- Focal - Opt - Icc.: DRC Violations That Remains After The Post-Route Optimization Performed by TheDokument4 SeitenFocal - Opt - Icc.: DRC Violations That Remains After The Post-Route Optimization Performed by Thegenx142Noch keine Bewertungen

- Trans Array (JAVA PROGRAM PDFDokument4 SeitenTrans Array (JAVA PROGRAM PDFAMRENDRA SINGHNoch keine Bewertungen

- Shortcut Keys ReferenceDokument4 SeitenShortcut Keys ReferenceVer BautistaNoch keine Bewertungen

- How To Use Parameterized Query in Excel Using Column As Parameter - Stack OverflowDokument5 SeitenHow To Use Parameterized Query in Excel Using Column As Parameter - Stack Overflowm13marleNoch keine Bewertungen

- Tech Questions in InterviewDokument176 SeitenTech Questions in InterviewGajarajakrishnan JanarthanamNoch keine Bewertungen

- Organization Study Of: HLL Lifecare LTDDokument20 SeitenOrganization Study Of: HLL Lifecare LTDGokulSbNoch keine Bewertungen

- EricDokument14 SeitenEricManuu MachangeNoch keine Bewertungen

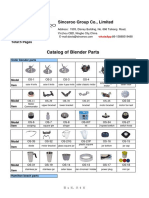

- Sinceroo Oster Blender PartsDokument5 SeitenSinceroo Oster Blender PartsEliecer Acosta ConyedoNoch keine Bewertungen

- Access AutomationDokument28 SeitenAccess AutomationEstuardo SierraNoch keine Bewertungen

- Preparation Resources Ead A 105Dokument1 SeitePreparation Resources Ead A 105Digital MapperNoch keine Bewertungen

- SubqueryDokument13 SeitenSubqueryHarsha PaniaNoch keine Bewertungen

- Modeling The Database Schema (Optional)Dokument19 SeitenModeling The Database Schema (Optional)parthascNoch keine Bewertungen

- Digital SignatureDokument14 SeitenDigital SignatureSatwik NagappaNoch keine Bewertungen

- DS 160 Introduction PowerPointDokument16 SeitenDS 160 Introduction PowerPointIsmael JibrinNoch keine Bewertungen

- Custom TopDokument4 SeitenCustom TopmaleemNoch keine Bewertungen

- R12 How To Use CPOI Token in FSGDokument3 SeitenR12 How To Use CPOI Token in FSGnghazalyNoch keine Bewertungen

- Role of User in ProjectsDokument13 SeitenRole of User in ProjectsdhotaremanishaNoch keine Bewertungen

- Real Time Face Based Detection and Tracking For Security SystemDokument10 SeitenReal Time Face Based Detection and Tracking For Security Systempalak AgarwalNoch keine Bewertungen

- CMD TricksDokument4 SeitenCMD TricksNarasimha ReddyNoch keine Bewertungen

- 24 PDFDokument2 Seiten24 PDFH Shamas MurtazaNoch keine Bewertungen

- Yed Graph Editor Manual: Import of Excel FilesDokument8 SeitenYed Graph Editor Manual: Import of Excel Filesmmrodrigo17Noch keine Bewertungen

- SynopsisDokument4 SeitenSynopsisLorina MendesNoch keine Bewertungen

- Javascript & DomDokument9 SeitenJavascript & DomAndrei UrsuleanuNoch keine Bewertungen

- Before Report Trigger InfoDokument2 SeitenBefore Report Trigger InfoRaam ValNoch keine Bewertungen