Beruflich Dokumente

Kultur Dokumente

Architecture Systemes Micro

Hochgeladen von

adil.prof3567Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Architecture Systemes Micro

Hochgeladen von

adil.prof3567Copyright:

Verfügbare Formate

ARCHITECTURE MATRIELLE DES SYSTMES MICROPROGRAMMS

COURS

PAGE 1 / 4

ARCHITECTURE MATRIELLE DES SYSTMES MICROPROGRAMMS

I. Objectifs

Savoir caractriser les bus dadresses et de donnes. Savoir dterminer la taille mmoire dun composant. Savoir dterminer les conditions de slection dun composant. Savoir dessiner et lire un plan mmoire.

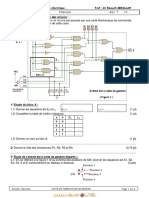

IV. Fonctions constituant larchitecture matrielle

Dans tous les systmes microprogramms on retrouve des fonctions similaires : Une unit de calcul appel MPU ou CPU. Une mmoire programme. Son contenu doit tre conserv en dehors de toute alimentation. Trs souvent elle nest accessible quen lecture (ROM). Une mmoire des variables accessibles en lecture et en criture (RAM) qui doit pouvoir recevoir les donnes du programme ainsi que la pile systme. Des circuits dentres et de sorties, spcialiss dans la communication avec les circuits lectroniques. Deux groupes dquipotentielles caractristiques appels bus dadresses et bus de donnes et un troisime groupe ddi au contrle.

II.

Constitution dun systme microprogramm

Le systme microprogramm comporte deux lments complmentaires indissociables : le programme qui dcrit la gestion du processus industriel. Le programme doit imprativement sadapter larchitecture du circuit lectronique quil est cens piloter. Le(s) circuit(s) lectronique(s) qui hberge(nt) le programme et lui donne vie.

V.

Bus de donnes, bus de contrle et bus dadresses.

Un bus est un ensemble de fils destin la communication entre les diffrents circuits. Il est reprsent par un trait gras. Les quipotentielles qui rentrent dans un bus ne sont pas relies aux autres. Par contre, toutes les quipotentielles portant la mme rfrence sont relies entre elles. Sur le schma ci-contre on distingue nettement deux bus : le bus dadresses et le bus de donnes. Les informations qui circulent sur les bus sont numriques.

III.

Exemple de systme microprogramm.

Un microcontrleur peut contenir un systme microprogramm complet (ex : 68HC11 de Motorola). Il nen est pas toujours ainsi et de nombreux systmes sont assembls de toutes pices. Exemple de systme microprogramm constitu autour dun microprocesseur MC6809 de Motorola :

A. Le bus de donnes

Le bus de donnes du schma ci-contre est constitu de 8 quipotentielles, cest donc un bus 8 bits. Les bits de ce bus sont reprs de D7 D0. Colorier en rouge le bus de donnes sur le schma ci-contre. Le nombre de valeurs possibles sur le bus de donnes est 28 = 256. Les valeurs transportes par le bus de donnes sont changes entre le microprocesseur et un autre composant. Les donnes peuvent transiter dans un sens ou dans lautre, le bus est dit bidirectionnel. Lorsque les donnes vont du microprocesseur au composant cela est appel une criture (le microprocesseur crit une donne dans une case mmoire ou dans un registre).

CRITURE

CPU

Bus de donnes

Mmoire

Lorsque les donnes vont du composant au microprocesseur cela est appel une lecture (le microprocesseur lit une donne dans une case mmoire ou dans un registre).

LECTURE

CPU

Bus de donnes

Mmoire

ARCHITECTURE MATRIELLE DES SYSTMES MICROPROGRAMMS

COURS

PAGE 2 / 4

B. Le bus de contrle

Le bus de contrle est souvent compos des fils suivants : CS (Chip Select) ou CE(Chip Enable) : Permet de signaler que le composant est slectionn et que les ordres quil reoit sur les autres fils lui sont destins. Cette entre est gnralement active au niveau bas. OE (Output Enable) : Permet de demander au composant de valider ses sorties, car les fils de donnes ont en gnral la particularit dtre trois tats (niveau bas, niveau haut ou haute impdance). Cette entre est gnralement active au niveau bas. RD/W (ReaD/Write) : Permet au microprocesseur dinformer un composant de la nature de lchange : lecture ou criture. La dnomination RD/W a pour signification : RD : ReaD, accs en lecture lorsque ce fil est ltat 1. /W : Write, accs en criture lorsque ltat est 0. Les composants qui sont relis au bus de donnes et qui sont relis RD/W sont accessibles en lecture et en criture. Quels sont ces composants ? IC4 (RAM) et IC5 (PIA : interface parallle). Les composants qui sont relis au bus de donnes et qui ne sont pas relis RD/W sont IC2 et IC3 (ROM) en lecture seulement. Quels sont ces composants ?

VI. Capacit mmoire dun composant A. Rappel de dfinitions

BIT : lment binaire (BInary digiT) qui peut prendre deux tats : 0 ou 1. MOT BINAIRE : groupe dtats binaires (fils dadresses, de donnes, contenu) reprsentant un nombre en base 2. OCTET : mot binaire de huit bits (se dit BYTE en anglo-saxon). POIDS BINAIRE : valeur associe au rang dun chiffre dans le nombre en base 2. MSB (Most Significant Bit) : bit de poids le plus fort du nombre. LSB (Least Significant Bit) : bit de poids le plus faible du nombre. KILO-x : dans le jargon informatique cest une sous unit de x qui ne vaut pas 1000 units x mais 1024 x (1024 = 210).

B. Calcul de capacit mmoire

La capacit mmoire est le nombre de cases mmoires de 1 bit contenu dans un composant mmoire. Soit a le nombre de fils dadresses et d le nombre de fils de donnes.

Bus dadresses de a fils 0000 0000 0000 0000 0000 0001 0000 0000 0010 Dd-1 X X X X Bus de donnes de d fils D4 D3 D2 D1 X X X X X X X X X X X X X X X X X X X X D0 X X X X

2a adresses diffrentes

Il suffit de calculer le nombre de cases mmoires de 1 bit.

1111 1111 1111

C. Le bus dadresses

Le bus dadresses du schma de la page 1 est constitu de 16 quipotentielles, cest donc un bus 16 bits. Les bits de ce bus sont reprs de A15 A0. Colorier en vert le bus dadresse du schma. Le nombre dadresses possibles est 2 = 65536. Il est donc possible dadresser 65536 cases mmoires de 8 bits (taille du bus de donnes). La premire adresse scrit : (0000 0000 0000 0000)2 = (0000)16 La dernire adresse scrit : (1111 1111 1111 1111)2 = (FFFF)16 Ce bus nest pas bidirectionnel. Il est en sortie pour le microprocesseur, cest lui qui dcide de ladresse, il est en entre pour les autres composants.

TOUJOURS 16

Puisque le nombre dadresses est 2a et qu chaque adresse correspond d bits de donnes, la capacit dune mmoire est d x 2a Soit en kilo-bits : d x 2a / 1024 = d x 2a / 210 = d x 2a-10 Soit en octets : d x 2a / 8 (2a pour un bus de donne de 8 bits) Soit en kilo-octets : d x 2a / (8 x 1024) (2a-10 pour un bus de donne de 8 bits) Exemple : Pour le systme microprocesseur de la page prcdente, donner la capacit mmoire des composants 2764 (ROM) : En nombre doctets : 213 = 8192 octets (2a car bus de donne de 8 bits) En nombre de kilo-octets : 23 = 8 kilo-octets (2a-10 car bus de donne de 8 bits) En nombre de bits : 8 x 213 = 65536 bits En nombre de kilo-bits : 8 x 23 = 64 kilo-bits Que peut-on dire de la capacit mmoire du composant 6264 (RAM) ? Il a la mme capacit mmoire car il a les mme nombre de fils dadresses et de donnes.

CPU

Bus dadresses

Mmoire

ARCHITECTURE MATRIELLE DES SYSTMES MICROPROGRAMMS

COURS

PAGE 3 / 4 Daprs la reprsentation normalise des composants IC2, IC3, IC4 et IC5, quels doivent tre les niveaux logiques prsents sur /ROM1, /ROM2, /RAM et /PIA pour que : Seul IC2 soit slectionn : Seul IC3 soit slectionn : Seul IC4 soit slectionn : Seul IC5 soit slectionn : /ROM1 = 0, /ROM2 = 1, /RAM = 1 et /PIA = 1 /ROM1 = 1, /ROM2 = 0, /RAM = 1 et /PIA = 1 /ROM1 = 1, /ROM2 = 1, /RAM = 0 et /PIA = 1 /ROM1 = 1, /ROM2 = 1, /RAM = 1 et /PIA = 0

VII. Dcodage dadresses

Chaque composant dune carte microprogramme doit tre accessible par le CPU. Par exemple, si le CPU est en train de sauvegarder une variable, il faut que le composant RAM soit slectionn et que les autres composants soient inhibs. Afin dordonner le systme, une plage dadresses est rserve chaque composant. La fonction ayant pour tche lattribution des adresses sappelle dcodage dadresses . Dans lexemple donn en premire page, le dcodage dadresses est ralis par un circuit spcialis : un dcodeur-dmultiplexeur 3 vers 8 (74138).

Dduire de la table de vrit du 74138 et des rsultats prcdents les niveaux logiques que devra appliquer le CPU sur A13, A14 et A15 pour slectionner : Complter la table de vrit du 74138 laide de votre Mmotech. Le composant PIA IC5 : Le composant RAM IC4 : A13 = 0, A14 = 0 et A15 = 0 A13 = 1, A14 = 0 et A15 = 0

Le composant ROM2 IC3 : A13 = 0, A14 = 1 et A15 = 1 Le composant ROM1 IC2 : A13 = 1, A14 = 1 et A15 = 1

Entres Valid G1 G2* C Slect. B A Y0 Y1 Y2

Sortie Y3 Y4 Y5 Y6 Y7

On remarque que les lignes dadresses de poids plus faibles (A12, A11 A0) ne participent pas la slection des composants. chaque combinaison {A15 ; A14 ; A13} correspond tout un ensemble dadresses. Complter le tableau suivant selon lexemple.

Bits dadresses

X L H H H H H H H H

*

H X L L L L L L L L

X X X X X X L L L L L H L H L L H H H L L H L H H H L H H H

H H L H H H H H H H

H H H L H H H H H H

H H H H L H H H H H

H H H H H L H H H H

H H H H H H L H H H

H H H H H H H L H H

H H H H H H H H L H

H H H H H H H H H L

Composant slectionn IC5 (PIA) IC4 (RAM) IC3 (ROM2) IC2 (ROM1)

Premire adresse Dernire adresse Premire adresse Dernire adresse Premire adresse Dernire adresse Premire adresse Dernire adresse

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

Code hexadcimal

0 0 0 0 1 1 1 1

0 0 0 0 1 1 1 1

0 0 1 1 0 0 1 1

X X 0 1 0 1 0 1

X X 0 1 0 1 0 1

X X 0 1 0 1 0 1

X X 0 1 0 1 0 1

X X 0 1 0 1 0 1

X X 0 1 0 1 0 1

X X 0 1 0 1 0 1

X X 0 1 0 1 0 1

X X 0 1 0 1 0 1

0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1

0000 000F 2000 3FFF C000 DFFF E000 FFFF

La taille dune plage dadresses de slection est tout simplement le nombre dadresses que lon peut crire entre sa premire et sa dernire adresse (comprise). La taille de la plage dadresses slectionne par /ROM1 est 213 (car 13 fils dadresses ne participent pas au dcodage.)

G2 = /G2A + /G2B

ARCHITECTURE MATRIELLE DES SYSTMES MICROPROGRAMMS La taille de la plage dadresses slectionne par /PIA est galement 213 pourtant il ny a que 24 adresses effectives pour le composant PIA. En effet seuls A0, A1, A2 et A3 sont relis ce composant, les fils A4 A12 sont donc indiffrents. On peut slectionner chaque adresse du PIA indiffremment avec les 29 combinaisons de A4 A12. On dit que ce composant 29 adresses images et quil sagit dun dcodage partiel. Pour les autres composants de la carte, tout le bus dadresses est utilis, il sagit donc dun dcodage complet. Remarque : Le dcodage dadresse nest pas forcement ralis par un dcodeurdmultiplexeur. Il peut tre galement effectu par un logigramme ou un circuit logique programmable (voir TD).

COURS

PAGE 4 / 4 Application : La reprsentation ci-contre est le plan mmoire du microcontrleur 68HC11A8 de Motorola.

VIII.

Plan mmoire

Cest une reprsentation graphique, un plan mmoire (en anglais memory map), de ce que le microprocesseur est susceptible de trouver telle ou telle adresse. Le plan mmoire est la traduction graphique du dcodage dadresses.

$0000

$0000

IC5 PIA

$1FFF $2000 $000F $0010

Zone dadresses de base du PIA 1re zone dadresses images

$001F $0020

IC4 RAM

$3FFF $4000

8Ko de RAM

Adresses inutilises

$5FFF $6000 $002F $0030

2re zone dadresses images 3re zone dadresses images

$003F

Quelles sont les adresses de dbut et de fin de la zone de RAM ? La zone RAM comporte combien dadresses ? Adresse de dbut : $0000 Adresse de fin : $00FF Soit 256 adresses (donc 256 octets car cest un microcontrleur 8 bits). Quelles sont les adresses de dbut et de fin de la zone de EEPROM ? La zone EEPROM comporte combien dadresses ? Adresse de dbut : $B600 Adresse de fin : $B7FF Soit 512 adresses (donc 512 octets car cest un microcontrleur 8 bits). Quelles sont les adresses de dbut et de fin de la zone de ROM (En dehors de la zone INTERRUPT VECTORS) ? La zone ROM comporte combien dadresses ? Adresse de dbut : $E000 Adresse de fin : $FFBF Soit 8128 adresses (donc 8128 octets car cest un microcontrleur 8 bits).

Adresses inutilises

$7FFF $8000

Adresses inutilises

$9FFF $A000 $1FF0

511re zone dadresses images

$1FFF

Adresses inutilises

$BFFF $C000

IC3 ROM2

$DFFF $E000

8Ko ROM2

IC2 ROM1

$FFFF

8Ko ROM1

16Ko de ROM au total

Plan mmoire dun systme 6809

Das könnte Ihnen auch gefallen

- 3 - Les Compteurs Integres AsynchronesDokument6 Seiten3 - Les Compteurs Integres AsynchronesAhmed BelhadjNoch keine Bewertungen

- CHAPITRE I Circuits Logiq Combinatoires PDFDokument28 SeitenCHAPITRE I Circuits Logiq Combinatoires PDFTimble PuteurNoch keine Bewertungen

- Chapitre II Architecture Générale D Un MicrocontroleurDokument22 SeitenChapitre II Architecture Générale D Un Microcontroleurfou100% (1)

- Conception Des Circuits Intégrés Prédiffusés Précaractérisés Et Sur Mesure v2010Dokument79 SeitenConception Des Circuits Intégrés Prédiffusés Précaractérisés Et Sur Mesure v2010Kaled Habib100% (1)

- Chapitre1 Microprocesseurs Et MicrocontroleursDokument14 SeitenChapitre1 Microprocesseurs Et Microcontroleursmanale bouderbalaNoch keine Bewertungen

- TTL Et CMOSDokument5 SeitenTTL Et CMOSEdgar ANDRIAMAHEFANoch keine Bewertungen

- Chapx Dma Stm32Dokument7 SeitenChapx Dma Stm32Wafa LakhdharNoch keine Bewertungen

- Cours Circuits Logiques ProgrammablesDokument72 SeitenCours Circuits Logiques ProgrammablesCompaore CédricNoch keine Bewertungen

- Cours VHDL S4Dokument48 SeitenCours VHDL S4MERYEM LAHBOUBNoch keine Bewertungen

- Micro 9Dokument22 SeitenMicro 9yahya hamdaniNoch keine Bewertungen

- Cours Architecture Aux MicrocontrôleursDokument49 SeitenCours Architecture Aux MicrocontrôleursDALII100% (1)

- Cours 1 Ère D Amplificateur OpérationnelDokument7 SeitenCours 1 Ère D Amplificateur OpérationnelSada DiopNoch keine Bewertungen

- Corrige TD Microcontroleur Pic 16f84Dokument11 SeitenCorrige TD Microcontroleur Pic 16f84HamdiHa92% (109)

- Les Compteurs Et Les Décompteurs.Dokument19 SeitenLes Compteurs Et Les Décompteurs.Khadija Ait MhamedNoch keine Bewertungen

- Devoir de Contrôle N°1 - Génie Électrique - Bac Technique (2012-2013) MR Abdallah RAOUAFI 2 PDFDokument4 SeitenDevoir de Contrôle N°1 - Génie Électrique - Bac Technique (2012-2013) MR Abdallah RAOUAFI 2 PDFMayouMohAmed100% (1)

- Devoir de Contrôle N°1 - Génie Électrique - Bac TechniqueDokument7 SeitenDevoir de Contrôle N°1 - Génie Électrique - Bac TechniqueAlaeddine Ben HassenNoch keine Bewertungen

- Circuits Logiques Séquentiels - LicDokument25 SeitenCircuits Logiques Séquentiels - LicHoucem B HsnNoch keine Bewertungen

- Electronique Numerique Cablée PDFDokument32 SeitenElectronique Numerique Cablée PDFHafid El GharosseNoch keine Bewertungen

- Page de Garde (Enregistré Automatiquement)Dokument3 SeitenPage de Garde (Enregistré Automatiquement)BerylNoch keine Bewertungen

- 2014 15 En208 TD1Dokument4 Seiten2014 15 En208 TD1YAHYA DbaghiNoch keine Bewertungen

- TP 1Dokument12 SeitenTP 1Usb MasNoch keine Bewertungen

- 2BACSTE - Pic 16F84 Et Pic 16F877 - RACHID BOUTSAIDDokument25 Seiten2BACSTE - Pic 16F84 Et Pic 16F877 - RACHID BOUTSAIDAFAD100% (1)

- Cours Systemes A MicroprocesseursDokument134 SeitenCours Systemes A MicroprocesseursKam ZegNoch keine Bewertungen

- Architecture Des OrdinateursDokument67 SeitenArchitecture Des Ordinateursmessem2009Noch keine Bewertungen

- FSMV1 IngDokument20 SeitenFSMV1 IngRachid BenrahouNoch keine Bewertungen

- CH 1Dokument20 SeitenCH 1raghda amamiNoch keine Bewertungen

- Travaux Pratiques: Electronique Numérique Avancée: Fpga - VHDLDokument39 SeitenTravaux Pratiques: Electronique Numérique Avancée: Fpga - VHDLMį Ņā ŘěťNoch keine Bewertungen

- Automate (API) 1Dokument10 SeitenAutomate (API) 1Mohamed BoucharebNoch keine Bewertungen

- Chapitre 2 - Familles Des Circuits Intégrés Numériques (Logiques)Dokument26 SeitenChapitre 2 - Familles Des Circuits Intégrés Numériques (Logiques)Ttech hackNoch keine Bewertungen

- Bascule (Circuit Logique)Dokument8 SeitenBascule (Circuit Logique)Maella AdjNoch keine Bewertungen