Beruflich Dokumente

Kultur Dokumente

Arquitectura Del Procesador X86

Hochgeladen von

Jean Paul PereaCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Arquitectura Del Procesador X86

Hochgeladen von

Jean Paul PereaCopyright:

Verfügbare Formate

Arquitectura del procesador X86

Arquitectura en pipeline Los procesadores previos al 8086, estaban limitados en su desempeo por la necesidad de realizar los dos pasos principales de ejecucin del procesador: Fetch/Execute, en forma secuencial. Es decir, no se puede ejecutar una instruccin hasta que se traiga de memoria (Fetch); y no podan traerse instrucciones de memoria mientras ejecutaba una instruccin, pues el procesador estaba ocupado. Resumiendo, un alto porcentaje del tiempo, el procesador estaba ocupado haciendo Fetch, cuando su funcin debiera ser ejecutar las instrucciones. La capacidad de ejecutar instrucciones slo se ocupaba en un bajo porcentaje.

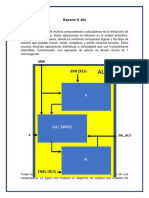

Para solucionar esto, Intel desarroll la arquitectura en pipeline del Fetch/Execute, en la cual simplemente se divide la tarea en dos secciones: una encargada del Fetch (BIU), y otra del Execute (EU). De esta manera, existen circuitos separados para cada funcin, los cuales trabajan en paralelo. Si bien el proceso an es secuencial, solamente al principio se requiere desperdiciar tiempo en el Fetch. A partir de ah, Fetch va adelante del Execute, y trae instrucciones al procesador mientras este ejecuta las anteriores.

BIU: Basic Interface Unit

El BIU es la parte del 8086 que se encarga de hacer el Fetch; es decir, su funcin es estar continuamente accesando la memoria, trayendo de ella las instrucciones para ser ejecutadas por el procesador. Contiene los siguientes elementos: 1.Los registros de segmentos 2.La cola de prefetch 3.El generador de direcciones fsicas 4.El Bus C Su funcionamiento es de la manera siguiente:

1. Registros de segmentos

Estos registros son localidades de 16 bits dedicados a las funciones de acceso a memoria. Se decidi, como se describir ms adelante al analizar el mecanismo de segmentacin, dividir el Megabyte de memoria al que puede accesar un 8086. Los registros de segmentos nos van a indicar qu seccin de memoria seleccionamos. Existen 4 registros de segmentos: DS: Data Segment (Segmento de Datos) Este registro selecciona una seccin de 64 Kb. que se dedica generalmente a colocar en ella nuestras variables, por lo cual toma su nombre: seccin de memoria dedicada a datos. CS: Code Segment (Segmento de Cdigo) Este registro selecciona el rea de 64 Kb. que generalmente dedicamos al cdigo. En este caso, el CPU (especficamente, el BIU), siempre toma las instrucciones de esta regin de memoria; por lo que cuando requerimos ms de 64 Kb. de cdigo (instrucciones), este registro tendr que moverse, tomando distintos valores segn recorremos distintas regiones de memoria. SS: Stack Segment (Segmento de Pila) Este registro selecciona la regin de 64 Kb. que va a contener la pila del sistema. Como su nombre lo indica, tendremos una estructura de datos, con poltica LIFO (Last In, First Out = El ltimo elemento en entrar, es el primero en salir), con instrucciones bsicas PUSH y POP para su manejo. Esta estructura es usada por los programas de aplicacin, pero tambin por el procesador para el control de instrucciones que lo requieren, tales como las llamadas a subrutinas yla atencin de interrupciones.

ES: Extra Segment (Segmento Extra) Este registro nos permite seleccionar una seccin de 64 Kb., que no est destinada a ningn uso especfico; por lo que el programador puede aplicarla como comodn, generalmente como un segundo segmento de datos; o bien, para el acceso a regiones de memoria del sistema, tales como la memoria de video o las variables del BIOS.

2. Cola de prefetch

Ya que el BIU trabaja en paralelo con el EU, requieren de un mecanismo para comunicarse. Esto se logra con una cola, estructura de datos que permite que el EU obtenga instrucciones para ejecutar en el mismo orden en que el BIU las coloc en la misma. As, el EU puede solicitar instrucciones en cuanto est listo para ejecutar la siguiente, sin importar en qu paso est el BIU en la obtencin de instrucciones; y viceversa, el BIU puede continuar su bsqueda de instrucciones, depositando la que acaba de obtener en la cola, sin importar si el EU en este momento est ocupado ejecutando.

3. Generador de direcciones fsicas

Como las direcciones son de 20 bits, y los registros que nos permiten accesarlas son de 16, se requiere de 2 registros para que en combinacin formen la direccin. Esta combinacin est basada en la arquitectura segmentada que veremos ms adelante. La funcin del generador de direcciones fsicas consiste en realizar esa combinacin, para lo cual contiene la circuitera necesaria para calcular la frmula: Direccin Fsica = Segmento * 0010h + Desplazamiento

4. Bus C

Este bus interno del procesador permite que la informacin fluya entre la interfaz con la memoria y los distintos elementos del BIU. Se requiere un bus independiente, para que la informacin que usa el EU no se interfiera con la que est procesando el BIU.

EU: Execution Unit

El EU es la parte del 8086 que Contiene los siguientes elementos: 1.Unidad de control 2.Registros de propsito general 3.Registros de ndice 4.ALU 5.Registro de Banderas 6.Bus A

Unidad de Control

Es la seccin del procesador que contiene la lgica de funcionamiento del mismo; es decir, esta circuitera gobierna el comportamiento de los distintos elementos en el procesador, coordinando los procesos de Fetch y Execute, as como las distintas microoperaciones necesarias para la ejecucin. Por tanto, tiene dos funciones principales: Generar la secuencia de estados del procesador, lo que logra gracias a la ejecucin del microcdigo.

Decodificar las instrucciones, determinando as los pasos para su ejcucin

Registros de Propsito general

Son 4 registros de 16 bits, que el programador usar para una diversidad de funciones. Tienen varias caractersticas en comn: Pueden ejecutar la mayora de las operaciones del procesador, incluyendo la generalidad de las instrucciones aritmticas y lgicas, salvo la multiplicacin y divisin. Se dividen lgicamente en 2 registros de 8 bits cada uno, llamados parte alta y parte baja; refirindose el registro de parte baja a los bits 0-7 (menos significativos) y la parte alta a los bits 8-15 (ms significativos). Pueden conectarse a los registros de segmentos; de hecho, siempre se har acceso a los registros de segmento a travs de un registro de propsito general, o de la pila.

Los 4 registros tienen su nombre propio y ciertas especializaciones: AX: Registro de acumulador Este registro es el ms usado, siendo de propsito general; y tiene ciertas especializaciones, de ah su nombre: Es el nico que puede ser usado como multiplicando en la multiplicacin Es el nico que puede ser usado como dividendo en la divisin Es el parmetro que selecciona los distintos servicios Operativo, usados mediante el mecanismo de Interrupciones. del Sistema

BX: Registro de Base Este registro, adems de las caractersticas generales de los registros de propsito general, se especializa en el acceso a memoria en combinacin con los registros de ndice, especialmente para el manejo de arreglos. CX: Registro de Contador Este registro, como su nombre indica, ser ampliamente usado como contador. Puede ser usado como cualquier registro de propsito general, pero tiene capacidades especiales para ser usado en instrucciones: de manejo de ciclos como contador en los corrimientos de manejo de memoria y strings DX: Registro de Datos Este registro de propsito general tiene como especializaciones: Formar con AX nmeros de 32 bits, siendo en este caso la parte ms significativa. El acceso a puertos. Las instrucciones IN y OUT, que permiten dicho acceso, requerirn en ciertos casos que el nmero de puerto est en DX.

Registros de ndice

Estos registros, de 16 bits, son muy similares a los de propsito general, pero no tienen todas las capacidades de los mismos; en particular:

No pueden conectarse directamente con los registros de segmentos. No pueden verse como dos registros de 8 bits (parte alta y parte baja).

Ahora bien, tienen sus propias habilidades. Especficamente, estn diseados para combinarse con los registros de segmento, ser usados como desplazamientos y as intervenir en el acceso a memoria. Se les usa, por ello, para el acceso a arreglos o como apuntadores. Los 4 registros que se consideran en este grupo son: SI: Source Index, o Apuntador a la Fuente Este registro se especializa en el acceso a bytes o words dentro del segmento de datos; existen instrucciones que lo toman por defecto como el registro que apunta a una localidad de memoria que se va a leer, por lo cual toma su nombre. DI: Destination Index, Apuntador al Destino Este registro se especializa en el acceso a bytes o words dentro del segmento de datos o el extra; existen instrucciones que lo toman por defecto como el registro que en combinacin con el ES apunta a una localidad de memoria que se va a escribir, por lo cual toma su nombre. BP: Base Pointer, o apuntador a la Base de la Pila. Este registro es usado para accesar, dentro del segmento de pila, la informacin. Principalmente nos permite determinar cuando hay un underflow, es decir, cuando se quiere sacar ms informacin de la pila que la que se ha colocado en ella; y el acceso a variables locales y parmetros. SP: Stack Pointer, o apuntador al tope de la Pila. Este registro tambin est siempre asociado al manejo de la pila. Su funcin especial es marcar el tope de la pila, y por tanto, indica en qu localidad de memoria se localiza la informacin de la pila; se incrementa cuando se hace un POP, con lo que apunta al siguiente elemento en la pila; y se decrementa al hacer un PUSH, con lo que controla el acceso a la memoria de la pila.

ALU: Unidad Aritmtica-Lgica

Este componente, como su nombre indica, contiene la circuitera necesaria para realizar las diversas operaciones aritmticas y lgicas. Recibe sus operandos por el Bus A, y genera los resultados regresndolos al mismo bus. Una particularidad que es importante recalcar es su conexin al registro de banderas, por lo cual todas las operaciones aritmticas y lgicas, de acuerdo a su resultado, lo alterarn.

Registro de Banderas

Este es un registro de 16 bits, usados como banderas. Esto quiere decir que cada uno de los bits seala un evento dentro del procesador; cuando el bit tiene un valor de 0, el evento no ocurri (falso); y cuando tiene un valor de

1, el evento mencionaremos:

ocurri

(verdadero).

Entre

las

banderas

ms

importantes

ZF: Bandera de resultado 0 Se prende cuando el resultado de la ltima operacin realizada en el ALU fue un 0. CF: Bandera de carry Se prende cuando el resultado de la ltima operacin realizada en el ALU (necesariamente, una suma o resta) gener un carry o un borrow. OF: Bandera de overflow Se prende cuando el resultado de la ltima operacin realizada en el ALU excedi la capacidad del registro donde se almacena (overflow). SF: Bandera de signo Se prende cuando el resultado de la ltima operacin realizada en el ALU fue negativo, segn la representacin de complemento a 2 que mencionamos en clases anteriores. AF: Bandera de carry auxiliar Se prende cuando el resultado de la ltima operacin realizada en el ALU gener un carry cuando estaba a la mitad. Por ejemplo, si sumamos dos nmeros de 16 bits, nos indicar si la suma de las partes bajas (primeros 8 bits) haba generado carry; si sumamos dos nmeros de 8 bits, indica si el resultado intermedio despus de sumar los 4 bits menos significativos, gener carry para sumarse a los bits 5. DF: Bandera de direccin A diferencia de las anteriores, esta bandera no se prende como resultado del ALU, sino que el programador la usa para controlar la direccin del acceso mediante apuntadores, especialmente en las instrucciones de strings. IF: Bandera de interrupcin Se prende cuando el procesador es interrumpido, y est ejecutando una rutina de atencin de interrupcin. Esto evita que el procesador acepte interrupciones mientras est procesando interrupciones previas, de manera que no se pierda el control del procesador.

Bus A

Este bus es el camino por el que viajan los datos dentro de la unidad de ejecucin, principalmente entre los registros y el ALU.

Manejo de Memoria: Segmentacin

Cuando Intel extendi el bus de direcciones, de 16 a 20 bits, se encontr con el problema de cmo asociar los registros con las direcciones de memoria. Para lograrlo, aplic un concepto ya usado antes en mainframes, conocido como segmentacin; en este modelo, se usan dos registros para seleccionar una localidad de memoria:

Registro de Segmento: indica en qu segmento (regin o seccin) de la memoria se encontrar la localidad deseada.

Registro de Desplazamiento: indica en qu desplazamiento, es decir, direccin relativa respecto al inicio de la seccin, se encontrar la localidad deseada.

Modos de direccionamiento del 8086/8088: Estos procesadores tienen 27 modos de direccionamiento (una cantidad bastante ms grande que los microprocesadores anteriores) o reglas para localizar un operando de una instruccin. Tres de ellos son comunes a microprocesadores anteriores: direccionamiento inmediato (el operando es un nmero que se encuentra en la misma instruccin), direccionamiento a registro (el operando es un registro del microprocesador) y direccionamiento inherente (el operando est implcito en la instruccin, por ejemplo, en la multiplicacin uno de los operandos siempre es el acumulador). El resto de los modos sirve para localizar un operando en memoria. Para facilitar la explicacin de estos modos, se pueden resumir de la siguiente manera: Deben sumarse cuatro cantidades: 1) direccin de segmento, 2) direccin base, 3) una cantidad ndice y 4) un desplazamiento. La direccin de segmento se almacena en el registro de segmento (DS, ES, SS o CS). En la prxima seccin se indica la forma en que se hace esto. Por ahora basta con saber que el contenido del registro de segmento se multiplica por 16 antes de utilizarse para obtener la direccin real. El registro de segmentacin siempre se usa para referenciar a memoria. La base se almacena en el registro base (BX o BP). El ndice se almacena en el registro ndice (SI o DI). Cualquiera de estas dos cantidades, la suma de las dos o ninguna, pueden utilizarse para calcular la direccin real, pero no pueden sumarse dos bases o dos ndices. Los registros restantes (AX, CX, DX y SP) no pueden utilizarse para direccionamiento indirecto. El programador puede utilizar tanto la base como el ndice para gestionar ciertas cosas, tales como matrices de dos dimensiones, o estructuras internas a otras estructuras, esquemas que se utilizan en las prcticas comunes de programacin. La base y el ndice son variables o dinmicas, ya que estn almacenadas en registros de la CPU. Es decir, pueden modificarse fcilmente mientras se ejecuta un programa. Adems del segmento, base e ndice, se usa un desplazamiento de 16 bits, 8 bits o 0 bits (sin desplazamiento). sta es una cantidad esttica que se fija al tiempo de ensamblado (paso de cdigo fuente a cdigo de mquina) y no puede cambiarse durante la ejecucin del programa (a menos que el programa se escriba sobre s mismo, lo que constituye una prctica no aconsejada). Todo esto genera los 24 modos de direccionamiento (considerando desplazamientos de 8 o 16 bits)a memoria que se ven a continuacin:

Registro indirecto: Basado:

[BX],

[DI].

[SI]. Desplazamiento [BP].

Desplazamiento [BX],

Indexado: Desplazamiento [SI], Desaplazamiento[DI]. Basado-indexado: [BX+SI], [BX+DI], [BP+SI], [BX+DI].

Basado-indexado con desplazamiento: Desplazamiento[BX+SI], Desplazamiento[BX+DI], Desplazamiento [BP+SI], Desplazamiento [BX+DI] Directo: [Desplazamiento].

Aqu desp8 indica desplazamiento de 8 bits y desp16 indica desplazamiento de 16 bits. Otras combinaciones no estn implementadas en la CPU y generarn error al querer ensamblar, por ejemplo, ADD CL,[DX+SI]. El ensamblador genera el tipo de desplazamiento ms apropiado (0, 8 16 bits) dependiendo del valor que tenga la constante: si vale cero se utiliza el primer caso, si vale entre -128 y 127 se utiliza el segundo, y en otro caso se utiliza el tercero. Ntese que [BP] sin desplazamiento no existe. Al ensamblar una instruccin como, por ejemplo, MOV AL,[BP], se generar un desplazamiento de 8 bits con valor cero. Esta instruccin ocupa tres bytes, mientras que MOV AL,[SI] ocupa dos, porque no necesita el desplazamiento. Estos modos de direccionamiento producen algunos inconvenientes en el 8086/8088. La CPU gasta tiempo calculando una direccin compuesta de varias cantidades. Principalmente esto se debe al hecho de que el clculo de direcciones est programado en microcdigo (dentro de la CROM del sistema de control de la unidad de ejecucin). En las siguientes versiones (a partir del 80186/80188) estos clculos estn cableados en la mquina y, por lo tanto, cuesta mucho menos tiempo el realizarlos. Veamos un ejemplo: MOV AL, ES:[BX+SI+6]. En este caso el operando de la izquierda tiene direccionamiento a registro mientras que el de la derecha indica una posicin de memoria. Poniendo valores numricos, supongamos que los valores actuales de los registros sean: ES = 3200h, BX = 200h, SI = 38h. Como se apunt ms arriba la direccin real de memoria ser: ES * 10h + BX + SI + 6 = 3200h * 10h + 200h + 38h + 6 = 3223Eh Estructura de memoria el 8086/8088 usa un correctamente a un direcciones de slo 16 de segmentacin: Como se ha mencionado anteriormente, esquema ingenioso llamado segmentacin, para acceder megabyte completo de memoria, con referencias de bits.

Veamos cmo funciona. Cualquier direccin tiene dos partes, cada una de las cuales es una cantidad de 16 bits. Una parte es la direccin de segmento y la otra es el offset. A su vez el offset se compone de varias partes: un desplazamiento (un nmero fijo), una base (almacenada en el registro base) y un ndice (almacenado en el registro ndice). La direccin de segmento se almacena en uno de los cuatro registros de segmento (CS, DS, ES, SS). El procesador usa estas dos cantidades de 16 bits para calcular la direccin real de 20 bits, segn la siguiente frmula: Direccin real = 16 * (direccin del segmento) + offset

Tal como veamos antes, dado que 16 en decimal es 10 en hexadecimal, multiplicar por ese valor es lo mismo que correr el nmero hexadecimal a la izquierda una posicin. Hay dos registros de segmento que tienen usos especiales: el microprocesador utiliza el registro CS (con el offset almacenado en el puntero de instruccin IP) cada vez que se debe acceder a un byte de instruccin de programa, mientras que las instrucciones que utilizan la pila (llamados a procedimientos, retornos, interrupciones y las instrucciones PUSH y POP) siempre utilizan el registro de segmento SS (con el offset almacenado en el registro puntero de pila SP). De ah los nombres que toman: CS es el segmento de cdigo mientras que SS es el registro segmento de pila. Para acceder a datos en la memoria se puede utilizar cualquiera de los cuatro registros de segmento, pero uno de ellos provoca que la instruccin ocupe un byte menos de memoria: es el llamado segmento por defecto, por lo que en lo posible hay que tratar de usar dicho segmento para direccionar datos. Este segmento es el DS (registro de segmento de datos) para todos los casos excepto cuando se utiliza el registro base BP. En este caso el segmento por defecto es SS. Si se utiliza otro registro, el ensamblador genera un byte de prefijo correspondiente al segmento antes de la instruccin: CS -> 2Eh, DS -> 3Eh, ES -> 26h y SS -> 36h. El uso de estos diferentes segmentos significa que hay reas de trabajo separadas para el programa, pila y los datos. Cada rea tiene un tamao mximo de 64 KBytes. Dado que hay cuatro registros de segmento, uno de programa (CS), uno de pila (SS) y dos de datos (segmento de datos DS y segmento extra ES) el rea de trabajo puede llegar a 4 * 64 KB = 256 KB en un momento dado suponiendo que las reas no se superponen. Si el programa y los datos ocupan menos de 64 KB, lo que se hace es fijar los registros de segmento al principio del programa y luego se utilizan diferentes offsets para acceder a distintas posiciones de memoria. En caso contrario necesariamente debern cambiarse los registros de segmento en la parte del programa que lo requiera. Los registros de segmento DS, ES y SS se cargan mediante las instrucciones MOV y POP, mientras que CS se carga mediante transferencias de control (saltos, llamadas, retornos, interrupciones) intersegmento.

Das könnte Ihnen auch gefallen

- Auditar La Actividad Usuarios SAMBA y LograteDokument4 SeitenAuditar La Actividad Usuarios SAMBA y LograteherschelmorenoNoch keine Bewertungen

- Custionario Hardware 2Dokument2 SeitenCustionario Hardware 2Roberto Sebastián Carvajal100% (3)

- Crear y utilizar Java beansDokument39 SeitenCrear y utilizar Java beansGiancarlo Gutierrez SotoNoch keine Bewertungen

- Diseño y Documentación de Un Esquema de DireccionamientoDokument4 SeitenDiseño y Documentación de Un Esquema de DireccionamientoAlison ReedNoch keine Bewertungen

- Asignación Contigua Vs No Contigua PDFDokument9 SeitenAsignación Contigua Vs No Contigua PDFZeus JeanNoch keine Bewertungen

- Laboratorio 2.8.3Dokument9 SeitenLaboratorio 2.8.3INGEMAR DAVID GONZALEZ VARGAS100% (1)

- Quiz Preguntas de Repaso CCNA2 1 3Dokument6 SeitenQuiz Preguntas de Repaso CCNA2 1 3richromeroNoch keine Bewertungen

- Monitoreo de Espacio en Disco Duro en MysqlDokument9 SeitenMonitoreo de Espacio en Disco Duro en MysqlCarlos CortésNoch keine Bewertungen

- LSDBDokument3 SeitenLSDBOlibel Z Herrera GarciaNoch keine Bewertungen

- Asertosy DisparadoresDokument20 SeitenAsertosy DisparadoresPeniel Ruiz0% (1)

- Proyecto CCNA4Dokument3 SeitenProyecto CCNA4felipemg16100% (2)

- Instalacion Informix LinuxDokument3 SeitenInstalacion Informix LinuxHenry Vivanco0% (1)

- 05-Planificacion Discos LinuxDokument23 Seiten05-Planificacion Discos LinuxAreTchENoch keine Bewertungen

- Desarrollo de Software Basado en ComponentesDokument16 SeitenDesarrollo de Software Basado en ComponentesJose Alfredo Roman CruzNoch keine Bewertungen

- Tarea 14 Algoritmo Snoopy y Protocolos de Memoria CacheDokument22 SeitenTarea 14 Algoritmo Snoopy y Protocolos de Memoria CacheMike OjedaNoch keine Bewertungen

- Recuperacion de Datos Por Falla Del Sistema de ArchivosDokument12 SeitenRecuperacion de Datos Por Falla Del Sistema de ArchivosGuillermo MuñozNoch keine Bewertungen

- Contadores Asíncronos, Síncronos Y Contadores Mod PDFDokument6 SeitenContadores Asíncronos, Síncronos Y Contadores Mod PDFgeko1Noch keine Bewertungen

- 3.2.1.3 Packet Tracer - Configuring EtherChannel Instructions - IG PDFDokument7 Seiten3.2.1.3 Packet Tracer - Configuring EtherChannel Instructions - IG PDFbart0x100% (1)

- 2 Enlace Troncal 8021Q+SURLEYDokument9 Seiten2 Enlace Troncal 8021Q+SURLEYJorge Alberto Delgado100% (1)

- Tablespace SysauxDokument2 SeitenTablespace SysauxEvyGlzNoch keine Bewertungen

- Partes Un Router CiscoDokument3 SeitenPartes Un Router CiscoLuis Jose Jiménez PeñaNoch keine Bewertungen

- CCNA 3 Cisco v5.0 Exámen FinalDokument34 SeitenCCNA 3 Cisco v5.0 Exámen FinalOsy HernándezNoch keine Bewertungen

- GUIA #9 Procedimientos AlmacenadosDokument7 SeitenGUIA #9 Procedimientos AlmacenadosJunior Huaman HuarhuaNoch keine Bewertungen

- Actividad Final Unidad 4 y 5Dokument6 SeitenActividad Final Unidad 4 y 5Zamuel CastilloNoch keine Bewertungen

- Algoritmo de PetersonDokument2 SeitenAlgoritmo de PetersonMayra0% (1)

- Actividad 5.3.4: Configuración de Las ACL ExtendidasDokument8 SeitenActividad 5.3.4: Configuración de Las ACL ExtendidasemersonNoch keine Bewertungen

- Replicación de Instantánea en SQL ServerDokument24 SeitenReplicación de Instantánea en SQL ServerBryan'sNcNoch keine Bewertungen

- Control de transacciones y concurrencia en bases de datosDokument35 SeitenControl de transacciones y concurrencia en bases de datosCélimo Rodriguez HerreraNoch keine Bewertungen

- Ejercicio OSPFDokument9 SeitenEjercicio OSPFGerman Arteaga RiosNoch keine Bewertungen

- Academia local de redes Cisco ESPOCH - Examen final CCNA SecurityDokument3 SeitenAcademia local de redes Cisco ESPOCH - Examen final CCNA SecurityJavier VallejoNoch keine Bewertungen

- Particiones en MYSQL PDFDokument6 SeitenParticiones en MYSQL PDFbigboss_310890Noch keine Bewertungen

- Practica U AluDokument5 SeitenPractica U AluAmigos LolerosNoch keine Bewertungen

- Informix Administracion LibreDokument160 SeitenInformix Administracion LibreFercho AlvarezNoch keine Bewertungen

- Registros de SegmentosDokument4 SeitenRegistros de SegmentosJ84C0% (1)

- Intraclase PH No.8Dokument7 SeitenIntraclase PH No.8Humberto CorreaNoch keine Bewertungen

- Actividad 2Dokument4 SeitenActividad 2Carlos PedrazaNoch keine Bewertungen

- Tarea 5-La Placa BaseDokument3 SeitenTarea 5-La Placa BaseDavid Hernandez LopezNoch keine Bewertungen

- Buses Del SistemaDokument6 SeitenBuses Del SistemaJesus Chumpitaz FranciaNoch keine Bewertungen

- Conceptos Basicos de Redes y EnrutamientoDokument90 SeitenConceptos Basicos de Redes y Enrutamientoasdajklsd100% (1)

- SUBPROGRAMASDokument13 SeitenSUBPROGRAMASasirNoch keine Bewertungen

- Superbloque y sistemas de archivosDokument7 SeitenSuperbloque y sistemas de archivosGeronimo Ortega0% (2)

- 5.2.1.4 Packet Tracer - Configuring SSH Instruction - ILMDokument2 Seiten5.2.1.4 Packet Tracer - Configuring SSH Instruction - ILMCarlos FernandezNoch keine Bewertungen

- Guía DBA para La Resolución de Problemas de Rendimiento de SQL Server Parte 2Dokument9 SeitenGuía DBA para La Resolución de Problemas de Rendimiento de SQL Server Parte 2eserranosNoch keine Bewertungen

- Examen 1 LinuxDokument11 SeitenExamen 1 Linuxجيوفاني بينياراندا رودريغيزNoch keine Bewertungen

- Practica VLANs Con OSPFDokument4 SeitenPractica VLANs Con OSPFJuan Jose Enrique GarciaNoch keine Bewertungen

- 10.1.3.3 Packet Tracer - Configuring DHCPv4 Using Cisco IOS InstructionsDokument3 Seiten10.1.3.3 Packet Tracer - Configuring DHCPv4 Using Cisco IOS InstructionsJohn RodriguezNoch keine Bewertungen

- Pisd-501 TrabajofinalDokument3 SeitenPisd-501 TrabajofinalPiero CondoriNoch keine Bewertungen

- Reporte Algoritmos de Planificación de ProcesosDokument11 SeitenReporte Algoritmos de Planificación de ProcesosJenny StevezNoch keine Bewertungen

- Procedimientos Totalpack1Dokument7 SeitenProcedimientos Totalpack1Jose rojadNoch keine Bewertungen

- 3.6.1.2 Packet Tracer - Configure AAA Authentication On Cisco Routers - En.esDokument7 Seiten3.6.1.2 Packet Tracer - Configure AAA Authentication On Cisco Routers - En.esWilmer VelásquezNoch keine Bewertungen

- Modulo 4. Habilidades de Linea de Comandos PDFDokument17 SeitenModulo 4. Habilidades de Linea de Comandos PDFfranciscotolox67Noch keine Bewertungen

- Manual Sobre Crear Un Proxy Transparente Con PfSense - Squid + SquidGuard - LinuxPartyDokument14 SeitenManual Sobre Crear Un Proxy Transparente Con PfSense - Squid + SquidGuard - LinuxPartyOmar Fernando Rojas GarciaNoch keine Bewertungen

- CH 8Dokument12 SeitenCH 8Ferney ChicaNoch keine Bewertungen

- CCNA 11.2.4.5 Lab - Accessing Network Devices With SSHDokument11 SeitenCCNA 11.2.4.5 Lab - Accessing Network Devices With SSHRobert HenryNoch keine Bewertungen

- Arquitectura Del Procesador X86Dokument7 SeitenArquitectura Del Procesador X86Luis JosueNoch keine Bewertungen

- 02 Unidad IIDokument25 Seiten02 Unidad IIBraian Stalin Pineda ReyesNoch keine Bewertungen

- El UP 8086 Fue de Los Primeros en Utilizar Un Bus de 16Dokument4 SeitenEl UP 8086 Fue de Los Primeros en Utilizar Un Bus de 16Annie UniNoch keine Bewertungen

- Presentación DE LENGUAJE ENSAMBLADORDokument34 SeitenPresentación DE LENGUAJE ENSAMBLADORMario Padilla100% (1)

- Unidad1 Panorama Del Hardware de La IBM PCDokument31 SeitenUnidad1 Panorama Del Hardware de La IBM PCtcondesNoch keine Bewertungen

- UNIDAD 2 Lenguaje EnsambladorDokument69 SeitenUNIDAD 2 Lenguaje EnsambladorAngelus Charls100% (1)

- Programación Lineal Con Variables EnterasDokument10 SeitenProgramación Lineal Con Variables EnterasJean Paul PereaNoch keine Bewertungen

- Reglamento de Tesis Universitaria para La Obtención Del Titulo Profesional de Ingeniero de SistemasDokument7 SeitenReglamento de Tesis Universitaria para La Obtención Del Titulo Profesional de Ingeniero de SistemasJean Paul PereaNoch keine Bewertungen

- Programación Entera BinariaDokument7 SeitenProgramación Entera BinariaJean Paul Perea78% (9)

- Tais Sesionxii XiiiDokument7 SeitenTais Sesionxii Xiiidevil23maycrynarutoNoch keine Bewertungen

- DiagramasDokument57 SeitenDiagramasJean Paul Perea0% (1)

- Reglamento de Prácticas Sistemas-UNTDokument3 SeitenReglamento de Prácticas Sistemas-UNTJean Paul PereaNoch keine Bewertungen

- Tecnología Cliente-ServidorDokument17 SeitenTecnología Cliente-ServidorJean Paul Perea100% (2)

- Diagrama MatricialDokument16 SeitenDiagrama MatricialJean Paul PereaNoch keine Bewertungen

- Tais Sesión IIDokument6 SeitenTais Sesión IIJean Paul PereaNoch keine Bewertungen

- Tais Sesión VIDokument3 SeitenTais Sesión VIJean Paul PereaNoch keine Bewertungen

- Tais Sesión VIIIDokument5 SeitenTais Sesión VIIIJean Paul PereaNoch keine Bewertungen

- Tais Sesión IIIDokument10 SeitenTais Sesión IIIJean Paul PereaNoch keine Bewertungen

- Tais Sesión VIIDokument10 SeitenTais Sesión VIIJean Paul PereaNoch keine Bewertungen

- Diagrama de ArbolDokument15 SeitenDiagrama de ArbolDiego RiveraNoch keine Bewertungen

- Tais Sesión IDokument5 SeitenTais Sesión IJean Paul PereaNoch keine Bewertungen

- DashboardDokument1 SeiteDashboardJean Paul PereaNoch keine Bewertungen

- ASSI Sesión T5 Auditoría Del CVDSDokument6 SeitenASSI Sesión T5 Auditoría Del CVDSJean Paul Perea100% (1)

- ASSI Sesión T3 Perfil de Auditor y Tipos de AuditoriaDokument3 SeitenASSI Sesión T3 Perfil de Auditor y Tipos de AuditoriaJean Paul PereaNoch keine Bewertungen

- 5) El Diseño Del Proyecto (Proceso Productivo)Dokument10 Seiten5) El Diseño Del Proyecto (Proceso Productivo)Jean Paul PereaNoch keine Bewertungen

- 4) Tamaño y Localización de Proyectos de InversiónDokument11 Seiten4) Tamaño y Localización de Proyectos de InversiónJean Paul PereaNoch keine Bewertungen

- RC Sesion T05Dokument28 SeitenRC Sesion T05Jean Paul PereaNoch keine Bewertungen

- 2) Clasificación de Los Proyectos de InversiónDokument7 Seiten2) Clasificación de Los Proyectos de InversiónJean Paul PereaNoch keine Bewertungen

- 1) Proyectos de InversiónDokument10 Seiten1) Proyectos de InversiónJean Paul PereaNoch keine Bewertungen

- Modelo de Estimación de Proyecto de Software (COCOMO)Dokument61 SeitenModelo de Estimación de Proyecto de Software (COCOMO)Jean Paul Perea100% (1)

- 3) Estudio de MercadoDokument14 Seiten3) Estudio de MercadoJean Paul PereaNoch keine Bewertungen

- ASSI Sesión T7 COBITDokument6 SeitenASSI Sesión T7 COBITJean Paul PereaNoch keine Bewertungen

- ASSI Sesión T2 Conceptos, Delito Informático, Control Interno y Auditoría InternaDokument6 SeitenASSI Sesión T2 Conceptos, Delito Informático, Control Interno y Auditoría InternaJean Paul PereaNoch keine Bewertungen

- ASSI Sesión T1 Auditoria de SIDokument5 SeitenASSI Sesión T1 Auditoria de SIJean Paul PereaNoch keine Bewertungen

- Caracteristicas Formulacion de ProyctosDokument41 SeitenCaracteristicas Formulacion de ProyctosHumbert GxNoch keine Bewertungen

- ASSI Sesión T4 Ciclo de Vida de Una AuiditoríaDokument2 SeitenASSI Sesión T4 Ciclo de Vida de Una AuiditoríaJean Paul PereaNoch keine Bewertungen

- Libro Manual de Mantenimiento y Reparación de PCDokument43 SeitenLibro Manual de Mantenimiento y Reparación de PCLucy CelesteNoch keine Bewertungen

- Barra de Herramientas Layout, Trabajando Con Plantillas 01Dokument13 SeitenBarra de Herramientas Layout, Trabajando Con Plantillas 01miqueasNoch keine Bewertungen

- Centralair - Tratamiento Del Aire ComprimidoDokument24 SeitenCentralair - Tratamiento Del Aire ComprimidoBrayam Jenrry Monterroso QuispeNoch keine Bewertungen

- BIOS Pitidos y MensajesDokument10 SeitenBIOS Pitidos y MensajesMosquera Ayala AlexanderNoch keine Bewertungen

- Polímeros y Materiales CompuestosDokument19 SeitenPolímeros y Materiales Compuestoshumberto100% (1)

- Cotizacion MotorDokument4 SeitenCotizacion MotormichelyNoch keine Bewertungen

- Contabilidad 2Dokument27 SeitenContabilidad 2Gabriela AguilarNoch keine Bewertungen

- Reciclaje ComputacionalDokument12 SeitenReciclaje ComputacionalVirizitha RamirezNoch keine Bewertungen

- Tipos de Nave Gad Ores de InternetDokument9 SeitenTipos de Nave Gad Ores de InternetjanetheduNoch keine Bewertungen

- Revista Amigurumis Especial PerrosDokument26 SeitenRevista Amigurumis Especial PerrosPaula88% (8)

- Generaciones de Las ComputadorasDokument10 SeitenGeneraciones de Las ComputadorasVIANNEY MORALESNoch keine Bewertungen

- Filtros Pasabanda de Banda AngostaDokument42 SeitenFiltros Pasabanda de Banda AngostaDaniela Chávez ManrriqueNoch keine Bewertungen

- Apuntes de Circuitos Neumáticos Completo 9 10Dokument2 SeitenApuntes de Circuitos Neumáticos Completo 9 10Edwin WilcheNoch keine Bewertungen

- Contadores de energía eléctrica: tipos y característicasDokument20 SeitenContadores de energía eléctrica: tipos y característicasfrbuenoNoch keine Bewertungen

- RobotsDokument15 SeitenRobotsmartarte100% (1)

- UNI-INGENIERÍA-FACULTAD-INDUSTRIAL-SIST-LAB-CORRIENTE-ALTERNADokument17 SeitenUNI-INGENIERÍA-FACULTAD-INDUSTRIAL-SIST-LAB-CORRIENTE-ALTERNAAbraham Daniel AlanyaNoch keine Bewertungen

- 04 Mec 075 TesisDokument162 Seiten04 Mec 075 TesisAlejandro Martinez RNoch keine Bewertungen

- Diagnostico Irfeyal 2018Dokument2 SeitenDiagnostico Irfeyal 2018nelfrancisco2Noch keine Bewertungen

- Electrónica del vehículo: Diagnóstico y pruebasDokument17 SeitenElectrónica del vehículo: Diagnóstico y pruebasVictor Cabrera HuamanNoch keine Bewertungen

- Digrama 3Dokument1 SeiteDigrama 3Presupuestos ProactiveNoch keine Bewertungen

- Marco TeoricoDokument13 SeitenMarco TeoricoFerZaxAguirreNoch keine Bewertungen

- MATERIALES MAGNÉTICOS: Propiedades magnéticas de aleaciones y cálculo de campos e inductanciasDokument7 SeitenMATERIALES MAGNÉTICOS: Propiedades magnéticas de aleaciones y cálculo de campos e inductanciasCésar Guerrero CorneNoch keine Bewertungen

- Pendientes de La Tecnología de 3ºDokument8 SeitenPendientes de La Tecnología de 3ºfenix5Noch keine Bewertungen

- Cap 7 EntradaSalidaDokument27 SeitenCap 7 EntradaSalidaJon SolaNoch keine Bewertungen

- Lenze 8100 TraduccionDokument20 SeitenLenze 8100 TraduccionPatricio Antonio Cortés PeñaNoch keine Bewertungen

- Panel Operador TP277 OP277Dokument280 SeitenPanel Operador TP277 OP277JLBR23Noch keine Bewertungen

- Transformadores TrihalDokument2 SeitenTransformadores TrihalJOSE GUILLERMONoch keine Bewertungen

- 201901E2LAB1Dokument5 Seiten201901E2LAB1David SanabriaNoch keine Bewertungen

- Ar Her RodDokument1 SeiteAr Her RodJorgeNoch keine Bewertungen