Beruflich Dokumente

Kultur Dokumente

252 256

Hochgeladen von

Ijarcet JournalOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

252 256

Hochgeladen von

Ijarcet JournalCopyright:

Verfügbare Formate

ISSN: 2278 1323

International Journal of Advanced Research in Computer Engineering & Technology

Volume 1, Issue 4, June 2012

252

All Rights Reserved 2012 IJARCET

Abstract In a Communication system, the received signals

are of high data rates making it difficult to process the signals to

extract information of interest. So to solve this problem DDC

makes a better solution. In this paper, an efficient way of

designing and implementing a Wideband Digital down

Converter has been discussed. It is shown that the signal of

interest extracted till now is of narrowband but in this article

extraction of wideband signals from the given ADC signal using

advanced filtering and decimation techniques has been

presented. Filtering is implemented in stages to obtain efficient

response. Multiplier-free filter implementation providing

decimation rates fron 4 to 4096 has been implemented. Also, the

reasons for choosing FPGA over ASSPs to implement DDC are

provided. Xilinx ISE 12.3 version software is used for

simulating each block of DDC at system level testing and Chip

Scope Pro Analyzer tool is used for board level testing. Vitex-5

FPGA with speed -2 is the hardware used for implementing the

design.

Keywords Wideband Digital down converter, ADC, Filtering

and Decimation techniques, ASSP, FPGA, System level testing,

Board level testing.

I. INTRODUCTION

In the current scenario, Digital Communication is one of

the commonly used modes of communication, due to its

advantages over Analog Communication. A Digital

Communication system has three basic blocks a transmitter,

channel and a receiver. The DDC presented in this paper is

the key component of Digital Radio Receiver. Digital Radio

receivers often have fast ADC converters to digitize the band

limited RF or IF signal generating high data rates; but in

many cases, the signal of interest represents a small

proportion of that bandwidth. A DDC allows the frequency

band of interest to be moved down the spectrum so the

sample rate can be reduced, filter requirements and further

processing on the signal of interest become more easily

realizable.

A Digital down Converter converts a digitized real signal

centered at an intermediate frequency (IF) to a base banded

complex signal centered at zero frequency by using a mixer.

Also in addition to down conversion, DDCs typically

decimate to a lower sampling rate by using several stages of

decimation filters. Before decimation, filtering is performed

using linear phase filters to limit the bandwidth to our signal

of interest. The decimated signal, with a lower data rate, is

easier to process on a low speed DSP processor[1].

Fig. 1 Theoretical Block diagram of DDC

II. THEORY of DDC SYSTEM

A DDC consists of five basic blocks

i. NCO (numerically controlled oscillator)

ii. Mixer

iii. CIC (Cascaded integrate comb)

iv. CFIR (Compensation FIR) filter

v. PFIR (Programmable FIR) filter

Fig. 2 Practical Implementation of DDC

Implementation of each block of DDC using advanced

methods has been discussed in this section.

A.NCO

A numerically controlled oscillator (NCO) is a digital

signal generator creating a synchronous (i.e. clocked),

discrete-time, discrete-valued representation of a waveform,

usually sinusoidal. Numerically Controlled Oscillators

(NCO), also called Direct Digital Synthesizers (DDS), offers

several advantages over other types of oscillators in terms of

accuracy, stability and reliability. NCOs provide a flexible

architecture that enables easy programmability such as

on-the-fly frequency/phase.

Design and Implementation of Wideband Digital

Down Converter on FPGA

K.S.Sushmitha

#1

, G.Vimala Kumari

*2

Department of ECE, MVGR COLLEGE OF ENGINEERING

Vizianagaram, A.P, INDIA

sushmitha.ks9@gmail.com

ISSN: 2278 1323

International Journal of Advanced Research in Computer Engineering & Technology

Volume 1, Issue 4, June 2012

253

All Rights Reserved 2012 IJARCET

Fig. 3 Principle of NCO

A. An NCO generally consists of two parts:

- A phase accumulator (PA), which adds to the

value held at its output a frequency control value at each

clock sample.

- A phase-to-amplitude converter (PAC), which

uses the phase accumulator output word (phase word) usually

as an address into a waveform look-up table (LUT) to

provide a corresponding amplitude sample.

1) Phase Accumulator: The phase accumulator is actually a

modulo-M counter that increments its stored number by the

value of Frequency Control Word (Tuning Frequency) each

time it receives a clock pulse.

Fig. 4 Numerically Controlled Oscillator

Tuning frequency is obtained by using the below formula.

clk

Fout = f / 2 . f

N

A

w

When clocked, the phase accumulator (PA) creates a

modulo-2

N

sawtooth waveform as shown in the below figure,

where N is the number of bits carried in the phase

accumulator. N sets the frequency resolution of the

Numerically Controlled Oscillator.

2) Phase-to-amplitude converter: Each phase value from the

PA serves as an address to the LUT which outputs

corresponding amplitude value. Here the LUT is a memory

that stores the amplitude values of sine wave for each phase

value. The N-bit output from PA is truncated to M-bit as the

memory space is 2

M

only. The output of PAC is a sine wave.

Fig. 5 Phase Accumulator Output

B. The Mixer

A mixer is used to convert the IF signal to baseband signal

by multiplying the input signal with complex sinusoidal

signal cos (wt)-j sin(wt) = e-jwt which is generated by NCO

thus giving two signals as output i.e.;

i. In-Phase signal

ii. Quadrature-Phase signal

where these signals are 90 degrees out of phase with each

other.

This works on the (simplified) mathematical principle:

Frequency(A) * Frequency(B) = Frequency(A-B) +

Frequency(A+B)[1].

The further stage is to remove unwanted components.

C. CIC Filter

The cascaded integrator-comb (CIC) filter is a class of

hardware-efficient linear phase finite impulse response (FIR)

digital filters. The CIC filter is suitable for this high-speed

application because of its ability to achieve high decimation

factors and other reason is it is implemented using additions

and subtractions rather than using multipliers. It decimates by

R which is programmable.

The two basic building blocks of a CIC filter are

1) An integrator (decimator): An integrator is simply a

single-pole IIR filter with a unity feedback coefficient:

Y [n] = y [n-1] + x[n] (1)

This system is also known as an accumulator[2]. The transfer

function for an integrator on the z-plane is

1

H ( ) = 1/(1 - Z )

I

Z

2) Comb Filter (Interpolator): A comb filter running at the

slow sampling rate fs/R is described by

y[n] = x[n] - x[n -M].

A comb filter is a differentiator with a transfer function

H ( ) = 1 - Z

M

C

Z

In this equation, M is the differential delay, and is usually

limited to 1 or 2[2].

Fig. 6 Integrator and Comb filter

ISSN: 2278 1323

International Journal of Advanced Research in Computer Engineering & Technology

Volume 1, Issue 4, June 2012

254

All Rights Reserved 2012 IJARCET

To summarize, a CIC decimator would have N cascaded

integrator stages clocked at fs, followed by a rate change by a

factor R, followed by N cascaded comb stages running at

fs/R[5] .

Fig. 7 CIC Filter

Frequency Characteristics:

The transfer function for a CIC filter at fs is

1

1

0

(1 Z )

H(Z) = H (Z)H (Z) = = Z

(1 Z )

N

RM N RM

K

I C N

K

=

(

(

The magnitude response at the output of the filter is as shown

below[3] .We can obtain an expression for the CIC filter's

frequency response by evaluating H

cic

(z) transfer function on

the z-plane's unit circle, by setting z = e

j

2, yielding:

j2 fD

2 f

cic

j2 f

j2 fD/2 j2 fD/2 j2 fD/2

j2 f/2 j2 f/2 j2 f/2

1 e

H (e ) =

1 e

e (e - e )

=

e (e - e )

j

t

t

t

t t t

t t t

Using Euler's identity 2jsin() = e

j

- e

j

, we can write:

j2 fD/2

2 f

cic j2 f/2

j2 f(D - 1)/2

e 2jsin(2 fD/2)

H (e ) =

e 2jsin(2 f/2)

sin( fD)

e .

sin( f)

j

t

t

t

t

t

t

t

t

=

where here D = M = Differential Delay

It is a sinc function

N

sin Mf

H(f) =

f

sin

R

t

t

In the CIC Filter there is a disadvantage i.e.; it exhibits pass

band droop. So we use CFIR to compensate this.

Fig. 8 Magnitude Response of CIC Filter

D. Compensation FIR filter:

The output of the CIC filter has a sinc shape, which is not

suitable for most applications. A clean-up filter can be

applied at the CIC output to correct for the pass band droop,

as well as to achieve the desired cut-off frequency and filter

shape. This filter typically decimates by a factor of 2 or 4 to

minimize the output sample[4]. This filter will operate at low

frequency (fS/R) to achieve a more efficient hardware

solution. Its magnitude response is an inverse-sinc function.

1

sin( f/R) Mf

G(f) = MR = sin (Mf )

sin( Mf ) sin( Mf )

N N

N

c

t t

t t

| |

~

|

\ .

As before, the filter order can be limited such that it can be

implemented in a single MAC unit, in this case N=62 (63

filter taps).

Fig. 9 Magnitude Response of CFIR Filter

III. IMPLEMENTATION on FPGA

An advantage of using an FPGA for the DDC is that we

can customize the filter chain to exactly meet our

requirements. ASSPs dont offer the design flexibility or

integration attainable in an FPGA.

During filter design, a behavioral model of the complete

DDC is generated using Xilinx ISE software by writing

VHDL code for each individual block and their operation is

tested by simulating the design using Modelsim Simulator.

Later the design is synthesized and implemented on an FPGA

by generating a .bit file of the design and programming,

configuring the FPGA with the .bit file. The correct operation

of the design in the FPGA is tested using Chip Scope Pro

Analyzer tool which uses three main blocks to analyze any

part of DDC. These blocks are generated through the IP Core

Generator tool in Xilinx ISE. The blocks are:

ISSN: 2278 1323

International Journal of Advanced Research in Computer Engineering & Technology

Volume 1, Issue 4, June 2012

255

All Rights Reserved 2012 IJARCET

1) ICON: Integrated controller is use as an interface between

the other two blocks and PC, JTAG which is connected to

FPGA on which the design is programmed.

2) ILA: Integrated Logic Analyzer is used to control the

inputs of any part of DDC thus achieving Controllability of

inner circuits.

3) VIO: Virtual input output is used to observe the outputs of

any part of DDC thus achieving observability.

Fig. 10 Chip Scope pro Block Diagram

Thus Board level testing has also been performed.

Why to choose FPGA:

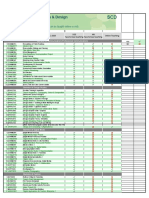

Fig. 11 Comparison of ASIC and FPGA

IV. SIMULATION RESULTS

Thus the results at each block of DDC have been shown.

Here the sine wave is generated at 30MHz output frequency,

thus the tuning frequency is 30MHz

and clock frequency is 100MHz . The input signal to the

mixer is 70MHz. The output of the mixer is in kHz.

Fig. 12 Output wave generated by NCO

The signal from the mixer is filtered and decimated through

CIC and is shown below.

Fig. 13 NCO Output : Result from Chip Scope Pro Analyzer

Fig. 14 Mixer(I) signal output from Chip Scope Pro Analyzer

Fig. 15 Mixer(Q) signal output from Chip Scope Pro Analyzer

Fig. 16 Output of CIC Filter

ISSN: 2278 1323

International Journal of Advanced Research in Computer Engineering & Technology

Volume 1, Issue 4, June 2012

256

All Rights Reserved 2012 IJARCET

Fig. 17 Output of DDC

Thus the output of DDC which contains signal of interest has

been obtained.

CONCLUSION

The components are been designed such that the end users

can customize the design according to their requirements by

simply modifying certain parameters in each block. Also as

FPGA is choosen as the target technology, it results in a

design with low power consumption, accurate performance,

high integration and customizability. Further if required the

components of DDC can be designed to work at higher rates

by further improving their architectures .

REFERENCES

[1] T.Hollis/R.Weir, The Theory of Digital Down Conversion, Hunt

Engineering, 2003.Rev 1.2.

[2] E. B. Hogenauer. An economical class of digital _lters for decimation

and interpolation.IEEE Transactions on Acoustics,Speech and Signal

Processing, ASSP-29(2):155{162, 1981.

[3] Understanding CIC Compensation Filters by Altera corp. Application

Note 455. http://www.altera.com/literature/an/an455.pdf ,April 2007.

[4] Stephen Creaney and Igor Kostarnov Designing Efficient Digital Up

and Down Converters for Wide band Systems. XAPP1113 (v1.0)

November 21, 2008.

[5] Cascaded Integrator-Comb (CIC) Filter V3.0, Xilinx, Inc. 2100 Logic

Drive, march 14, 2012.

[6] Alan V. Oppenheim and Ronald W. Schafer. Discrete-Time Signal

Processing. Pretice-Hall Signal Processing Series. Pretice-Hall,

Englewood Cliffs, 1989.

K.S.Sushmitha received Btech degree in electronics and communication

engineering from Jawaharlal Nehru technological University. She is

currently pursuing the M.Tech degree in VLSI at M.V.G.R.College of

Engineering.

G.Vimala Kumari completed her BE, M.Tech, and presently working as

associate professor in the department of ECE of MVGR College of

Engineering.

Das könnte Ihnen auch gefallen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Virtualizing The Private Cloud For Maximum Resource UtilizationDokument5 SeitenVirtualizing The Private Cloud For Maximum Resource UtilizationIjarcet JournalNoch keine Bewertungen

- 509 512Dokument4 Seiten509 512Ijarcet JournalNoch keine Bewertungen

- 494 497Dokument4 Seiten494 497Ijarcet JournalNoch keine Bewertungen

- 498 503Dokument6 Seiten498 503Ijarcet JournalNoch keine Bewertungen

- 489 493Dokument5 Seiten489 493Ijarcet JournalNoch keine Bewertungen

- Design & Implementation of Linux Based Network Forensic System Using HoneynetDokument5 SeitenDesign & Implementation of Linux Based Network Forensic System Using HoneynetIjarcet JournalNoch keine Bewertungen

- 443 449Dokument7 Seiten443 449Ijarcet JournalNoch keine Bewertungen

- Solving Three Dimensional Bin Packing Problem Using Elitism Based Genetic AlgorithmDokument5 SeitenSolving Three Dimensional Bin Packing Problem Using Elitism Based Genetic AlgorithmIjarcet JournalNoch keine Bewertungen

- Application Development Using WPF: Shirish Patil, Sameer Soni, Pranali Dhete and DR B.B. MeshramDokument4 SeitenApplication Development Using WPF: Shirish Patil, Sameer Soni, Pranali Dhete and DR B.B. MeshramIjarcet JournalNoch keine Bewertungen

- PAPR Reduction of An MC-CDMA System Using SLM Technique: Gagandeep Kaur, Rajbir KaurDokument5 SeitenPAPR Reduction of An MC-CDMA System Using SLM Technique: Gagandeep Kaur, Rajbir KaurIjarcet JournalNoch keine Bewertungen

- 461 470Dokument10 Seiten461 470Ijarcet JournalNoch keine Bewertungen

- 375 378Dokument4 Seiten375 378Ijarcet JournalNoch keine Bewertungen

- 476 479Dokument4 Seiten476 479Ijarcet JournalNoch keine Bewertungen

- 450 455Dokument6 Seiten450 455Ijarcet JournalNoch keine Bewertungen

- Computer Assisted Testing and Evaluation System: Distance Evaluation Using Mobile Agent TechnologyDokument7 SeitenComputer Assisted Testing and Evaluation System: Distance Evaluation Using Mobile Agent TechnologyIjarcet JournalNoch keine Bewertungen

- 433 438Dokument6 Seiten433 438Ijarcet JournalNoch keine Bewertungen

- 439 442Dokument4 Seiten439 442Ijarcet JournalNoch keine Bewertungen

- 407 409Dokument3 Seiten407 409Ijarcet JournalNoch keine Bewertungen

- 410 418Dokument9 Seiten410 418Ijarcet JournalNoch keine Bewertungen

- MC UartDokument8 SeitenMC UartNagesh BsNoch keine Bewertungen

- 388 394Dokument7 Seiten388 394Ijarcet JournalNoch keine Bewertungen

- An Enhancement in Relevance Knowledge Discovery Model For Medical Reasoning Using CBRMDokument6 SeitenAn Enhancement in Relevance Knowledge Discovery Model For Medical Reasoning Using CBRMIjarcet JournalNoch keine Bewertungen

- 379 381Dokument3 Seiten379 381Ijarcet JournalNoch keine Bewertungen

- VLSI Implementation of Pipelined Fast Fourier TransformDokument6 SeitenVLSI Implementation of Pipelined Fast Fourier TransformIjarcet JournalNoch keine Bewertungen

- 402 406Dokument5 Seiten402 406Ijarcet JournalNoch keine Bewertungen

- A Novel Approach For Iris Recognition: Manisha M. Khaladkar, Sanjay R. GanorkarDokument4 SeitenA Novel Approach For Iris Recognition: Manisha M. Khaladkar, Sanjay R. GanorkarIjarcet JournalNoch keine Bewertungen

- Offline Handwritten Signature Verification Using Associative Memory NetDokument5 SeitenOffline Handwritten Signature Verification Using Associative Memory NetIjarcet JournalNoch keine Bewertungen

- 347 352Dokument6 Seiten347 352Ijarcet JournalNoch keine Bewertungen

- 358 365Dokument8 Seiten358 365Ijarcet JournalNoch keine Bewertungen

- 353 357Dokument5 Seiten353 357Ijarcet JournalNoch keine Bewertungen

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (120)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- AYUMJADokument1 SeiteAYUMJASoumet Das SoumetNoch keine Bewertungen

- Building Material Supplier in GurgaonDokument12 SeitenBuilding Material Supplier in GurgaonRodidustNoch keine Bewertungen

- Sabian Aspect OrbsDokument8 SeitenSabian Aspect Orbsellaella13100% (2)

- MLX90614Dokument44 SeitenMLX90614ehsan1985Noch keine Bewertungen

- Tribes Without RulersDokument25 SeitenTribes Without Rulersgulistan.alpaslan8134100% (1)

- Ficha Tecnica Bomba Inyeccion MiniFlex EDokument1 SeiteFicha Tecnica Bomba Inyeccion MiniFlex Ejohn frader arrubla50% (2)

- L 11Dokument3 SeitenL 11trangNoch keine Bewertungen

- RH-A Catalog PDFDokument1 SeiteRH-A Catalog PDFAchmad KNoch keine Bewertungen

- Aristotle - OCR - AS Revision NotesDokument3 SeitenAristotle - OCR - AS Revision NotesAmelia Dovelle0% (1)

- A Project Report ON Strategic Purchasing Procedure, Systems and Policies (Hospital Industry)Dokument20 SeitenA Project Report ON Strategic Purchasing Procedure, Systems and Policies (Hospital Industry)amitwin1983Noch keine Bewertungen

- (EN 10348) - Steel For The Reinforcement of Concrete. Galvanized Reinforcing SteelDokument24 Seiten(EN 10348) - Steel For The Reinforcement of Concrete. Galvanized Reinforcing Steelbagusu_6Noch keine Bewertungen

- Digital Systems Project: IITB CPUDokument7 SeitenDigital Systems Project: IITB CPUAnoushka DeyNoch keine Bewertungen

- Installation Instructions INI Luma Gen2Dokument21 SeitenInstallation Instructions INI Luma Gen2John Kim CarandangNoch keine Bewertungen

- Church and Community Mobilization (CCM)Dokument15 SeitenChurch and Community Mobilization (CCM)FreethinkerTianNoch keine Bewertungen

- Engineering Management: Class RequirementsDokument30 SeitenEngineering Management: Class RequirementsMigaeaNoch keine Bewertungen

- CPD - SampleDokument3 SeitenCPD - SampleLe Anh DungNoch keine Bewertungen

- Saflex-Dg - 41 Data SheetDokument5 SeitenSaflex-Dg - 41 Data SheetrasheedgotzNoch keine Bewertungen

- A Short Survey On Memory Based RLDokument18 SeitenA Short Survey On Memory Based RLcnt dvsNoch keine Bewertungen

- Mahindra&mahindraDokument95 SeitenMahindra&mahindraAshik R GowdaNoch keine Bewertungen

- Chakir Sara 2019Dokument25 SeitenChakir Sara 2019hiba toubaliNoch keine Bewertungen

- BPS C1: Compact All-Rounder in Banknote ProcessingDokument2 SeitenBPS C1: Compact All-Rounder in Banknote ProcessingMalik of ChakwalNoch keine Bewertungen

- Halloween EssayDokument2 SeitenHalloween EssayJonathan LamNoch keine Bewertungen

- SCD Course List in Sem 2.2020 (FTF or Online) (Updated 02 July 2020)Dokument2 SeitenSCD Course List in Sem 2.2020 (FTF or Online) (Updated 02 July 2020)Nguyễn Hồng AnhNoch keine Bewertungen

- Pyramid Type Plate Bending MachineDokument10 SeitenPyramid Type Plate Bending MachineAswin JosephNoch keine Bewertungen

- Static Electrification: Standard Test Method ForDokument10 SeitenStatic Electrification: Standard Test Method Forastewayb_964354182Noch keine Bewertungen

- Anker Soundcore Mini, Super-Portable Bluetooth SpeakerDokument4 SeitenAnker Soundcore Mini, Super-Portable Bluetooth SpeakerM.SaadNoch keine Bewertungen

- Job Satisfaction of Library Professionals in Maharashtra State, India Vs ASHA Job Satisfaction Scale: An Evaluative Study Dr. Suresh JangeDokument16 SeitenJob Satisfaction of Library Professionals in Maharashtra State, India Vs ASHA Job Satisfaction Scale: An Evaluative Study Dr. Suresh JangeNaveen KumarNoch keine Bewertungen

- PDFDokument653 SeitenPDFconstantinNoch keine Bewertungen

- Documentation Report On School's Direction SettingDokument24 SeitenDocumentation Report On School's Direction SettingSheila May FielNoch keine Bewertungen

- Waste Biorefinery Models Towards Sustainable Circular Bioeconomy Critical Review and Future Perspectives2016bioresource Technology PDFDokument11 SeitenWaste Biorefinery Models Towards Sustainable Circular Bioeconomy Critical Review and Future Perspectives2016bioresource Technology PDFdatinov100% (1)