Beruflich Dokumente

Kultur Dokumente

65nm Code

Hochgeladen von

Hazwan Afiq KaswuriOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

65nm Code

Hochgeladen von

Hazwan Afiq KaswuriCopyright:

Verfügbare Formate

go athena # #To allow changing device size, set the gate length as a variable set Lg=0.

065 # #Set up a mesh suitable for a 65nm MOSFET. The MOSFET will be symmetrical #so just model half of the device starting mid channel at 0.0. #Only need to model out to 0.1um so final transistor will be placed in the middl e #of a 0.2um mesh in x direction line x loc=0 spac=0.01 line x loc=0.5*$Lg spac=0.005 line x loc=0.1 spac=0.1 # line y loc=0.00 spac=0.005 line y loc=0.3 spac=0.015 line y loc=0.5 spac=0.02 line y loc=2 spac=1 # # Start off by defining silicon as p type <100> with boron conc=2e15 init orientation=100 c.boron=2e15 #Deposit an oxide on the silicon surface for implanting to prevent channeling deposit oxide thick=0.05 #nwell formation for the body of the pmos transistor. The shallowest implant #will define the threshold voltage so vary to get desired threshold. implant phos dose=2.6E13 energy=420 tilt=5 implant phos dose=3.5E13 energy=50 tilt=5 #Anneal the nwell and electrically activate it diffus temp=1000 time=100 weto2 hcl=3 #Remove all oxide prior to gate oxidation etch oxide all #Grow a thin gate oxide target 2.5nm. Change steps 2,3,4 to adjust thickness # method fermi compress diffuse temp=700 time=34 f.o2=0.5 f.n2=10 t.final=800 pres=1 diffuse temp=800 time=2 f.o2=20 pres=1 diffuse temp=800 time=3 f.o2=10 f.hcl=0.1 pres=1 diffuse temp=800 time=2 f.o2=10 pres=1 diffuse temp=800 time=10 inert diffuse temp=800 time=20 inert t.final=700 #Display actual gate thickness acheived extract name="Thin Gate Tox" thickness oxide mat.occno=1 x.val=0 #Deposit 200nm Gate Poly. deposit poly thick=0.2 division=20 #Dope the poly P-Type implant boron dose=5.0e15 energy=15 tilt=5 #Etch the poly gate etch poly right p1.x= 0.5*$lg #Deposit Spacer TEOS and etch to form the oxide spacer deposit oxide thick=0.02 division=8 etch oxide thick=0.02 struct outf=exspacer.str

#P+ Source Drain Implant (PSD). This is a very shallow implant for 65nm #which is why we had to dope the poly earlier. implant boron dose=1.0e15 energy=4 tilt=0 #Anneal PSD using spike (very fast) RTA diffusion temp=1000 time=2 seconds f.o2=0.3 f.n2=2.7 struct outfile=expsdrta.str #Now need to form silicide on the Source Drain and Gate regions. #130nm and below uses sputtered Cobalt to form CoSi. #First remove all oxide from surfaces where CoSi is to be formed. etch oxide thick=0.014 #Sputter 40nm Cobalt deposit cobalt thick=0.04 div=8 #Use RTA to react Cobalt with Silicon to form CoSi diffusion temp=550 time=10 second inert #Strip away any unreacted cobalt from non silicon surfaces #e.g. the spacer oxide. etch cobalt all struct outfile=exsal.str #mirror the structure to form the complete transistor structure mirror left struct outfile=final.str #Define the electrodes electrode name=drain x=-0.08 electrode name=source x= 0.08 electrode name=gate x= 0 electrode name=substrate backside #----------------------------------------------------------------------------go devedit base.mesh height=1000000 width=1000000 bound.cond !apply max.slope=28 max.ratio=300 rnd.unit=0.001 line.straightening=1 align.points when=automatic imp.refine imp="NetDoping" sensitivity=1 imp.refine min.spacing=0.01 constr.mesh max.angle=90 max.ratio=300 max.height=1 max.width=1 min.height=0.000 1 min.width=0.0001 Mesh Mode=MeshBuild refine mode=both x1=-0.5*$Lg y1=0 x2=0.5*$Lg y2=0.2 ############# PVt Test : Returns PVt, PBeta and PTheta ################ go atlas # set material models models cvt srh print contact name=gate p.poly interface qf=3e10 # get initial solution solve init

method newton trap solve prev

# Bias the drain a bit... solve vdrain=-0.1 name=drain # Ramp the gate log outf=mos1ex08_1.log master solve vgate=0 vstep=-0.05 vfinal=-1.5 vdrain=-0.1 name=gate save outf=mos1ex08_1.str quit

Das könnte Ihnen auch gefallen

- 98-366 MTA Networking Fundamental - SlidesDokument232 Seiten98-366 MTA Networking Fundamental - Slidesharyanto100% (3)

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsVon EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNoch keine Bewertungen

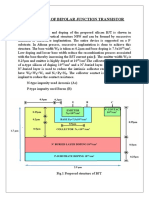

- Tcad - BJTDokument10 SeitenTcad - BJTram_786Noch keine Bewertungen

- Oracle RAC AdministrationDokument26 SeitenOracle RAC AdministrationShivkumar Kurnawal100% (2)

- Form 4 Add Maths Chapter 1Dokument25 SeitenForm 4 Add Maths Chapter 1Azhar GameMaster100% (1)

- Mosfet OperationDokument70 SeitenMosfet OperationTanmayBangaloreNoch keine Bewertungen

- Vlsi PDFDokument81 SeitenVlsi PDFShruthiNoch keine Bewertungen

- 3D OCT-2000 - User Manual PDFDokument114 Seiten3D OCT-2000 - User Manual PDFVladimir Levchenko50% (4)

- Microsoft Powerpoint - Vlsi Design AspectDokument89 SeitenMicrosoft Powerpoint - Vlsi Design AspectAKASHDIP DUTTANoch keine Bewertungen

- Lecture 030 - Deep Submicron (DSM) Cmos TechnologyDokument14 SeitenLecture 030 - Deep Submicron (DSM) Cmos TechnologywatelzbuddyNoch keine Bewertungen

- Kubectl Commands Cheat Sheet PDFDokument1 SeiteKubectl Commands Cheat Sheet PDFJade Devin CabatlaoNoch keine Bewertungen

- Termis 6 0Dokument952 SeitenTermis 6 0Adrian MarinNoch keine Bewertungen

- Solns 4Dokument14 SeitenSolns 4ramprakash_rampelliNoch keine Bewertungen

- FUNDAMENTALS of CMOS VLSI 5th SEM ECE PDFDokument190 SeitenFUNDAMENTALS of CMOS VLSI 5th SEM ECE PDFVarunKaradesaiNoch keine Bewertungen

- Voltage Regulation Calculation PDFDokument135 SeitenVoltage Regulation Calculation PDFPrashant TrivediNoch keine Bewertungen

- Major steps in bipolar IC fabricationDokument5 SeitenMajor steps in bipolar IC fabricationlachuns123Noch keine Bewertungen

- Amada Laser CuttingDokument8 SeitenAmada Laser CuttingMahmud MaherNoch keine Bewertungen

- Solution Manual for 100 Genesys Design Examples: Second EditionVon EverandSolution Manual for 100 Genesys Design Examples: Second EditionNoch keine Bewertungen

- 에미터랑 컬렉터랑 다르게 나온는 거확인할려고 만든 노트패드Dokument2 Seiten에미터랑 컬렉터랑 다르게 나온는 거확인할려고 만든 노트패드고경진Noch keine Bewertungen

- Rishabh Chhabra Assignment2Dokument4 SeitenRishabh Chhabra Assignment2Rishabh ChhabraNoch keine Bewertungen

- Silvaco ATHENA Description 4Dokument21 SeitenSilvaco ATHENA Description 4Nabilah AzizNoch keine Bewertungen

- Silv ProgrammingDokument85 SeitenSilv ProgrammingAadil ShNoch keine Bewertungen

- CMOS VLSI MOS Transistor CharacteristicsDokument26 SeitenCMOS VLSI MOS Transistor CharacteristicsvuaphuNoch keine Bewertungen

- VLSI Technology and Question BankDokument2 SeitenVLSI Technology and Question BankTina TaylorNoch keine Bewertungen

- Chapter 2: CMOS Technology: Instructor: Dr. Po-Wen Chiu (EE/NTHU)Dokument35 SeitenChapter 2: CMOS Technology: Instructor: Dr. Po-Wen Chiu (EE/NTHU)王靖堯Noch keine Bewertungen

- MESFET SilvacoDokument7 SeitenMESFET SilvacoKritiChhabraNoch keine Bewertungen

- E3-327 (3) - M SOI MOSFET Oct 2013Dokument56 SeitenE3-327 (3) - M SOI MOSFET Oct 2013Tara VishinNoch keine Bewertungen

- Bec010 Vlsi - NotesDokument109 SeitenBec010 Vlsi - NotesFarukh ZafarNoch keine Bewertungen

- Assignment Cum Tutorial Sheet - 7 (With Solution)Dokument2 SeitenAssignment Cum Tutorial Sheet - 7 (With Solution)HARSHVARDHAN SINGH RATHORENoch keine Bewertungen

- Sub 50-Nm Finfet PmosDokument4 SeitenSub 50-Nm Finfet PmosAnonymous OUnaZ1g9Noch keine Bewertungen

- sm1 071Dokument2 Seitensm1 071Paulo Henrique D. FavarettoNoch keine Bewertungen

- Dwnload Full Cmos Digital Integrated Circuits Analysis and Design 4th Edition Kang Solutions Manual PDFDokument36 SeitenDwnload Full Cmos Digital Integrated Circuits Analysis and Design 4th Edition Kang Solutions Manual PDFmalinsjavitai100% (10)

- Vlsi BestDokument4 SeitenVlsi Bestkunjanb11Noch keine Bewertungen

- Structure of Bipolar Junction TransistorDokument10 SeitenStructure of Bipolar Junction TransistorNitishNoch keine Bewertungen

- Lab 6Dokument4 SeitenLab 6Dray 7Noch keine Bewertungen

- Physics of VLSI Devices (ECE-5018) Digital Assignment - II: M S G M S GDokument6 SeitenPhysics of VLSI Devices (ECE-5018) Digital Assignment - II: M S G M S GShreyas RaoNoch keine Bewertungen

- Emd QBDokument7 SeitenEmd QBAditya ShrivastavNoch keine Bewertungen

- VLSI Design Assignment ProblemsDokument2 SeitenVLSI Design Assignment ProblemsBhavani BhagyasreeNoch keine Bewertungen

- The Well: Circuit Design, Layout, and Simulation Third Edition R. Jacob BakerDokument43 SeitenThe Well: Circuit Design, Layout, and Simulation Third Edition R. Jacob BakerMostafa MohamedNoch keine Bewertungen

- Unit 1 Basic MOS Technology: Figure 1. Moore's LawDokument18 SeitenUnit 1 Basic MOS Technology: Figure 1. Moore's LawSushruth SastryNoch keine Bewertungen

- CMOS Transistor Comparison & CharacteristicsDokument1 SeiteCMOS Transistor Comparison & Characteristicsmaheshwarivikas1982Noch keine Bewertungen

- Solutions For Chapter 9 Problems 2. Passive Circuit ElementsDokument16 SeitenSolutions For Chapter 9 Problems 2. Passive Circuit Elementsひたぎ 戦場ヶ原Noch keine Bewertungen

- 3.4.1.2 Silicon On Insulator: Chapter 3 CMOS Processing TechnologyDokument1 Seite3.4.1.2 Silicon On Insulator: Chapter 3 CMOS Processing TechnologyCarlos SaavedraNoch keine Bewertungen

- Numericalsmassignments SolvedDokument5 SeitenNumericalsmassignments SolvedghasNoch keine Bewertungen

- DVLSI ESA 2020 Solution (SSR) PDFDokument10 SeitenDVLSI ESA 2020 Solution (SSR) PDFM Chandan ShankarNoch keine Bewertungen

- EE 5171 Fall, 2005 Final Exam: Time (Sec)Dokument6 SeitenEE 5171 Fall, 2005 Final Exam: Time (Sec)Sudipta Romen BiswasNoch keine Bewertungen

- Mosfet: Metal Oxide Semiconductor Field Effect TransistorsDokument47 SeitenMosfet: Metal Oxide Semiconductor Field Effect Transistorschandanayadav8490Noch keine Bewertungen

- Future MOSFET Devices Using High-K (TiO2) DielectricDokument6 SeitenFuture MOSFET Devices Using High-K (TiO2) DielectricIJRASETPublicationsNoch keine Bewertungen

- IC Fabrication TechnologyDokument12 SeitenIC Fabrication TechnologyBiswajit BeheraNoch keine Bewertungen

- VLSI Technology and Applications - 10B11EC612: Tutorial Sheet - 3Dokument1 SeiteVLSI Technology and Applications - 10B11EC612: Tutorial Sheet - 3harshit420Noch keine Bewertungen

- Lec 7,8 Modern CMOS TechnologyDokument43 SeitenLec 7,8 Modern CMOS TechnologyVikram MeenaNoch keine Bewertungen

- CMOS Transistor Layout KungFu Preliminary ReleaseDokument35 SeitenCMOS Transistor Layout KungFu Preliminary ReleaseBabu ChintapalliNoch keine Bewertungen

- Static Logigates 12Dokument19 SeitenStatic Logigates 12api-3750190Noch keine Bewertungen

- Assignment #2Dokument2 SeitenAssignment #2Aireen AmirNoch keine Bewertungen

- Kerb A4Dokument3 SeitenKerb A4muhammad faisalNoch keine Bewertungen

- Microelectronic CircuitDokument696 SeitenMicroelectronic CircuitImtiaz AhmedNoch keine Bewertungen

- 10 5 - 1 LN 0259 - 0 LN: N N N VDokument18 Seiten10 5 - 1 LN 0259 - 0 LN: N N N VfneojwgfjeNoch keine Bewertungen

- CMOS Fabrication Process and Layout Design Rules Lecture 10Dokument4 SeitenCMOS Fabrication Process and Layout Design Rules Lecture 10lomash acharyaNoch keine Bewertungen

- Electrical Machine Design SOLVED PROBLEMS ON DC MACHINE MAGNETIC CIRCUIT Continuation of Chapter PDFDokument14 SeitenElectrical Machine Design SOLVED PROBLEMS ON DC MACHINE MAGNETIC CIRCUIT Continuation of Chapter PDFMahesh MohananNoch keine Bewertungen

- BJT Ic FabricationDokument20 SeitenBJT Ic Fabricationestifvnjjsnvk100% (2)

- BASIC VLSI DESIGN .PptsDokument32 SeitenBASIC VLSI DESIGN .PptsNarayana Rao RevallaNoch keine Bewertungen

- Sheet 4 (Answers)Dokument49 SeitenSheet 4 (Answers)يوسف عادل حسانينNoch keine Bewertungen

- Problems SolutionsDokument23 SeitenProblems SolutionsMukesh Kumar0% (1)

- Complementary Metal-Oxide-Semiconductor (CMOS) (PronouncedDokument3 SeitenComplementary Metal-Oxide-Semiconductor (CMOS) (PronouncedMeiling MizukiNoch keine Bewertungen

- VLSI design overview and MOS transistorsDokument30 SeitenVLSI design overview and MOS transistorsratnavaliNoch keine Bewertungen

- Vlsi Assign PDFDokument19 SeitenVlsi Assign PDFudamtewNoch keine Bewertungen

- Organic Light-Emitting Transistors: Towards the Next Generation Display TechnologyVon EverandOrganic Light-Emitting Transistors: Towards the Next Generation Display TechnologyNoch keine Bewertungen

- Physics of Electronics KEEE1124Dokument18 SeitenPhysics of Electronics KEEE1124Hazwan Afiq KaswuriNoch keine Bewertungen

- Prima Test Math Form3Dokument9 SeitenPrima Test Math Form3Hazwan Afiq KaswuriNoch keine Bewertungen

- Tut3 Sofware EngineDokument2 SeitenTut3 Sofware EngineHazwan Afiq Kaswuri57% (7)

- Electric MotorsDokument8 SeitenElectric MotorsjesusmendezvillamideNoch keine Bewertungen

- LRU-K Page Replacement Algorithm: CSCI 485 Lecture Notes Instructor: Prof. Shahram GhandeharizadehDokument29 SeitenLRU-K Page Replacement Algorithm: CSCI 485 Lecture Notes Instructor: Prof. Shahram GhandeharizadehMoulee VijayNoch keine Bewertungen

- Rockwell Automation OverviewDokument13 SeitenRockwell Automation OverviewVivek ThotaNoch keine Bewertungen

- 01 - Failure Analysis of A Special Vehicle Engine Connecting RodDokument12 Seiten01 - Failure Analysis of A Special Vehicle Engine Connecting RodBima SorayaNoch keine Bewertungen

- The Advantages of Online Shopping PlatformDokument2 SeitenThe Advantages of Online Shopping PlatformNor SyahirahNoch keine Bewertungen

- ECC 602 Computer Communication Network exam modulesDokument2 SeitenECC 602 Computer Communication Network exam modulesRatnakar YadavNoch keine Bewertungen

- Hull Me S Her ManualDokument121 SeitenHull Me S Her ManualCông TuấnNoch keine Bewertungen

- CBT RecDokument37 SeitenCBT Recanon-743856Noch keine Bewertungen

- MagicQ Remote App SetupDokument4 SeitenMagicQ Remote App Setupderte linoNoch keine Bewertungen

- DCDokument1 SeiteDCBSAScitiNoch keine Bewertungen

- Technical Bulletin - ACP - ACS - Connect - Tool - v1.0 - B-307Dokument6 SeitenTechnical Bulletin - ACP - ACS - Connect - Tool - v1.0 - B-307Fabian ArayaNoch keine Bewertungen

- VR Ajp 18 To 20Dokument8 SeitenVR Ajp 18 To 201213 Vaibhav KothareNoch keine Bewertungen

- Epson L805 BrochureDokument4 SeitenEpson L805 Brochureavijit_deNoch keine Bewertungen

- Es Lab Manual-JntukDokument22 SeitenEs Lab Manual-JntukMelissa GuerraNoch keine Bewertungen

- ERPSCM MM SRVServiceEntrySheet 180915 0417 1152Dokument7 SeitenERPSCM MM SRVServiceEntrySheet 180915 0417 1152ronnzaaNoch keine Bewertungen

- COMO LIMPIAR CP PM CS 5.5Dokument10 SeitenCOMO LIMPIAR CP PM CS 5.5Franco AlarcónNoch keine Bewertungen

- Deepfacelab: Integrated, Flexible and Extensible Face-Swapping FrameworkDokument10 SeitenDeepfacelab: Integrated, Flexible and Extensible Face-Swapping FrameworksamsNoch keine Bewertungen

- Check List ExcelDokument4 SeitenCheck List ExcelMykolaNoch keine Bewertungen

- Audio Cover Song Identification Using Convolutional Neural NetworkDokument5 SeitenAudio Cover Song Identification Using Convolutional Neural NetworkNeel KothariNoch keine Bewertungen

- TR1 234Dokument4 SeitenTR1 234Rocha MartinNoch keine Bewertungen

- OBD2 II T79 Digital Auto Scanner Owner's Manual For 1996 and Newer OBD2 VehiclesDokument62 SeitenOBD2 II T79 Digital Auto Scanner Owner's Manual For 1996 and Newer OBD2 VehiclesErwinNoch keine Bewertungen

- Making a Python list of namesDokument14 SeitenMaking a Python list of namesSoniaNoch keine Bewertungen

- Spatial Database For GPS Wildlife Tracking Data: Ferdinando Urbano Francesca CagnacciDokument271 SeitenSpatial Database For GPS Wildlife Tracking Data: Ferdinando Urbano Francesca CagnacciMonse JuarezNoch keine Bewertungen

- Big Data Quality Issues and SolutionsDokument22 SeitenBig Data Quality Issues and SolutionsHassan SiddiquiNoch keine Bewertungen

- AG-HMR10 Operating ManualDokument106 SeitenAG-HMR10 Operating ManualbrittanylbrothersNoch keine Bewertungen