Beruflich Dokumente

Kultur Dokumente

8086 Signals

Hochgeladen von

sushalworkOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

8086 Signals

Hochgeladen von

sushalworkCopyright:

Verfügbare Formate

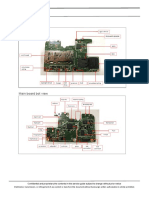

Minimum mode signals:

When the Minimum mode operation is selected, the

8086 provides all control signals needed to implement the memory and I/O interface. The minimum mode signal can be divided into the following basic groups : address/data bus, status control,interrupt and DMA.

Address/Data Bus : these lines serve two

functions. As an address bus is 20 bits long and consists of signal lines A0 through A19. A19 represents the MSB and A0 LSB. A 20bit address gives the 8086 a 1Mbyte memory address space. The 16 data bus lines D0 through D15 are actually multiplexed with address lines A0 through A15respectively. By multiplexed we mean that the bus work as an address bus during first machine cycle and as a data busduring next machine cycles. D15 is the MSB and D0 LSB.

DT/R: (Data transmit / Receive): It is an o/p signal

from the processor to control the direction of data flow DEN : It is an o/p signal used to enable the data during DTR. ALE :It is used to differentiate between HOB an LOB M/IO: It is used to differentiate between Memory access and I/O access. WR:It is a write control signal and it is asserted low whenever the processor writes data to memory or IO port.

INTA : INTA is a line to acknowledge when the

interrupt request is accepted by the processor. HOLd : It is an input signal to the processor from other bus .It is used by DMA Controller to get control of the bus. HLDA :It is an ACK signal by the processor to the BUS requesting the control of the bus through HOLD .

Maximum mode Signals

When the 8086 is set for the maximum-mode

configuration, it provides signals for implementing a multiprocessor / coprocessor system environment. By multiprocessor environment we mean that one microprocessor exists in the system and that each processor is executing its own program. Usually in this type of system environment, there are some system resources that are common to all processors. They are called as global resources. There are also other resources that are assigned to specific processors. These are known as local or private resources.

Coprocessor also means that there is a second

processor in the system. In this two processor does not access the bus at the same time. One passes the control of the system bus to the other and then may suspend its operation. In the maximum-mode 8086 system, facilities are provided for implementing allocation of global resources and passing bus control to other microprocessor or coprocessor.

S0,S1,S2 , : These are status signals required to generate

bus timing and control signals. RQ/GT : Bus Request /Bus Grant to force the processor to release the local bus at the end of current bus cycle. LOCK: It is an o/p signal activated by the LOCK prefix instruction to prevent other bus masters from gaining control of the system bus. QS1,QS0 : The processor provides the status of the queue on these lines.

Das könnte Ihnen auch gefallen

- 8051Dokument69 Seiten8051Raffi SkNoch keine Bewertungen

- Comparison of Pentium Processor With 80386 and 80486Dokument23 SeitenComparison of Pentium Processor With 80386 and 80486Tech_MX60% (5)

- 80486Dokument21 Seiten80486Khadar Nawas0% (1)

- 8086 microprocessor pins and signals overviewDokument11 Seiten8086 microprocessor pins and signals overviewVamsiNoch keine Bewertungen

- MCB2300 CanDokument14 SeitenMCB2300 CanMichaelNoch keine Bewertungen

- 08-SM-A107 Tshoo 7 PDFDokument20 Seiten08-SM-A107 Tshoo 7 PDFSmartFix agudeloNoch keine Bewertungen

- R01an0239ej sh7125Dokument35 SeitenR01an0239ej sh7125ArmanNoch keine Bewertungen

- 25.ACCESSIBLE DISPLAY DESIGN TO CONTROL HOME AREA NETWORKSDocumentDokument84 Seiten25.ACCESSIBLE DISPLAY DESIGN TO CONTROL HOME AREA NETWORKSDocumentdileeppatraNoch keine Bewertungen

- LM - Build An ARM-based Embedded Web ServerDokument46 SeitenLM - Build An ARM-based Embedded Web ServerEmadElDinEzzatNoch keine Bewertungen

- Interfacing 8255Dokument13 SeitenInterfacing 8255S SIVAKUMAR0% (1)

- BLDC DriveDokument37 SeitenBLDC DriveLasya Ganapathi100% (1)

- Chapter 4 Assembly Language and ProgrammingDokument85 SeitenChapter 4 Assembly Language and ProgrammingPetra Kalasa100% (1)

- 8051 Microcontroller FAQDokument160 Seiten8051 Microcontroller FAQkranthi633Noch keine Bewertungen

- Mbedded Echnosolutions: We Are India 'S One of The Leading Trainings & Jobs Providing OrganizationDokument23 SeitenMbedded Echnosolutions: We Are India 'S One of The Leading Trainings & Jobs Providing OrganizationKalyani ShindeNoch keine Bewertungen

- Intel 8051 Micrcontroller: What Is A Microcontroller?Dokument20 SeitenIntel 8051 Micrcontroller: What Is A Microcontroller?satya_vanapalli3422Noch keine Bewertungen

- Emb PIC Charles Kim Chap2Dokument2 SeitenEmb PIC Charles Kim Chap2subiNoch keine Bewertungen

- Accident Detection and Alert System Based On ARM7 MicrocontrollerDokument4 SeitenAccident Detection and Alert System Based On ARM7 MicrocontrollersophiyasharanNoch keine Bewertungen

- Worksheet 4-Input+OutputDokument5 SeitenWorksheet 4-Input+OutputShiza SiddiqueNoch keine Bewertungen

- Final Project Introduction To Computer System UnitDokument19 SeitenFinal Project Introduction To Computer System UnitMuhammad Usman AkhterNoch keine Bewertungen

- Open Compute Project Intel Motherboard v2.0 YGMDokument32 SeitenOpen Compute Project Intel Motherboard v2.0 YGMgawinNoch keine Bewertungen

- Evaluation of Microprocessor PDFDokument2 SeitenEvaluation of Microprocessor PDFJennifer100% (1)

- Module 4-Motherboard.18214342Dokument59 SeitenModule 4-Motherboard.18214342Fercie Q. EngresoNoch keine Bewertungen

- CSE331L - Introduction to Assembly LanguageDokument7 SeitenCSE331L - Introduction to Assembly LanguageTanjila Islam Ritu 1811017642Noch keine Bewertungen

- 8086 MicroprocessorDokument21 Seiten8086 MicroprocessorPinki KumariNoch keine Bewertungen

- DHTDokument9 SeitenDHTNoman Jabbar100% (2)

- Permanent Switch Board ContentDokument56 SeitenPermanent Switch Board ContentCrispNoch keine Bewertungen

- 8096 MicrocontrollerDokument51 Seiten8096 MicrocontrollerNarasimha Murthy Yayavaram67% (3)

- Microcontrollers and Embedded SystemsDokument35 SeitenMicrocontrollers and Embedded SystemsTarek BarhoumNoch keine Bewertungen

- GSM 8051 Microcontroller SMS IrrigationDokument6 SeitenGSM 8051 Microcontroller SMS Irrigationamism24100% (1)

- Interfacing Programs For 8085Dokument37 SeitenInterfacing Programs For 8085archankumarturagaNoch keine Bewertungen

- ARM 4 Part2Dokument9 SeitenARM 4 Part2SUGYAN ANAND MAHARANANoch keine Bewertungen

- Case Study 8086 MicroprocessorDokument4 SeitenCase Study 8086 MicroprocessorVitesh ShengaleNoch keine Bewertungen

- PIC IntroDokument7 SeitenPIC IntroMsJojo AlkhouriNoch keine Bewertungen

- Lab ManualDokument54 SeitenLab ManualImmanuel VinothNoch keine Bewertungen

- Features of 8086Dokument31 SeitenFeatures of 8086Ngaa SiemensNoch keine Bewertungen

- SYNAPSE Techno Design Innovation PVT LTDDokument47 SeitenSYNAPSE Techno Design Innovation PVT LTDcobalt_1223Noch keine Bewertungen

- Real Time ECG On Internet Using Raspberry PiDokument4 SeitenReal Time ECG On Internet Using Raspberry PiVardhan ShahNoch keine Bewertungen

- Rfid Security Access Control System: Submitted byDokument20 SeitenRfid Security Access Control System: Submitted byVale Conde CuatzoNoch keine Bewertungen

- Ee8551 8085 NotesDokument31 SeitenEe8551 8085 NotesKUMARANSCRNoch keine Bewertungen

- Dspa 17ec751 M5Dokument34 SeitenDspa 17ec751 M5digital loveNoch keine Bewertungen

- Keyboard I 8051Dokument3 SeitenKeyboard I 8051sachinshymNoch keine Bewertungen

- FSM DesignDokument61 SeitenFSM DesignParesh SawantNoch keine Bewertungen

- Introduction To MicroprocessorDokument31 SeitenIntroduction To MicroprocessorMuhammad DawoodNoch keine Bewertungen

- Ilovepdf MergedDokument430 SeitenIlovepdf MergedYuvraj ChhabraNoch keine Bewertungen

- Bongkar Laptop Cq41Dokument15 SeitenBongkar Laptop Cq41Andrian AdeNoch keine Bewertungen

- Dac Interface To 8051 PDFDokument4 SeitenDac Interface To 8051 PDFRAVI100% (1)

- Chapter 3: Computer Instructions: ObjectivesDokument7 SeitenChapter 3: Computer Instructions: ObjectivesSteffany RoqueNoch keine Bewertungen

- F3 Serial Port Diagnostic ModesDokument497 SeitenF3 Serial Port Diagnostic ModesEugen0% (1)

- Messenger Development Without Internet Using Zigbee TechnologyDokument89 SeitenMessenger Development Without Internet Using Zigbee TechnologyRaghu ReddyNoch keine Bewertungen

- Important Instructions To Examiners:: (Autonomous)Dokument29 SeitenImportant Instructions To Examiners:: (Autonomous)Rohit Shinde RSNoch keine Bewertungen

- 8255 Ppi ExamplesDokument10 Seiten8255 Ppi Examplesvenky258100% (1)

- Introduction to I/O Interfaces and PortsDokument30 SeitenIntroduction to I/O Interfaces and PortsSafa MNoch keine Bewertungen

- HID TutorialDokument52 SeitenHID TutorialBenny ManurungNoch keine Bewertungen

- Mupi 2 MarksDokument11 SeitenMupi 2 Marksveeyesyes08Noch keine Bewertungen

- Low Power UART Design in Serial CommunicationDokument15 SeitenLow Power UART Design in Serial CommunicationAbhiroop Boggavarapu0% (1)

- TCP Modifications for Wireless NetworksDokument30 SeitenTCP Modifications for Wireless NetworksMurugan Antham RNoch keine Bewertungen

- TMS320F2812 Dsp/biosDokument26 SeitenTMS320F2812 Dsp/biosPantech ProLabs India Pvt LtdNoch keine Bewertungen

- Direct Memory Access (DMA) : Burst ModeDokument7 SeitenDirect Memory Access (DMA) : Burst ModeAnand ReddyNoch keine Bewertungen

- D3 DebugDokument73 SeitenD3 DebugGeorge Anastasiu MafteiNoch keine Bewertungen

- Basic IT MCQs - WaniZahoorDokument79 SeitenBasic IT MCQs - WaniZahoorWani ZahoorNoch keine Bewertungen

- Draft INDEKS 2020Dokument584 SeitenDraft INDEKS 2020aleeNoch keine Bewertungen

- Debug Linux Kernel with GDBDokument40 SeitenDebug Linux Kernel with GDBtedy58Noch keine Bewertungen

- Soyo Sy kt600 Dragon Plus Motherboard User ManualDokument37 SeitenSoyo Sy kt600 Dragon Plus Motherboard User ManualUmberti Boff KolingNoch keine Bewertungen

- Cufft Performance GraphsDokument10 SeitenCufft Performance Graphsapi-12797690Noch keine Bewertungen

- Chapter 04 System UnitDokument9 SeitenChapter 04 System UnitLuci Arce SantiagoNoch keine Bewertungen

- Introduction To 8086 MicroprocessorDokument7 SeitenIntroduction To 8086 MicroprocessorRameen ChNoch keine Bewertungen

- A Software Implementation of AES For A Multos Smart CardDokument88 SeitenA Software Implementation of AES For A Multos Smart Cardyioann100% (3)

- Modicon M340Dokument247 SeitenModicon M340Luis FelipeNoch keine Bewertungen

- MCQMOD5Dokument3 SeitenMCQMOD5maruti800Noch keine Bewertungen

- Objective:: Lab#8: Access Memory of A Trainer Board SSUET/QR/114Dokument3 SeitenObjective:: Lab#8: Access Memory of A Trainer Board SSUET/QR/114Faraz AbbasNoch keine Bewertungen

- MP Div A 10045 Atharva BorikarDokument22 SeitenMP Div A 10045 Atharva BorikarAtharva BorikarNoch keine Bewertungen

- Colfax SKL AVX512 GuideDokument52 SeitenColfax SKL AVX512 GuideAnibal J GuerraNoch keine Bewertungen

- Introduction to Microprocessor in 40 CharactersDokument15 SeitenIntroduction to Microprocessor in 40 Characterskalash satypalNoch keine Bewertungen

- Lab 2Dokument12 SeitenLab 2Darwin VargasNoch keine Bewertungen

- CENG3420 Homework 3 SolutionsDokument5 SeitenCENG3420 Homework 3 SolutionsJosue David Hernandez ViloriaNoch keine Bewertungen

- System Bit M340Dokument13 SeitenSystem Bit M340ifceeae nhceNoch keine Bewertungen

- 2014-10 - VIOS Best Practices and Maintenance - Jaqui Lynch - ViosmaintDokument51 Seiten2014-10 - VIOS Best Practices and Maintenance - Jaqui Lynch - ViosmaintnarendermannNoch keine Bewertungen

- Chapter 3-1Dokument54 SeitenChapter 3-1Bawoke DestaNoch keine Bewertungen

- Microprocessor Multiple Choice QuesDokument6 SeitenMicroprocessor Multiple Choice Quesrraje82100% (9)

- CS501 - HandoutsDokument359 SeitenCS501 - HandoutsAlone GirlNoch keine Bewertungen

- Technology Alone Is Not Enough. We Also Have To Put The Heart "-La Tecnología Por Sí Sola No Basta. También Tenemos Que Poner El Corazón" - Jane GoodallDokument8 SeitenTechnology Alone Is Not Enough. We Also Have To Put The Heart "-La Tecnología Por Sí Sola No Basta. También Tenemos Que Poner El Corazón" - Jane Goodallkima 666Noch keine Bewertungen

- A Peek Inside The ComputerDokument36 SeitenA Peek Inside The ComputerMelvin Escopete0% (1)

- Chapter 6 8086 Hardware Specifications PDFDokument42 SeitenChapter 6 8086 Hardware Specifications PDFseiyfuNoch keine Bewertungen

- Autodyn SPH User Manual & TutorialDokument73 SeitenAutodyn SPH User Manual & TutorialmindertNoch keine Bewertungen

- CSE 211: Computer Organization and Design ONLINE Assignment No.2 General InstructionsDokument4 SeitenCSE 211: Computer Organization and Design ONLINE Assignment No.2 General InstructionsAnkit JainNoch keine Bewertungen

- WLL - Parts of A Desktop ComputerDokument4 SeitenWLL - Parts of A Desktop ComputerEvamie MabilogNoch keine Bewertungen

- EIT - Infosys MaterialDokument54 SeitenEIT - Infosys MaterialAnkeet PandaNoch keine Bewertungen

- Grade 7-Information Technology Fetena Net d101Dokument94 SeitenGrade 7-Information Technology Fetena Net d101Abdiwaliali MusseNoch keine Bewertungen