Beruflich Dokumente

Kultur Dokumente

ECE 4110 - Sequential Logic Design Lecture #15: Agenda

Hochgeladen von

Bala SubramanianOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

ECE 4110 - Sequential Logic Design Lecture #15: Agenda

Hochgeladen von

Bala SubramanianCopyright:

Verfügbare Formate

ECE 4110 Sequential Logic Design Lecture #15

Agenda

1. VHDL : Test Benches

Announcements

1. HW # 6 due 2. HW #7 assigned 3. Next Test 1 review

Lecture #15 Page 1

VHDL : Test Benches

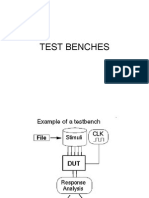

Test Benches

- We need to stimulate our designs in order to test their functionality - Stimulus in a real system is from an external source, not from our design - We need a method to test our designs that is not part of the design itself - This is called a "Test Bench"

- Test Benches are VHDL entity/architectures with the following: - We instantiate the design to be tested using components - We call these instantiations "Unit Under Test" (UUT) or "Device Under Test". - The entity has no ports - We create a stimulus generator within the architecture - We can use reporting features to monitor the expected outputs

Lecture #15 Page 2

VHDL : Test Benches

Test Benches

- Test Benches are for Verification, not for Synthesis!!! - this allows us to use constructs that we ordinarily wouldn't put in a design because they are not synthesizable

Let's test this MUX

entity Mux_2to1 is port (A, B, Sel Y entity Mux_2to1; : in : out STD_LOGIC; STD_LOGIC);

Lecture #15 Page 3

VHDL : Test Benches

entity Test_Mux is end entity Test_Mux; architecture Test_Mux_arch of Test_Mux is signal signal signal In1_TB, In2_TB Sel_TB Out_TB : STD_LOGIC; : STD_LOGIC; : STD_LOGIC; -- setup internal Test Signals -- give descriptive names to make -- apparent they are test signals -- declare any used components STD_LOGIC; STD_LOGIC); -- the test bench entity has no ports

component Mux_2to1 port (A, B, Sel : in Y : out end component; begin

UUT : Mux_2to1 port map ( A => In1_TB, B => In2_TB, Sel => Sel_TB, Y => Out_TB);

-- instantiate the design to test

Lecture #15 Page 4

VHDL : Test Benches

STIM : process -- create process to generate stimulus begin In1_TB <= '0'; In2_TB <= '0'; Sel_TB <= '0' wait for 10ns -- we can use wait In1_TB <= '0'; In2_TB <= '1'; Sel_TB <= '0' wait for 10ns -- statements to control In1_TB <= '1'; In2_TB <= '0'; Sel_TB <= '0' wait for 10ns -- the speed of the stim : : : In1_TB <= '1'; In2_TB <= '1'; Sel_TB <= '1' wait for 10ns end process STIM; end architecture Test_Mux_2to1;

-- end with a wait

Lecture #15 Page 5

VHDL : Test Benches

Test Bench Reporting

- There are reporting features that allow us to monitor the output of a design - We can compare the output against "Golden" data and report if there are differences - This is powerful when we evaluate our designs across power, temp, process..

Assert

- the keyword "assert" will check a Boolean expression - if the Boolean expression is FALSE, it will print a string following the "report" keyword - Severity levels are also reported with possible values {ERROR, WARNING, NOTE, FAILURE} ex) A<='0'; B<='0'; wait for 10ns; assert (Z='1') report "Failed test 00" severity ERROR;

- The message comes out at the simulator console.

Lecture #15 Page 6

VHDL : Test Benches

Report

- the keyword "report" will always print a string - this is good for outputting the process of a test - Severity levels are also reported ex) report "Beginning the MUX test" severity NOTE; A<='0'; B<='0'; wait for 10ns; assert (Z='1') report "Failed test 00" severity ERROR;

Lecture #15 Page 7

Das könnte Ihnen auch gefallen

- PLC Programming from Novice to Professional: Learn PLC Programming with Training VideosVon EverandPLC Programming from Novice to Professional: Learn PLC Programming with Training VideosBewertung: 5 von 5 Sternen5/5 (1)

- J GSV:KDokument96 SeitenJ GSV:Kmeghna veggalam100% (1)

- UVM RamakrishnaDokument54 SeitenUVM Ramakrishnahv_chillal880% (2)

- Verification ConceptsDokument33 SeitenVerification Conceptsamigottp100% (1)

- Reso Course PlannerDokument2 SeitenReso Course PlannerSnehasishGhosh100% (1)

- Principles of Electromechanical Energy ConversionDokument21 SeitenPrinciples of Electromechanical Energy ConversionJehovah CoelhoNoch keine Bewertungen

- Data Driven System Engineering: Automotive ECU DevelopmentVon EverandData Driven System Engineering: Automotive ECU DevelopmentNoch keine Bewertungen

- Systemverilog - CodingDokument39 SeitenSystemverilog - CodingV SharmaNoch keine Bewertungen

- SM 1201r9 UsxrayDokument500 SeitenSM 1201r9 UsxrayMurat KaanNoch keine Bewertungen

- A Dimensional Engineering Process For ShipbuildingDokument11 SeitenA Dimensional Engineering Process For ShipbuildingWJccnNoch keine Bewertungen

- PLC Programming & Implementation: An Introduction to PLC Programming Methods and ApplicationsVon EverandPLC Programming & Implementation: An Introduction to PLC Programming Methods and ApplicationsNoch keine Bewertungen

- Basic Engineering Correlation Calculus v3 001Dokument3 SeitenBasic Engineering Correlation Calculus v3 001Ska doosh100% (1)

- SoC VerificationDokument68 SeitenSoC VerificationspaulsNoch keine Bewertungen

- MB Truck Explorer Manual GB PDFDokument117 SeitenMB Truck Explorer Manual GB PDFاحمد ابو عبداللهNoch keine Bewertungen

- VHDL - Lab SolutionDokument33 SeitenVHDL - Lab Solutionmdhuq1Noch keine Bewertungen

- Software Testing Strategies GuideDokument29 SeitenSoftware Testing Strategies GuideAbrar MohammadNoch keine Bewertungen

- VHDL Testbench TutorialDokument6 SeitenVHDL Testbench TutorialJamesMatthewWongNoch keine Bewertungen

- DFT Scan Insertion: VLSI Testing and Design For TestabilityDokument19 SeitenDFT Scan Insertion: VLSI Testing and Design For TestabilityHuzur AhmedNoch keine Bewertungen

- Introduction To PragmaticsDokument119 SeitenIntroduction To PragmaticsIsabella IsaBella75% (4)

- How scan chains work for stuck-at and delay testingDokument15 SeitenHow scan chains work for stuck-at and delay testingprakashthamankarNoch keine Bewertungen

- The Practical Reference Guide ForDokument21 SeitenThe Practical Reference Guide ForIgnacio SantiagoNoch keine Bewertungen

- Formal Verification: An Essential Toolkit for Modern VLSI DesignVon EverandFormal Verification: An Essential Toolkit for Modern VLSI DesignBewertung: 4 von 5 Sternen4/5 (4)

- Lab5 Synopsys Tetramax DFTDokument20 SeitenLab5 Synopsys Tetramax DFTJay PadaliyaNoch keine Bewertungen

- Dpu 6055Dokument54 SeitenDpu 6055Daniel PricopNoch keine Bewertungen

- DFTDokument28 SeitenDFTHareshPatel100% (2)

- ECE 4110 - Sequential Logic Design Lecture #15: AgendaDokument7 SeitenECE 4110 - Sequential Logic Design Lecture #15: AgendaraghvendrmNoch keine Bewertungen

- Qa Test PlansDokument8 SeitenQa Test PlansAli SeddiekNoch keine Bewertungen

- Solution Manual For VHDL For Engineers Kenneth L ShortDokument19 SeitenSolution Manual For VHDL For Engineers Kenneth L ShortMarieHughesebgjp100% (86)

- Writing Test Benches: A Free Application NoteDokument8 SeitenWriting Test Benches: A Free Application NoteEhsan MahdaviNoch keine Bewertungen

- Ee201 TestbenchDokument19 SeitenEe201 TestbenchSamNoch keine Bewertungen

- Ch07 TestingDokument34 SeitenCh07 TestingSummer TriangleNoch keine Bewertungen

- RSP OSS SchulungDokument248 SeitenRSP OSS Schulungsalloum18Noch keine Bewertungen

- MUX 2-1 BehavioralDokument5 SeitenMUX 2-1 BehavioralFaza RosyadanNoch keine Bewertungen

- Test BenchDokument86 SeitenTest BenchPrathamesh GangalNoch keine Bewertungen

- Encounter Test Lab VLSI ASICDokument10 SeitenEncounter Test Lab VLSI ASICShama LolyNoch keine Bewertungen

- System Verilog1Dokument27 SeitenSystem Verilog1Suguna PriyaNoch keine Bewertungen

- Lab4 - Tasks, Functions, and TestbenchDokument6 SeitenLab4 - Tasks, Functions, and Testbenchwert1a2Noch keine Bewertungen

- ECNG3016 Practical 3Dokument12 SeitenECNG3016 Practical 3Marlon BoucaudNoch keine Bewertungen

- Writing A Testbench in Verilog & Using To Test 1. SynopsisDokument19 SeitenWriting A Testbench in Verilog & Using To Test 1. SynopsissubashNoch keine Bewertungen

- Week5-Slides WatermarkDokument30 SeitenWeek5-Slides WatermarkHahjaNoch keine Bewertungen

- Classroom 13Dokument28 SeitenClassroom 13nitcvisheshNoch keine Bewertungen

- How To Write A VHDL Test BenchDokument4 SeitenHow To Write A VHDL Test BenchEvliya ÜlkerNoch keine Bewertungen

- Lecture 8 VHDL Test BenchesDokument101 SeitenLecture 8 VHDL Test BenchesNathaly Soledad Esponda HernándezNoch keine Bewertungen

- Ch07 TestingDokument30 SeitenCh07 TestingjulioNoch keine Bewertungen

- Software Testing Lect 2-3Dokument34 SeitenSoftware Testing Lect 2-3HiraishinSeiNoch keine Bewertungen

- Self-checking testbench speeds up verificationDokument23 SeitenSelf-checking testbench speeds up verificationKapasi TejasNoch keine Bewertungen

- UEC2302 Digital System Design: Unit 5: Lecture-9 Test BenchesDokument50 SeitenUEC2302 Digital System Design: Unit 5: Lecture-9 Test BenchesAmoga LekshmiNoch keine Bewertungen

- Testing: One of The Desirable Properties of Engineering Requirements Is That It Be VerifiableDokument36 SeitenTesting: One of The Desirable Properties of Engineering Requirements Is That It Be VerifiableMUHAMMADNoch keine Bewertungen

- VLSI Design For Test/Power Spring 2017 Project 4: Chip Testing Lab Final Reports Due On 11:59pm, 4/30/2017Dokument5 SeitenVLSI Design For Test/Power Spring 2017 Project 4: Chip Testing Lab Final Reports Due On 11:59pm, 4/30/2017srikar_dattaNoch keine Bewertungen

- Testing in Software Engineering:: Question-19Dokument3 SeitenTesting in Software Engineering:: Question-19Imtiyaz BashaNoch keine Bewertungen

- Testing Verilog Designs with TestbenchesDokument36 SeitenTesting Verilog Designs with TestbenchesĐức NguyễnNoch keine Bewertungen

- Keysight i3070 ICT System Getting Started GuideDokument8 SeitenKeysight i3070 ICT System Getting Started GuideSergio BustillosNoch keine Bewertungen

- ArchL Functional Verification 09Dokument26 SeitenArchL Functional Verification 09Ajax KrausNoch keine Bewertungen

- Unit Test ProcessDokument15 SeitenUnit Test ProcessSakthivel PNoch keine Bewertungen

- A Verilog HDL Test Bench Primer: Application NoteDokument14 SeitenA Verilog HDL Test Bench Primer: Application NoteJesús AraujoNoch keine Bewertungen

- Verilog HDL - Introduction to Typical Design Flow and BasicsDokument59 SeitenVerilog HDL - Introduction to Typical Design Flow and BasicsBhargavi AndraNoch keine Bewertungen

- Lecture TestbenchesDokument13 SeitenLecture TestbenchesryujindanceNoch keine Bewertungen

- Simulation, Verification and Testing: 0Dokument14 SeitenSimulation, Verification and Testing: 0ssfofoNoch keine Bewertungen

- SE463-U1 Fundamentals of Testing - 21 - DoneDokument20 SeitenSE463-U1 Fundamentals of Testing - 21 - DoneSam SamNoch keine Bewertungen

- Lab 1Dokument5 SeitenLab 1sean_bostic7193Noch keine Bewertungen

- Verilog Code for Frequency Division and FSMDokument40 SeitenVerilog Code for Frequency Division and FSMYogesh TiwariNoch keine Bewertungen

- Lecture 12Dokument32 SeitenLecture 12rahulNoch keine Bewertungen

- Eee446 Lab Manual Spring2015Dokument23 SeitenEee446 Lab Manual Spring2015vognarNoch keine Bewertungen

- 2015 DVClub Austin SVA Tutorial and SVA PlanningDokument39 Seiten2015 DVClub Austin SVA Tutorial and SVA PlanningspaulsNoch keine Bewertungen

- Testing Conventional ApplicationsDokument122 SeitenTesting Conventional ApplicationsAnanthu RKNoch keine Bewertungen

- 04 VerifyDokument68 Seiten04 Verifyveena_scNoch keine Bewertungen

- Stubs and DriversDokument4 SeitenStubs and DriversAreej Al MajedNoch keine Bewertungen

- Lglite + Load Board: Fundamentals of Fault DetectionDokument14 SeitenLglite + Load Board: Fundamentals of Fault DetectionVijayakumar SNoch keine Bewertungen

- Hol 1824 01 Net - PDF - en PDFDokument122 SeitenHol 1824 01 Net - PDF - en PDFHenryNoch keine Bewertungen

- 12EE72 - Model KeyDokument1 Seite12EE72 - Model KeyBala SubramanianNoch keine Bewertungen

- LIC SimDokument6 SeitenLIC SimBala SubramanianNoch keine Bewertungen

- Aptitude Test 1Dokument8 SeitenAptitude Test 1Bala SubramanianNoch keine Bewertungen

- Aptitude Test-1Dokument7 SeitenAptitude Test-1Bala SubramanianNoch keine Bewertungen

- Welcome To The Free Online Tutorial SessionsDokument6 SeitenWelcome To The Free Online Tutorial SessionsBala SubramanianNoch keine Bewertungen

- Staff in Charge H.O.D / EeeDokument1 SeiteStaff in Charge H.O.D / EeeBala SubramanianNoch keine Bewertungen

- EE1251Dokument9 SeitenEE1251Bala SubramanianNoch keine Bewertungen

- Learn English through Tamil Language - Top BooksDokument2 SeitenLearn English through Tamil Language - Top BooksBala SubramanianNoch keine Bewertungen

- SeeniDokument9 SeitenSeeniBala SubramanianNoch keine Bewertungen

- Answer All Questions: P.S.R. Engineering College Sivakasi-626 140Dokument1 SeiteAnswer All Questions: P.S.R. Engineering College Sivakasi-626 140Bala SubramanianNoch keine Bewertungen

- 12PE21-model - 1Dokument2 Seiten12PE21-model - 1Bala SubramanianNoch keine Bewertungen

- Purchase Order 17.04.2013 For PED LABDokument4 SeitenPurchase Order 17.04.2013 For PED LABBala SubramanianNoch keine Bewertungen

- Basic ElementsDokument2 SeitenBasic ElementsBala SubramanianNoch keine Bewertungen

- Iiyear Electronics and Instrumentation Engineering GE32-Environmental Science and EngineeringDokument36 SeitenIiyear Electronics and Instrumentation Engineering GE32-Environmental Science and EngineeringsrajeceNoch keine Bewertungen

- DLC-IA 1 KeyDokument16 SeitenDLC-IA 1 KeyBala SubramanianNoch keine Bewertungen

- Modeling and Analysis of Electrical Machines - Set1Dokument1 SeiteModeling and Analysis of Electrical Machines - Set1Bala SubramanianNoch keine Bewertungen

- Ei1351 LP ADokument4 SeitenEi1351 LP ABala SubramanianNoch keine Bewertungen

- ME - Analysis of Electrical Machines-SyllabusDokument2 SeitenME - Analysis of Electrical Machines-SyllabusBala SubramanianNoch keine Bewertungen

- MODEL - QU - Modeling and Analysis of Electrical Machines - Set1Dokument2 SeitenMODEL - QU - Modeling and Analysis of Electrical Machines - Set1Bala Subramanian80% (5)

- Pe9211 Mj13Dokument2 SeitenPe9211 Mj13Bala SubramanianNoch keine Bewertungen

- Blood Gas AnalyzerDokument3 SeitenBlood Gas AnalyzerBala SubramanianNoch keine Bewertungen

- IA-1. EI 65 QusDokument1 SeiteIA-1. EI 65 QusBala SubramanianNoch keine Bewertungen

- P.S.R. Engineering College, Sivakasi - 626 140 Electrical and Electronics Engineering M.E (Power Electronics and Drives) Course PlanDokument2 SeitenP.S.R. Engineering College, Sivakasi - 626 140 Electrical and Electronics Engineering M.E (Power Electronics and Drives) Course PlanBala SubramanianNoch keine Bewertungen

- P.S.R. Engineering College, Sivakasi - 626 140.: Department of Electrical and Electronics EngineeringDokument1 SeiteP.S.R. Engineering College, Sivakasi - 626 140.: Department of Electrical and Electronics EngineeringBala SubramanianNoch keine Bewertungen

- PSR Engineering College Internal Assessment Test on Biomedical InstrumentationDokument1 SeitePSR Engineering College Internal Assessment Test on Biomedical InstrumentationBala SubramanianNoch keine Bewertungen

- P.S.R. Engineering College, Sivakasi - 626 140Dokument1 SeiteP.S.R. Engineering College, Sivakasi - 626 140Bala SubramanianNoch keine Bewertungen

- Unit 4Dokument36 SeitenUnit 4asksivaNoch keine Bewertungen

- Ee2352 Solid State Drives Unit-Ii Converter / Chopper Fed DC Motor Mr. R. Essaki Raj Senior LecturerDokument19 SeitenEe2352 Solid State Drives Unit-Ii Converter / Chopper Fed DC Motor Mr. R. Essaki Raj Senior LecturerBala SubramanianNoch keine Bewertungen

- SSD - Unit 3Dokument16 SeitenSSD - Unit 3Bala SubramanianNoch keine Bewertungen

- Control Charts For Lognormal DataDokument7 SeitenControl Charts For Lognormal Dataanjo0225Noch keine Bewertungen

- Amd690gm-M2 1219Dokument34 SeitenAmd690gm-M2 1219rmartins_239474Noch keine Bewertungen

- Physics Investigatory Project Class 12 CbseDokument20 SeitenPhysics Investigatory Project Class 12 Cbsesyed50% (6)

- HP Application Lifecycle Management Readme: What's New Installation InstructionsDokument36 SeitenHP Application Lifecycle Management Readme: What's New Installation InstructionsBrandon GarciaNoch keine Bewertungen

- Is It Simple To Explain Simple Experiments The Heavy Newspaper' Stick BreakDokument6 SeitenIs It Simple To Explain Simple Experiments The Heavy Newspaper' Stick Break이온유Noch keine Bewertungen

- Lab 2 ECADokument7 SeitenLab 2 ECAAizan AhmedNoch keine Bewertungen

- Fiber Optics Unit 3Dokument82 SeitenFiber Optics Unit 3NIKHIL SOLOMON P URK19CS1045Noch keine Bewertungen

- Darktrace Csensor Release NotesDokument10 SeitenDarktrace Csensor Release NotesNelson JuniorNoch keine Bewertungen

- Install and Configure Computer SystemsDokument18 SeitenInstall and Configure Computer SystemsAlbino LarozaNoch keine Bewertungen

- Transient Step Response Specification of Z-Source DC-DC ConverterDokument5 SeitenTransient Step Response Specification of Z-Source DC-DC ConverterijsretNoch keine Bewertungen

- WCB Customized Superior Quality Slewing Ring GearDokument173 SeitenWCB Customized Superior Quality Slewing Ring GearWCB BEARINGNoch keine Bewertungen

- Manual ApolloDokument263 SeitenManual ApolloJose Luis CristanchoNoch keine Bewertungen

- CNT SVX15D E4 1111Dokument60 SeitenCNT SVX15D E4 1111Mihai IavorschiNoch keine Bewertungen

- Power Max India PVT LTD Extra Work Done at VMW Shed WorksDokument4 SeitenPower Max India PVT LTD Extra Work Done at VMW Shed WorksparthaNoch keine Bewertungen

- XXXXX: Important Instructions To ExaminersDokument21 SeitenXXXXX: Important Instructions To ExaminersYogesh DumaneNoch keine Bewertungen

- Tutorials 1-4Dokument6 SeitenTutorials 1-4KrishnaNoch keine Bewertungen

- Wiring Diagram SCH17: Service InformationDokument16 SeitenWiring Diagram SCH17: Service Informationابو حمزة صبريNoch keine Bewertungen

- Bandura Et Al.Dokument16 SeitenBandura Et Al.Siddhant JhawarNoch keine Bewertungen

- Practicals ListDokument1 SeitePracticals ListDisha AminNoch keine Bewertungen

- ContentServer PDFDokument16 SeitenContentServer PDFdaniel leon marinNoch keine Bewertungen

- Experimental Noize Guitar Set 1 Effects PedalDokument2 SeitenExperimental Noize Guitar Set 1 Effects PedalSingani Titicaca100% (1)

- Quantitative Reasoning: Factors, HCF & LCM, FactorialsDokument2 SeitenQuantitative Reasoning: Factors, HCF & LCM, FactorialsNaman JainNoch keine Bewertungen