Beruflich Dokumente

Kultur Dokumente

Jfet

Hochgeladen von

Rahul YadavCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Jfet

Hochgeladen von

Rahul YadavCopyright:

Verfügbare Formate

JFET

Junction Field Effect Transistor

Introduction (FET)

Field-effect transistor (FET) are important

devices such as BJTs

Also used as amplifier and logic switches

What is the difference between JFET and

BJT?

BJT is Current-controlled

FET is Voltage-controlled

Types of Field Effect Transistors

(The Classification)

JFET

MOSFET (IGFET)

n-Channel JFET

p-Channel JFET

n-Channel

EMOSFET

p-Channel

EMOSFET

Enhancement

MOSFET

Depletion

MOSFET

n-Channel

DMOSFET

p-Channel

DMOSFET

FET

High input impedance (MO)

(Linear AC amplifier system)

Temperature stable than BJT

Smaller than BJT

Can be fabricated with fewer processing

BJT is bipolar conduction both hole and

electron

FET is unipolar uses only one type of current

carrier

Less noise compare to BJT

Usually use as an Amplifier and logic switch

Introduction.. (Advantages of FET

over BJT)

Disadvantages of FET

Easy to damage compare to BJT

There are 2 types of JFET

n-channel JFET

p-channel JFET

Three Terminal

Drain D

Gate -G

Source S

Junction field-effect transistor..

Gate

Drain

Source

SYMBOLS

n-channel JFET

Gate

Drain

Source

p-channel JFET

N channel JFET:

Major structure is n-type material (channel)

between embedded p-type material to form 2 p-

n junction.

In the normal operation of an n-channel device,

the Drain (D) is positive with respect to the

Source (S). Current flows into the Drain (D),

through the channel, and out of the Source (S)

Because the resistance of the channel depends

on the gate-to-source voltage (V

GS

), the drain

current (I

D

) is controlled by that voltage

N-channel JFET

N-channel JFET..

P channel JFET:

Major structure is p-type material

(channel) between embedded n-type

material to form 2 p-n junction.

Current flow : from Source (S) to Drain

(D)

Holes injected to Source (S) through p-

type channel and flowed to Drain (D)

P-channel JFET

P-channel JFET..

Water analogy for the JFET control

mechanism

JFET Characteristic for V

GS

= 0 V and 0<V

DS

<|V

p

|

To start, suppose V

GS

=0

Then, when V

DS

is increased, I

D

increases.

Therefore, I

D

is proportional to V

DS

for small

values of V

DS

For larger value of V

DS

, as V

DS

increases, the

depletion layer become wider, causing the

resistance of channel increases.

After the pinch-off voltage (V

p

) is reached, the I

D

becomes nearly constant (called as I

D

maximum,

I

DSS

-Drain to Source current with Gate Shorted)

JFET for V

GS

= 0 V and 0<V

DS

<|V

p

|

Channel

becomes

narrower as

V

DS

is

increased

Pinch-off (V

GS

= 0 V, V

DS

= V

P

).

I

D

versus V

DS

JFET Characteristic Curve

for V

GS

= 0 V and 0<V

DS

<|V

p

|

(Application of a negative voltage to the gate of a JFET)

JFET for

JFET Characteristic Curve..

For negative values of V

GS

, the gate-to-channel

junction is reverse biased even with V

DS

=0

Thus, the initial channel resistance of channel is

higher.

The resistance value is under the control of V

GS

If V

GS

= pinch-off voltage(V

P

)

The device is in cutoff (V

GS

=V

GS(off)

= V

P

)

The region where I

D

constant The saturation/pinch-

off region

The region where I

D

depends on V

DS

is called the

linear/ohmic region

p-Channel JFET

p-Channel JFET characteristics with I

DSS

= 6

mA and V

P

= +6 V.

Characteristics for n-channel

JFET

P

+

+

+

Characteristics for p-channel

JFET

Transfer Characteristics

The input-output transfer characteristic of

the JFET is not as straight forward as it is

for the BJT. In BJT:

I

C

=| I

B

which | is defined as the relationship

between I

B

(input current) and I

C

(output

current).

Transfer Characteristics..

In JFET, the relationship between V

GS

(input

voltage) and I

D

(output current) is used to

define the transfer characteristics. It is called

as Shockleys Equation:

The relationship is more complicated (and not

linear)

As a result, FETs are often referred to a

square law devices

| |

|

\ .

2

GS

D DSS

P

V

I = I 1 -

V

V

P

=V

GS (OFF)

Defined by Shockleys equation:

Relationship between I

D

and V

GS

.

Obtaining transfer characteristic curve axis

point from Shockley:

When V

GS

= 0 V, I

D

= I

DSS

When V

GS

= V

GS(off)

or V

p

, I

D

= 0 mA

) (

2

) (

1

off

GS P

off

GS

GS

DSS D

V V

V

V

I I =

|

|

.

|

\

|

=

Transfer Characteristics

Transfer Characteristics

JFET Transfer Characteristic Curve JFET Characteristic Curve

FET BIASING

Unlike BJTs, thermal runaway does

not occur with FETs, as already

discussed in our blog. However, the

wide differences in maximum and

minimum transfer

characteristics make I

D

levels

unpredictable with simple fixed-gate

bias voltage.

To obtain reasonable limits on

quiescent drain currents I

D

and drain-

source voltage V

DS

, source resistor

and potential divider bias techniques

must be used. With few exceptions,

MOSFET bias circuits are similar to

those used for JFETs.

FIXED BIASING

DC bias of a FET device needs setting of gate-source

voltage V

GS

to give desired drain current I

D

. For a

JFET drain current is limited by the saturation current

I

DS

. Since the FET has such a high input impedance

that no gate current flows and the dc voltage of the

gate set by a voltage divider or a fixed battery voltage

is not affected or loaded by the FET.

Fixed dc bias is obtained using a battery V

QG

. This

battery ensures that the gate is always negative with

respect to source and no current flows through resistor

R

G

and gate terminal that is I

G

=0.

The battery provides a voltage V

GS

to bias the N-

channel JFET, but no resulting current is drawn

from the battery V

GG

. Resistor R

G

is included to

allow any ac signal applied through capacitor C

to develop across R

G

. While any ac signal will

develop across R

G

, the dc voltage drop across

R

G

is equal to I

G

R

G

i.e. 0 volt.

The gate-source voltage V

GS

is then

V

GS

= - v

G

v

s

= v

GG

0 = V

GG

The drain -source current I

D

is then fixed by the

gate-source voltage as determined by equation.

This current then causes a voltage drop across

the drain resistor R

D

and is given as V

RD

=

I

D

R

D and

OUTPUT VOLTAGE,

Vout = VDD ID RD

SELF BIASING

This is the most common method for biasing a

JFET. Self-bias circuit for N-channel JFET is shown

in figure.

Since no gate current flows through the reverse-

biased gate-source, the gate current I

G

= 0 and,

therefore,

V

G

= I

G

R

G

= 0

With a drain current I

D

the voltage at the S is

V

s

= I

D

R

s

The gate-source voltage is then

V

Gs

= V

G

- V

s

= 0 I

D

R

s

= I

D

R

s

So voltage drop across resistance R

s

provides

the biasing voltage V

Gg

and no external source is

required for biasing and this is the reason that it

is called self-biasing.

The operating point (that is zero signal I

D

and

V

DS

) can easily be determined from equation and

equation given below :

V

DS =

V

DD

I

D

(R

D +

R

S

)

Thus dc conditions of JFET amplifier are fully

specified. Self biasing of a JFET stabilizes its

quiescent operating point against any change in its

parameters like transconductance.

Let the given JFET be replaced by another JFET

having the double conductance then drain current

will also try to be double but since any increase in

voltage drop across R

s

, therefore, gate-source

voltage, V

GS

becomes more negative and thus

increase in drain current is reduced.

VOLTAGE-DIVIDER

BIASING

A slightly modified form of dc bias is provided by

the circuit shown in figure. The resistors R

Gl

and

R

G2

form a potential divider across drain supply

V

DD

. The voltage V

2

across R

G2

provides the

necessary bias. The additional gate resistor R

Gl

from

gate to supply voltage facilitates in larger adjustment

of the dc bias point and permits use of larger valued

R

S

.

The gate is reverse biased so that I

G

= 0 and gate

voltage

V

G

=V

2

=

(V

DD

/R

G1 +

R

G2

) *R

G2

And

V

GS

= v

G

v

s

= V

G

- I

D

R

s

The circuit is so designed that ID Rs is greater than VG so that

VGS is negative. This provides correct bias voltage.

The operating point can be determined as

I

D

= (V

2

V

GS

)/ R

S

And

V

DS

= V

DD

I

D

(R

D

+ R

S

)

Das könnte Ihnen auch gefallen

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (345)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Experimenter: The Impoverished RadioDokument52 SeitenExperimenter: The Impoverished Radiobenra1100% (1)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- Bobcat 743 - Engine Electrical Circuitry (S - N 501914085 & Above) - 743Dokument4 SeitenBobcat 743 - Engine Electrical Circuitry (S - N 501914085 & Above) - 743CsabaNoch keine Bewertungen

- Mastering The Art of Small TalkDokument8 SeitenMastering The Art of Small TalkRahul YadavNoch keine Bewertungen

- Electric Control SystemDokument108 SeitenElectric Control SystemMrAlbert2009Noch keine Bewertungen

- MB35 TrainingDokument33 SeitenMB35 TrainingNicu LiviuNoch keine Bewertungen

- Clipper and ClamperDokument35 SeitenClipper and ClamperRahul YadavNoch keine Bewertungen

- Electric Motor 5Dokument90 SeitenElectric Motor 5abdulkadhirNoch keine Bewertungen

- IGBTDokument22 SeitenIGBTumeshgangwar100% (1)

- New Trends in Education: Corporate Social ResponsibilityDokument12 SeitenNew Trends in Education: Corporate Social ResponsibilityRahul YadavNoch keine Bewertungen

- Is 10810Dokument1 SeiteIs 10810Rahul YadavNoch keine Bewertungen

- The Indian Navy: Three Dimesional ProwessDokument12 SeitenThe Indian Navy: Three Dimesional ProwessRahul Yadav100% (1)

- Important Dates FinalDokument1 SeiteImportant Dates FinalRahul YadavNoch keine Bewertungen

- Clipper and Clamper: Amity School of EngineeringDokument38 SeitenClipper and Clamper: Amity School of EngineeringRahul YadavNoch keine Bewertungen

- Hdpe Statment Detail PDFDokument1 SeiteHdpe Statment Detail PDFshameemNoch keine Bewertungen

- Ledg24qbr 12w XWW 001awDokument2 SeitenLedg24qbr 12w XWW 001awShahid SiddiqueNoch keine Bewertungen

- Blueplanet Argus: DC CombinerDokument2 SeitenBlueplanet Argus: DC Combinermohamad iaalyNoch keine Bewertungen

- Mercury Switch Datasheet PDFDokument1 SeiteMercury Switch Datasheet PDFFidaa JaafrahNoch keine Bewertungen

- ESS ESS KAY ENGG. CO. LTD, KapurthalaDokument26 SeitenESS ESS KAY ENGG. CO. LTD, KapurthalaSavyasachi VatsNoch keine Bewertungen

- ECE 322 CourseHandout - Sp2015Dokument4 SeitenECE 322 CourseHandout - Sp2015Grant HeilemanNoch keine Bewertungen

- Eng - Ademco Accord XPCDokument62 SeitenEng - Ademco Accord XPCAdam ChalklyNoch keine Bewertungen

- 2CV Series For 230 Vac Capacitor Start Motors and 2VR Series For 230 Vac Capacitor Start/Capacitor Run MotorsDokument2 Seiten2CV Series For 230 Vac Capacitor Start Motors and 2VR Series For 230 Vac Capacitor Start/Capacitor Run MotorsmachevallieNoch keine Bewertungen

- Ascon - Rectifier FR 48V-1200WDokument2 SeitenAscon - Rectifier FR 48V-1200Wsebax123Noch keine Bewertungen

- DSE520 Data SheetDokument2 SeitenDSE520 Data Sheettoa87Noch keine Bewertungen

- Chapter1 2 3 BioDokument132 SeitenChapter1 2 3 BioYanendra SahNoch keine Bewertungen

- Group 4 ReportDokument5 SeitenGroup 4 ReportMacrey BwaleiNoch keine Bewertungen

- Lab 8 - Sync Motor (V-Curves Characteristic) PDFDokument3 SeitenLab 8 - Sync Motor (V-Curves Characteristic) PDFzawirNoch keine Bewertungen

- HD100 DS 10 2009Dokument2 SeitenHD100 DS 10 2009Michael J. MongersonNoch keine Bewertungen

- ABZMS 36 EnglischDokument16 SeitenABZMS 36 EnglischPavel IljaschovNoch keine Bewertungen

- HGM180 180HC V1.0 enDokument8 SeitenHGM180 180HC V1.0 enMiguel Angel Pavon CarbonellNoch keine Bewertungen

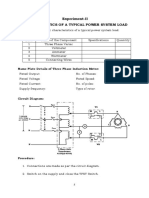

- 2.characteristics of A Typical Power System LoadDokument3 Seiten2.characteristics of A Typical Power System Loadarjuna4306Noch keine Bewertungen

- EZC400N3320Dokument2 SeitenEZC400N3320Σπίθας ΣπιθαμήNoch keine Bewertungen

- Lab Report 5Dokument9 SeitenLab Report 5Leo Marcelo Villalba100% (1)

- Catalogo Retificador SiemensDokument4 SeitenCatalogo Retificador SiemensfabianohyaNoch keine Bewertungen

- Site Planning Data 93E 15-20kvaDokument8 SeitenSite Planning Data 93E 15-20kvaTty SmithNoch keine Bewertungen

- Sauter 3-Way Valve DriveDokument6 SeitenSauter 3-Way Valve DriveDiBernadNoch keine Bewertungen

- PTS1-50-P Product SpecificationsDokument4 SeitenPTS1-50-P Product SpecificationsPhi FeiNoch keine Bewertungen

- 5 Solid State Motor Control DC Motor Speed Control PDFDokument29 Seiten5 Solid State Motor Control DC Motor Speed Control PDFmkdev2004@yahoo.comNoch keine Bewertungen