Beruflich Dokumente

Kultur Dokumente

Lec16 MOS Es

Hochgeladen von

narpatzaCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Lec16 MOS Es

Hochgeladen von

narpatzaCopyright:

Verfügbare Formate

ECE 663

MOSFETs

ECE 663

A little bit of history..

Substrate

Channel

Drain

Insulator

Gate

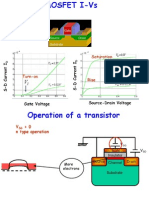

Operation of a transistor

V

SG

> 0

n type operation

Positive gate bias attracts electrons into channel

Channel now becomes more conductive

More

electrons

Source

V

SD

V

SG

Substrate

Channel

Drain

Insulator

Gate

Operation of a transistor

Transistor turns on at high gate voltage

Transistor current saturates at high drain bias

Source

V

SD

V

SG

Substrate

Channel

Drain

Insulator

Gate

Source

V

SD

V

SG

Start with a MOS capacitor

ECE 663

MIS Diode (MOS capacitor) Ideal

W

Questions

What is the MOS capacitance? Q

S

(

S

)

What are the local conditions during inversion?

S,cr

How does the potential vary with position? (x)

How much inversion charge is generated at the surface? Q

inv

(x,

S

)

Add in the oxide: how does the voltage divide?

S

(V

G

),

ox

(V

G

)

How much gate voltage do you need to invert the channel? V

TH

How much inversion charge is generated by the gate? Q

inv

(V

G

)

Whats the overall C-V of the MOSFET? Q

S

(V

G

)

ECE 663

E

C

E

F

E

V

E

i

Ideal MIS Diode n-type, V

appl

=0

Assume Flat-band

at equilibrium

q|

S

ECE 663

0

2

= |

.

|

\

|

+ _ | |

B

g

m ms

q

E

Ideal MIS Diode n-type, V

appl

=0

ECE 663

Ideal MIS Diode p-type, V

appl

=0

ECE 663

Ideal MIS Diode p-type, V

appl

=0

0

2

= |

.

|

\

|

+ + _ | |

B

g

m ms

q

E

ECE 663

Accumulation

Pulling in majority carriers at surface

ECE 663

But this increases the barrier for

current flow !!

n

+

p n

+

ECE 663

Depletion

ECE 663

Need CB to dip below E

F

.

Once below by

B

, minority carrier density trumps the intrinsic density.

Once below by 2

B

, it trumps the major carrier density (doping) !

Inversion

B

ECE 663

Sometimes maths can help

ECE 663

P-type semiconductor V

appl

=0

Convention for p-type: positive if bands bend down

ECE 663

Ideal MIS diode p-type

|

= = = = e n e n e n e n n

p

kT q

p

kT E q E

i

kT E E

i p

F i F i

0

/

0

/ ) ( / ) (

'

|

= = e p e p p

p

kT q

p p 0

/

0

kT

q

|

CB moves towards E

F

if > 0 n increases

VB moves away from E

F

if > 0 p decreases

ECE 663

Ideal MIS diode p-type

At the semiconductor surface, =

s

s

e n n

p s

|

=

0

s

e p p

p s

|

=

0

s

< 0 - accumulation of holes

s

=0 - flat band

B

>

s

>0 depletion of holes

s

=

B

- intrinsic concentration n

s

=p

s

=n

i

s

>

B

Inversion (more electrons than holes)

ECE 663

Surface carrier concentration

s

e n n

p s

|

=

0

s

e p p

p s

|

=

0

E

C

E

F

ECE 663

Want to find , E-field, Capacitance

Solve Poissons equation to get E field, potential based on

charge density distribution(one dimension)

s

s

dx

d

dx

d

D

dx

d

k

c =

= E

E

= c = c = E V

/

1 / /

2

2

0

) ( ) (

p p A D

n p N N q x + =

+

E

E

E

ECE 663

Away from the surface, = 0

and

0 0p p A D

p n N N =

+

| |

= e n e p n p

p p p p 0 0

( ) ) 1 ( ) 1 (

0 0

2

2

c

=

| |

e n e p

q

dx

d

p p

s

ECE 663

Solve Poissons equation:

( ) ) 1 ( ) 1 (

0 0

2

2

c

=

| |

e n e p

q

dx

d

p p

s

E = -d/dx

d

2

/dx

2

= -dE/dx

= (dE/d).(-d/dx)

= EdE/d

( ) ) 1 ( ) 1 (

0 0

2

2

c

=

| |

e n e p

q

dx

d

p p

s

EdE/d

ECE 663

Do the integral:

LHS:

RHS:

Get expression for E field (d/dx):

dx

d

x

x

xdx

x

=

}

=

0

2

2

} }

|

x x

x

dx dx e

0 0

,

( )( )

(

| + | + |

.

|

\

|

c

|

|

.

|

\

|

=

| |

1 1

2

0

0 0

2

2

e

p

n

e

qp

q

kT

E

p

p

s

p

field

Solve Poissons equation:

ECE 663

( ) ( )

2

1

0

0

0

0

1 1 ,

(

| + | + =

|

|

.

|

\

|

|

| |

e

p

n

e

p

n

F

p

p

p

p

Define:

|

c

0

2

0 p

s

p

s

D

qp q p

kT

L

Debye Length

Then:

|

|

.

|

\

|

| =

0

0

,

2

p

p

D

field

p

n

F

qL

kT

E

+ for > 0 and for < 0

> 0

E > 0

< 0

E < 0

ECE 663

|

|

.

|

\

|

| = c =

0

0

,

2

p

p

s

D

S s s

p

n

F

qL

kT

E Q

Use Gauss Law to find

surface charge per unit

area

( )( )

2

1

0

0

1 1

2

(

| + | + =

| |

s

p

p

s

D

s

s S

e

p

n

e

qL

kT

Q

ECE 663

Accumulation to depletion to strong Inversion

For negative , first term in F dominates exponential

For small positive , second term in F dominates - \

As gets larger, second exponential gets big

1

0

0

|

p

p

p

e n

B

= (kT/q)ln(N

A

/n

i

) = (1/|)ln(p

p0

/p

p0

n

p0

)

(n

p0

/p

p0

) = e

-2|

B

S

> 2

B

Questions

What is the MOS capacitance? Q

S

(

S

)

What are the local conditions during inversion?

S,cr

How does the potential vary with position? (x)

How much inversion charge is generated at the surface? Q

inv

(x,

S

)

Add in the oxide: how does the voltage divide?

S

(V

G

),

ox

(V

G

)

How much gate voltage do you need to invert the channel? V

TH

How much inversion charge is generated by the gate? Q

inv

(V

G

)

Whats the overall C-V of the MOSFET? Q

S

(V

G

)

ECE 663

Charges, fields, and potentials

Charge on metal = induced surface charge in semiconductor

No charge/current in insulator (ideal)

metal insul semiconductor

depletion

inversion

S A n M

Q W qN Q Q = + =

ECE 663

Electric Field

Electrostatic Potential

Charges, fields, and potentials

ECE 663

Electric Field

Electrostatic Potential

Depletion Region

( )( )

(

| + | + |

.

|

\

|

c

|

|

.

|

\

|

=

| |

1 1

2

0

0 0

2

2

e

p

n

e

qp

q

kT

E

p

p

s

p

field

ECE 663

Electric Field

Electrostatic Potential

=

s

(1-x/W)

2

W

max

= \2c

s

(2

B

)/qN

A

B

= (kT/q)ln(N

A

/n

i

)

Depletion Region

Questions

What is the MOS capacitance? Q

S

(

S

)

What are the local conditions during inversion?

S,cr

How does the potential vary with position? (x)

How much inversion charge is generated at the surface? Q

inv

(x,

S

)

Add in the oxide: how does the voltage divide?

S

(V

G

),

ox

(V

G

)

How much gate voltage do you need to invert the channel? V

TH

How much inversion charge is generated by the gate? Q

inv

(V

G

)

Whats the overall C-V of the MOSFET? Q

S

(V

G

)

Couldnt we just solve

this exactly?

U = |

U

S

= |

S

U

B

= |

B

Exact Solution

d/dx = -(\2kT/qL

D

)F(

B

,n

p0

/p

p0

)

dU/F(U) = x/L

D

(

]

U

U

S

F(U) = [e

U

B

(e

-U

-1+U)-e

-U

B

(e

U

-1-U)]

1/2

Exact Solution

dU/F(U,U

B

) = x/L

D

(

]

U

U

S

F(U,U

B

) = [e

U

B

(e

-U

-1+U) + e

-U

B

(e

U

-1-U)]

1/2

= qn

i

[e

U

B

(e

-U

-1) e

-U

B

(e

U

-1)]

Exact Solution

N

A

= 1.67 x 10

15

Q

inv

~ 1/(x+x

0

)

o

x

0

~ L

D

. factor

Questions

What is the MOS capacitance? Q

S

(

S

)

What are the local conditions during inversion?

S,cr

How does the potential vary with position? (x)

How much inversion charge is generated at the surface? Q

inv

(x,

S

)

Add in the oxide: how does the voltage divide?

S

(V

G

),

ox

(V

G

)

How much gate voltage do you need to invert the channel? V

TH

How much inversion charge is generated by the gate? Q

inv

(V

G

)

Whats the overall C-V of the MOSFET? Q

S

(V

G

)

ECE 663

Threshold Voltage for Strong Inversion

Total voltage across MOS structure= voltage across

dielectric plus

s

B

i

S

S i T

C

Q

V inversion strong V + = + = 2 ) _ (

) 2 ( 2

) ( 2

) (

max B A s

A

s s

A A S

qN

qN

inv

qN W qN SI Q c =

c

= =

B

i

B A s

T

C

qN

V +

c

= 2

) 2 ( 2

c

ox

V

i

/t

ox

= c

s

s

/(W/2) Before Inversion

After inversion there is a discontinuity in D due to surface Q

inv

V

ox

(at threshold) = c

s

(2

B

)/(W

max

/2)C

i

=

ECE 663

Notice Boundary Condition !!

B

i

B A s

T

C

qN

V +

c

= 2

) 2 ( 2

Local Potential vs Gate voltage

V

G

= V

fb

+

s

+ (k

s

t

ox

/k

ox

) (2kTN

A

/c

0

k

s

)[|

s

+ e

|(

s

-2

B

)

]

1/2

Initially, all voltage drops across channel (blue curve). Above threshold,

channel potential stays pinned to 2

B

, varying only logarithmically, so that

most of the gate voltage drops across the oxide (red curve).

ox

s

Look at Effective charge width

Initially, a fast increasing channel potential drops across

increasing depletion width

Eventually, a constant potential drops across a decreasing

inversion layer width, so field keeps increasing and thus

matches increasing field in oxide

~W

dm

/2

~t

inv

Questions

What is the MOS capacitance? Q

S

(

S

)

What are the local conditions during inversion?

S,cr

How does the potential vary with position? (x)

How much inversion charge is generated at the surface? Q

inv

(x,

S

)

Add in the oxide: how does the voltage divide?

S

(V

G

),

ox

(V

G

)

How much gate voltage do you need to invert the channel? V

TH

How much inversion charge is generated by the gate? Q

inv

(V

G

)

Whats the overall C-V of the MOSFET? Q

S

(V

G

)

Charge vs Local Potential

Q

s

(2c

0

k

s

kTN

A

)[|

s

+ e

|(

s

-2

B

)

]

1/2

Beyond threshold, all charge goes to inversion layer

How do we get the curvatures?

EXACT

Add other terms and keep

Leading term

Inversion Charge vs Gate voltage

Q ~ e

|(

s

-2

B)

,

s

-

2

B

~ log(V

G

-V

T

)

Exponent of a logarithm gives a linear variation of Q

inv

with V

G

Q

inv

= -C

ox

(V

G

-V

T

)

Why C

ox

?

Questions

What is the MOS capacitance? Q

S

(

S

)

What are the local conditions during inversion?

S,cr

How does the potential vary with position? (x)

How much inversion charge is generated at the surface? Q

inv

(x,

S

)

Add in the oxide: how does the voltage divide?

S

(V

G

),

ox

(V

G

)

How much gate voltage do you need to invert the channel? V

TH

How much inversion charge is generated by the gate? Q

inv

(V

G

)

Whats the overall C-V of the MOSFET? Q

S

(V

G

)

ECE 663

Capacitance

( )

|

|

.

|

\

|

|

(

|

.

|

\

|

+

c

=

c

c

=

| |

0

0

0

0

,

1 1

2

p

p

S

p

p

D

S S

D

p

n

F

e

p

n

e

L

Q

C

s s

For

s

=0 (Flat Band):

D

S

D

L

band flat C

c

= ) _ (

Expand exponentials..

........

! 3 ! 2

1

3 2

+ + + + =

x x

x e

x

ECE 663

Capacitance of whole structure

Two capacitors in series:

C

i

- insulator

C

D

- Depletion

D i

C C C

1 1 1

+ = OR

D i

D i

C C

C C

C

+

=

d

C

i

i

c

ECE 663

Capacitance vs Voltage

ECE 663

Flat Band Capacitance

Negative voltage = accumulation C~C

i

Zero voltage Flat Band

i

D

s

i

s i

D i s

D

s i

D i FB

L d

L d

L d

C C C c

c

c

+

=

c c

c + c

=

c

+

c

= + =

1 1 1 1 1

FB

C C V = = =0 0

D

i

FB

L d

C

s

i

c

c

+

c

=

ECE 663

CV

As voltage is increased, C goes through minimum

(weak inversion) where d/dQ is fairly flat

C will increase with onset of strong inversion

Capacitance is an AC measurement

Only increases when AC period long wrt minority

carrier lifetime

At high frequency, carriers cant keep up dont

see increased capacitance with voltage

For Si MOS, high frequency = 10-100 Hz

ECE 663

CV Curves Ideal MOS Capacitor

max

'

min

W d

C

s

i

i

c

c

+

c

=

ECE 663

But how can we operate gate at

todays clock frequency (~ 2 GHz!)

if we cant generate minority

carriers fast enough (> 100 Hz) ?

ECE 663

MOScap vs MOSFET

ECE 663

Substrate

Drain

Insulator

Gate

Source Channel

Substrate

Insulator

Gate

Channel

Minority carriers generated by

RG, over minority carrier lifetime

~ 100s

So C

inv

can be << C

ox

if fast gate

switching (~ GHz)

Majority carriers pulled in

from contacts (fast !!)

C

inv

= C

ox

MOScap vs MOSFET

ECE 663

Example Metal-SiO

2

-Si

N

A

= 10

17

/cm

3

At room temp kT/q = 0.026V

n

i

= 9.65x10

9

/cm

3

c

s

= 11.9x1.85x10

-14

F/cm

( )

m cm W

X x

x X x x

N q

n

N

kT

W

A

i

A

s

= =

=

|

.

|

\

|

c

=

1 . 0 10

10 10 6 . 1

10 65 . 9 10 ln 026 . 0 10 85 . 8 9 . 11

ln 4

5

max

17 19

9 17 14

2

max

ECE 663

Example Metal-SiO

2

-Si

d=50 nm thick oxide=10

-5

cm

c

i

=3.9x8.85x10

-14

F/cm

( )

Volts inv

x

x x x

C

W qN

V

C

C

cm F x

x

x x

W d

C

Volts

x

x x

n

N

q

kT

inv

cm F x

x x

d

C

s B

i

A

TH

i

i

i

A

B s

i

i

s

i

07 . 1 84 . 0 23 . 0 ) (

10 9 . 6

10 10 10 6 . 1

2

13 . 0

/ 10 1 . 9

10 9 . 11 9 . 3 10 5

10 85 . 8 9 . 3

84 . 0

10 65 . 9

10

ln 026 . 0 2 ln

2

2 ) (

/ 10 9 . 6

10

10 85 . 8 9 . 3

7

5 17 19

max

'

min

2 8

5 7

14

max

'

min

9

17

2 7

5

14

= + = + = + =

=

=

+

=

+

c

=

= |

.

|

\

|

= |

.

|

\

|

= =

= =

c

=

c

c

ECE 663

Real MIS Diode: Metal(poly)-Si-SiO

2

MOS

Work functions of gate and semiconductor are

NOT the same

Oxides are not perfect

Trapped, interface, mobile charges

Tunneling

All of these will effect the CV characteristic and

threshold voltage

ECE 663

Band bending due to work function difference

ms FB

V | =

ECE 663

Work Function Difference

q|

s

=semiconductor work function =

difference between vacuum and Fermi level

q|

m

=metal work function

q|

ms

=(q|

m

- q|

s

)

For Al, q|

m

=4.1 eV

n

+

polysilicon q|

s

=4.05 eV

p

+

polysilicon q|

s

=5.05 eV

q|

ms

varies over a wide range depending on

doping

ECE 663

ECE 663

SiO

2

-Si Interface Charges

ECE 663

Standard nomenclature for Oxide charges:

Q

M

=Mobile charges (Na+/K+) can cause

unstable threshold shifts cleanliness

has eliminated this issue

Q

OT

=Oxide trapped charge Can be anywhere

in the oxide layer. Caused by broken

Si-O bonds caused by radiation damage

e.g. alpha particles, plasma processes,

hot carriers, EPROM

ECE 663

Q

F

= Fixed oxide charge positive charge layer

near (~2mm) Caused by incomplete

oxidation of Si atoms(dangling bonds)

Does not change with applied voltage

Q

IT

=Interface trapped charge. Similar in origin

to Q

F

but at interface. Can be pos, neg,

or neutral. Traps e

-

and h during device

operation. Density of Q

IT

and Q

F

usually

correlated-similar mechanisms. Cure

is H anneal at the end of the process.

Oxide charges measured with C-V methods

ECE 663

Effect of Fixed Oxide Charges

ECE 663

ECE 663

Surface Recombination

Lattice periodicity broken at surface/interface mid-gap E levels

Carriers generated-recombined per unit area

ECE 663

Interface Trapped Charge - Q

IT

Surface states R-G centers caused by disruption of lattice

periodicity at surface

Trap levels distributed in band gap, with Fermi-type distributed:

Ionization and polarity will depend on applied voltage (above or

below Fermi level

Frequency dependent capacitance due to surface recombination

lifetime compared with measurement frequency

Effect is to distort CV curve depending on frequency

Can be passivated w/H anneal 10

10

/cm

2

in Si/SiO

2

system

kT E E

D D

D

D F

e g N

N

/ ) (

1

1

+

+

=

ECE 663

Effect of Interface trapped charge on C-V curve

ECE 663

a ideal

b lateral shift Q oxide, |

ms

c distorted by Q

IT

ECE 663

Non-Ideal MOS capacitor C-V curves

Work function difference and oxide charges shift CV curve in

voltage from ideal case

CV shift changes threshold voltage

Mobile ionic charges can change threshold voltage as a function of

time reliability problems

Interface Trapped Charge distorts CV curve frequency

dependent capacitance

Interface state density can be reduced by H annealing in Si-Si0

2

Other gate insulator materials tend to have much higher

interface state densities

ECE 663

All of the above.

For the three types of oxide charges the CV curve is shifted

by the voltage on the capacitor Q/C

When work function differences and oxide charges are

present, the flat band voltage shift is:

(

d

i

e ch oxide FB

dx x x

d C

V

0

arg _

) (

1 1

( )

i

ot m f

ms FB

C

Q Q Q

V

| =

Some important equations in the

inversion regime (Depth direction)

V

T

= |

ms

+ 2

B

+

ox

W

dm

= \[2c

S

(2

B

)/qN

A

]

Q

inv

= C

ox

(V

G

- V

T

)

ox

= Q

s

/C

ox

Q

s

= qN

A

W

dm

V

T

= |

ms

+ 2

B

+ (\[4c

S

B

qN

A

] - Q

f

+ Q

m

+ Q

ot

)/C

ox

Substrate

Channel

Drain

Insulator

Gate

Source

x

Das könnte Ihnen auch gefallen

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (587)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (890)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Low Voltage Switchgear Specification GuideDokument6 SeitenLow Voltage Switchgear Specification GuidejendrikoNoch keine Bewertungen

- 07 - Arc FlashDokument53 Seiten07 - Arc Flashchanchai T100% (4)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- TachometerDokument36 SeitenTachometerSheena Mary100% (1)

- Lab 1: Introduction To Combinational Design: EquipmentsDokument42 SeitenLab 1: Introduction To Combinational Design: EquipmentsnarpatzaNoch keine Bewertungen

- Lab 1: Introduction To Combinational Design: EquipmentsDokument42 SeitenLab 1: Introduction To Combinational Design: EquipmentsnarpatzaNoch keine Bewertungen

- Allen Holberg SolutionsDokument509 SeitenAllen Holberg SolutionsLatha Venkatesh100% (1)

- LV Hands OnDokument120 SeitenLV Hands Onefx8Noch keine Bewertungen

- Sensor NotesDokument86 SeitenSensor NotesNasos MasourasNoch keine Bewertungen

- Lec17 Mosfet IVDokument49 SeitenLec17 Mosfet IVEdward Allan MangubatNoch keine Bewertungen

- HeinzDokument159 SeitenHeinznarpatzaNoch keine Bewertungen

- 29 128 Manual 01 10-V3-Entire-manualDokument160 Seiten29 128 Manual 01 10-V3-Entire-manualnarpatzaNoch keine Bewertungen

- Lecturenote3 MosfetchapterDokument48 SeitenLecturenote3 MosfetchapterBayron Eduardo CentenoNoch keine Bewertungen

- SEQUENTIAL LOGIC FUNDAMENTALSDokument10 SeitenSEQUENTIAL LOGIC FUNDAMENTALSnarpatzaNoch keine Bewertungen

- Introduction To Logic Gates: 3.2 ObjectivesDokument4 SeitenIntroduction To Logic Gates: 3.2 ObjectivesnarpatzaNoch keine Bewertungen

- Combinational Logic CircuitsDokument4 SeitenCombinational Logic CircuitsnarpatzaNoch keine Bewertungen

- Heat PimpsDokument14 SeitenHeat PimpsnarpatzaNoch keine Bewertungen

- SpiceDokument61 SeitenSpiceZul Kharn AinNoch keine Bewertungen

- Absorption CoolingDokument11 SeitenAbsorption CoolingnarpatzaNoch keine Bewertungen

- 1 FTPDokument8 Seiten1 FTPnarpatzaNoch keine Bewertungen

- Microsoft Excel Study MaterialDokument49 SeitenMicrosoft Excel Study Materialvinodksrini007Noch keine Bewertungen

- WANG Ruonan ThesisDokument143 SeitenWANG Ruonan ThesisnarpatzaNoch keine Bewertungen

- ECE111 - Analog Electronics: Sandeep Saini Gaurav ChatterjeeDokument27 SeitenECE111 - Analog Electronics: Sandeep Saini Gaurav ChatterjeeAAYUSH SHUKLANoch keine Bewertungen

- Power Transformer: Laminated CoreDokument8 SeitenPower Transformer: Laminated Coreraymond baliteNoch keine Bewertungen

- Datasheet MOC301Dokument6 SeitenDatasheet MOC301Vam PireNoch keine Bewertungen

- Vantage® 500-I (Disel Engine+ElectricDokument3 SeitenVantage® 500-I (Disel Engine+ElectricKumar RNoch keine Bewertungen

- Design of A Boost Converter: Department of Electrical Engineering National Institute of Technology RourkelaDokument31 SeitenDesign of A Boost Converter: Department of Electrical Engineering National Institute of Technology Rourkela2k18-EE-243 Vethushan VinnayagamoorththiNoch keine Bewertungen

- LC1F115 Schneider Electric-DataSheetDokument3 SeitenLC1F115 Schneider Electric-DataSheetRAUL ORTIZNoch keine Bewertungen

- Mel G632 224Dokument2 SeitenMel G632 224Krishna KishoreNoch keine Bewertungen

- CMOS (Complementary Metal Oxide Semiconductor)Dokument5 SeitenCMOS (Complementary Metal Oxide Semiconductor)Hirakjyoti GoswamiNoch keine Bewertungen

- UOT-Electrical Specifications-EDokument72 SeitenUOT-Electrical Specifications-Enadher albaghdadiNoch keine Bewertungen

- Calculating parameters for a basic modern transistor amplifierDokument189 SeitenCalculating parameters for a basic modern transistor amplifierionioni2000Noch keine Bewertungen

- Online UPS User ManualDokument30 SeitenOnline UPS User ManualaxsalazarNoch keine Bewertungen

- BLY89Dokument12 SeitenBLY89sonyscribeNoch keine Bewertungen

- Technical Manual SIMPLY HP - ING - Sez.0 - IndexDokument2 SeitenTechnical Manual SIMPLY HP - ING - Sez.0 - Indexfortroni0% (1)

- ACS 2000AFE VC SW Troubleshooting GuideDokument67 SeitenACS 2000AFE VC SW Troubleshooting GuideJean Carlos da SilvaNoch keine Bewertungen

- 2-VLD IC HistoryDokument7 Seiten2-VLD IC HistorybrincyNoch keine Bewertungen

- Microwind3.1 Design Rules For 45NM Cmos TechnologyDokument44 SeitenMicrowind3.1 Design Rules For 45NM Cmos TechnologyOkta_BSD100% (1)

- PI734GDokument8 SeitenPI734G3efooNoch keine Bewertungen

- Adjust Excitation Equipment Voltage RegulatorsDokument12 SeitenAdjust Excitation Equipment Voltage RegulatorskirananneNoch keine Bewertungen

- KLM EASA Cat B Module 6 Book 2 Iss 0 Rev 3 SecuredDokument42 SeitenKLM EASA Cat B Module 6 Book 2 Iss 0 Rev 3 SecuredNadirNoch keine Bewertungen

- STW21NM50N MosfetDokument16 SeitenSTW21NM50N MosfetrigowNoch keine Bewertungen

- Electronic Components and DevicesDokument6 SeitenElectronic Components and DevicesSelvam MNoch keine Bewertungen

- CAPCICTOR - Pricelist 2023Dokument32 SeitenCAPCICTOR - Pricelist 2023MaharudraMahajanNoch keine Bewertungen

- Condition Based Monitoring For HT Motor (Inhouse) S.No Name of Test DescriptionDokument11 SeitenCondition Based Monitoring For HT Motor (Inhouse) S.No Name of Test DescriptionYadav AkhileshNoch keine Bewertungen

- Silicon On Insulator (Sol) TechnologyDokument17 SeitenSilicon On Insulator (Sol) TechnologyCharan MsdNoch keine Bewertungen

- Aquavar Iom PDFDokument84 SeitenAquavar Iom PDFFulton Xavier ZambranoNoch keine Bewertungen

- Registered Electrical Workers As at 15th May 2020Dokument66 SeitenRegistered Electrical Workers As at 15th May 2020pius ouna100% (1)

- M o D U L e 0 4 - 0 1 - 0 1 A Electronic Fundamentals: DiodesDokument33 SeitenM o D U L e 0 4 - 0 1 - 0 1 A Electronic Fundamentals: DiodesИлларион ПанасенкоNoch keine Bewertungen