Beruflich Dokumente

Kultur Dokumente

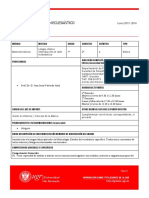

Arquitectura de Computadoras Tema 2.3

Hochgeladen von

Joel ZeaCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Arquitectura de Computadoras Tema 2.3

Hochgeladen von

Joel ZeaCopyright:

Verfügbare Formate

DISEO DE UN

PROCESADOR

SEGMENTADO.

GESTIN DE RIESGOS DE

DATOS, CONTROL Y

ESTRUCTURALES

GENERALIDADES

RcRa op Rb

La distribucin de tareas nos lleva a un

cause de cuatro etapas:

IF (Instruction fetch)

ID/OF (Instruction Decode/Operand Fetch)

ALU

OS (Operand Store)

Existen una serie de condiciones (riesgos)

que pueden hacer que el cauce no genere

los resultados correctos, a no ser que se

interrumpa su funcionamiento durante un

nmero de ciclos determinado. Lo que

llevara a la disminucin de rendimiento del

cauce.

Tipos de riesgos:

Riesgos de datos

Riesgos de control

Riesgos estructurales

Riesgos de Datos: Surgen por las

dependencias entre los operandos y resultados

de operaciones anteriores o posteriores.

Riesgos de control: Se originan a partir de

instrucciones de salto condicional, ya que segn

su resultado, determinan la secuencia de

instrucciones que se ejecutaran tras ellas.

Riesgos estructurales: Llamados tambin de

colisiones, se produce cuando instrucciones

diferentes pueden necesitar un recurso al mismo

tiempo.

RIESGOS DE DATOS

TIPOS:

RAW (Read After Write)

WAR (Write After Read)

WAW (Write After Write)

Riegos de datos tipo RAW

Se producen cuando una instruccin utiliza

como uno de sus operandos, el resultado

que obtiene de una instruccin previa:

Almacenamiento

1 2

W R

R2 = R1 + R2

R1 = R2 + R3

Read Oper Write

t+1 t+2 t+3 t+4

Read Write

Riegos de datos tipo WAR

Se producen cuando una instruccin utiliza

como destino, un operando que se utiliza

en una instruccin previa:

Almacenamiento

2 1

W R

R2 = R1 + R2

R1 = R2 + R3

Read Oper Write

t+1 t+2 t+3 t+4

Read Write

Riegos de datos tipo WAW

Se producen cuando una instruccin utiliza

como destino, el registro resultado de una

instruccin previa:

Almacenamiento

1 2

W W

R2 = R1 + R2

R2 = R4 + R3

Read Oper Write

t+1 t+2 t+3 t+4

Read Write

Conclusin:

Segn la distribucin de etapas del cauce, la

escritura en el banco de registros siempre se

hace en la ultima etapa; cuando la instruccin

escriba su resultado, todas las instrucciones

anteriores habrn terminado, de tal manera que

los riesgos del tipo WAR y WAW no causan

ningn error en su ejecucin.

OF/ID OS

OF/ID OS

t

t+1 t+2 t+3 t+4

R2 = R1 + R2

R2 = R4 + R3

SOLUCIONES PARA LAS

DEPENDENCIAS DE DATOS DE

TIPO RAW

Se pueden desarrollar mediante Hardware

o Software. Para elegir entre una de ellas

se debe tener en cuenta el rendimiento.

Las alternativas para evitar los problemas

de los riesgos RAW son:

Reorganizacin del cdigo

Interbloqueo entre etapas

Atajos

REORGANIZACIN DEL

CDIGO

Colocar instrucciones independientes,

entre instrucciones con dependencia RAW,

que retracen la segunda instruccin con

respecto a la primera.

Read Oper Write

t+1 t+2 t+3 t+4

R4 = R1 + R2

R2 = R4 + R5 Read Write

R3 = R1 + R2

REORGANIZACIN DEL

CDIGO

Colocar NOPs, entre instrucciones con

dependencia RAW, que retracen la

segunda instruccin con respecto a la

primera.

Read Oper Write

t+1 t+2 t+3 t+4

R4 = R1 + R2

R2 = R4 + R3 Read Write

NOP

INTERBLOQUEO ENTRE

ETAPAS

Se introduce elementos Hardware en el

cauce que detecten dependencias. La

etapa de lectura de operandos se bloquea

para la instruccin paralela.

Read Oper Write

t+1 t+2 t+3 t+4

R4 = R1 + R2

R2 = R4 + R3

Read Write

ATAJOS (BYPASS)

Implementa el Hardware necesario para

detectar las dependencias y adems las

enruta para mandar los datos donde son

necesarios (Datos anticipados).

Read Oper Write

t+1 t+2 t+3 t+4

R4 = R1 + R2

R2 = R4 + R3 Read Write

IMPLEMENTACIN DE LAS

INSTRUCCIONES DE SALTO

El PC es el que determina la direccin del

destino del salto.

Para ver si una condicin es cierta, se ha

implementado por hardware un circuito que lo

detecte y adems permita ingresar a la ALU,

como un operando ms, el contenido del PC.

El PC se auto incrementar si no salta, o

modificara su contenido de acuerdo a un offset

(Salto).

IMPLEMENTACIN DE LAS

INSTRUCCIONES DE SALTO

Si la condicin es cierta, el salto se

efectuara, por lo que las instrucciones

paralelas siguientes que se estaban

desarrollando son indeseables:

ALU

t+1 t+2 t+3 t+4

R3 = R1 + R2

PC+(R6)

Salto

bz R6

indeseables

CC

SOLUCIONES A LAS

INSTRUCCIONES DE SALTO

Escribir Nops en las posiciones donde las

instrucciones son indeseables.

Colocar instrucciones independientes, para

que completen su ejecucin.

Colocar en la instruccin explcitamente el

registro en que se verificara la condicin

(b cond Ra,off).

IMPLEMENTACIN DE LAS

INSTRUCCIONES DE ACCESO A

MEMORIA

Las instrucciones de carga y

almacenamiento son utilizadas

frecuentemente en un programa.

Se captan los contenidos de los registros

donde esta la informacin necesaria para

calcular la direccin.

Se calcula la direccin efectiva a partir de

dichos contenidos. (necesita un ciclo mas)

IMPLEMENTACIN DE LAS

INSTRUCCIONES DE ACCESO A

MEMORIA

Existen nuevos registros en Hardware:

DMAR: Registro de la direccin de la memoria

de datos.

SDMR: Registro a escribir en la memoria de

datos.

LDMR: Registro a cargar de la memoria de

datos.

SOLUCIONES:

Colocar instrucciones independientes si se

pudiera para evitar que se pierda un ciclo,

si no se pudiera colocar un Nop.

Incrementar el nmero ciclos de reloj por

instruccin. Teniendo una etapa dedicada

al acceso sobre la carga y almacenamiento

de la memoria.

Das könnte Ihnen auch gefallen

- RTR 160 4v-4t Nafta - User-ManualDokument122 SeitenRTR 160 4v-4t Nafta - User-ManualVentas Moto Boedo100% (1)

- Patron Funcional Sueño DescansoDokument4 SeitenPatron Funcional Sueño DescansoJoel ZeaNoch keine Bewertungen

- Laboratorio de Electronica Analoga 5Dokument7 SeitenLaboratorio de Electronica Analoga 5Joel ZeaNoch keine Bewertungen

- Estudio de Racg 2020 - Informe Final PDFDokument43 SeitenEstudio de Racg 2020 - Informe Final PDFJoel ZeaNoch keine Bewertungen

- CaticDokument507 SeitenCaticgustavoscribd2012100% (1)

- Curso Omicron Prueba de Relés de Onda PortadoraDokument24 SeitenCurso Omicron Prueba de Relés de Onda PortadoraJoel ZeaNoch keine Bewertungen

- Redes EmersonDokument42 SeitenRedes EmersonJoel ZeaNoch keine Bewertungen

- Orgullo y HumildadDokument18 SeitenOrgullo y HumildadJoel ZeaNoch keine Bewertungen

- Alarma Con Envío de SmsDokument8 SeitenAlarma Con Envío de SmsJoel ZeaNoch keine Bewertungen

- Alarma Con Envío de SmsDokument26 SeitenAlarma Con Envío de SmsJoel ZeaNoch keine Bewertungen

- Alarma Con Envío de SmsDokument8 SeitenAlarma Con Envío de SmsJoel ZeaNoch keine Bewertungen

- Domótica Usando El PIC16F877ADokument10 SeitenDomótica Usando El PIC16F877AJoel Zea50% (2)

- El Cincel de DiosDokument4 SeitenEl Cincel de DiosJoel ZeaNoch keine Bewertungen

- Letras CD Antologia de Cantos EucaristicosDokument17 SeitenLetras CD Antologia de Cantos Eucaristicosjrangel_leonNoch keine Bewertungen

- Exposicion Arqui Sasori ZeaDokument44 SeitenExposicion Arqui Sasori ZeaJoel ZeaNoch keine Bewertungen

- Informe Final MacDokument42 SeitenInforme Final MacJoel ZeaNoch keine Bewertungen

- Incubadora - ProyectosDokument5 SeitenIncubadora - ProyectosJerry Rodriguez FloresNoch keine Bewertungen

- Sensores de ConductividadDokument31 SeitenSensores de ConductividadJoel ZeaNoch keine Bewertungen

- Concentracion QuimicaDokument24 SeitenConcentracion QuimicaJoel ZeaNoch keine Bewertungen

- Lavado de DientesDokument1 SeiteLavado de DientesJoel ZeaNoch keine Bewertungen

- MAC InformeDokument12 SeitenMAC InformeJoel ZeaNoch keine Bewertungen

- Aprovechamiento de La Energia EolicaDokument44 SeitenAprovechamiento de La Energia EolicaJoel ZeaNoch keine Bewertungen

- Ing - Rad 2Dokument20 SeitenIng - Rad 2Joel ZeaNoch keine Bewertungen

- Ing - Rad IDokument40 SeitenIng - Rad IbrangrossmanNoch keine Bewertungen

- EsniDokument17 SeitenEsniJoel ZeaNoch keine Bewertungen

- El Cincel de DiosDokument4 SeitenEl Cincel de DiosJoel ZeaNoch keine Bewertungen

- Rito para La Corona de Adviento 07Dokument6 SeitenRito para La Corona de Adviento 07Joel Zea100% (1)

- AsertividadDokument2 SeitenAsertividadJoel ZeaNoch keine Bewertungen

- Real MaliciaDokument184 SeitenReal MaliciaMatias AguirreNoch keine Bewertungen

- Plan de Trabajo de La Comunidad de Amor Octubre Noviembre y DiciembreDokument1 SeitePlan de Trabajo de La Comunidad de Amor Octubre Noviembre y DiciembreJoel ZeaNoch keine Bewertungen

- Problematicas SocialesDokument15 SeitenProblematicas SocialesAna Luisa Morales BrionesNoch keine Bewertungen

- Lunaria SHDokument1 SeiteLunaria SHPEDRO PABLO DUQUENoch keine Bewertungen

- Informe Taller de Integracion ProfesionalDokument3 SeitenInforme Taller de Integracion ProfesionalmizzioNoch keine Bewertungen

- Mini Excavadora Kubota KX121 3 Alpha SPDokument4 SeitenMini Excavadora Kubota KX121 3 Alpha SPramon hidalgoNoch keine Bewertungen

- Ammann PrimeDokument8 SeitenAmmann PrimeJunior Ortega RomeroNoch keine Bewertungen

- Registró Auxiliar 6 EdaDokument6 SeitenRegistró Auxiliar 6 EdaWalter Quispe AymaNoch keine Bewertungen

- Manual Picaxe 1Dokument31 SeitenManual Picaxe 1JOSE RODOLFO SANDOVAL PINEDANoch keine Bewertungen

- Prueba de matemáticas PISADokument9 SeitenPrueba de matemáticas PISAMamani DanielNoch keine Bewertungen

- Diseño de desvío de río temporal para construcción de presaDokument19 SeitenDiseño de desvío de río temporal para construcción de presaDaniela CalleNoch keine Bewertungen

- Escala CUVE Agresion Escolar PDFDokument10 SeitenEscala CUVE Agresion Escolar PDFDeborah L. Sievens FigueroaNoch keine Bewertungen

- Compilado Proceso PDFDokument318 SeitenCompilado Proceso PDFAngie MirandaNoch keine Bewertungen

- Motivación: de Los Conceptos A Las AplicacionesDokument5 SeitenMotivación: de Los Conceptos A Las AplicacionesAndrea RenneeNoch keine Bewertungen

- AFI - Caso 1Dokument5 SeitenAFI - Caso 1willcalarNoch keine Bewertungen

- Análisis flexibilidad bombas unidades Orthoflow HCM UOPDokument3 SeitenAnálisis flexibilidad bombas unidades Orthoflow HCM UOPcarlos rueda100% (1)

- GEOMETRIADokument37 SeitenGEOMETRIAAndréss CadenaNoch keine Bewertungen

- Calidad 2Dokument10 SeitenCalidad 2Mayra nicol Alvarez sangayNoch keine Bewertungen

- ANUIES OFICIAL NM FacilitadorDokument96 SeitenANUIES OFICIAL NM FacilitadorAlberto FVallesNoch keine Bewertungen

- Lobo EsteparioDokument2 SeitenLobo EsteparioAlejandro ValenciaNoch keine Bewertungen

- Guia Docente Latin EclesiasticoDokument5 SeitenGuia Docente Latin EclesiasticoAngelis Et ArchangelisNoch keine Bewertungen

- Diseño OrganizacionalDokument8 SeitenDiseño OrganizacionalCarlos RomeroNoch keine Bewertungen

- Observaciones A La SSDokument22 SeitenObservaciones A La SSBelfanL.NuñezNoch keine Bewertungen

- Link 208Dokument2 SeitenLink 208JaimeNoch keine Bewertungen

- Capitalismo de vigilancia: Shoshana Zubogg alerta sobre los peligros de la extracción masiva de datosDokument10 SeitenCapitalismo de vigilancia: Shoshana Zubogg alerta sobre los peligros de la extracción masiva de datosAlejandro G. RuffoniNoch keine Bewertungen

- Calculo DiferencialDokument6 SeitenCalculo DiferencialCaRreÑoIJNoch keine Bewertungen

- Modulo de Fisica Grado 10Dokument35 SeitenModulo de Fisica Grado 10YRDZ TUTOSNoch keine Bewertungen

- Maquina Dosificadora de Masa para Elaboracion de HumitasDokument143 SeitenMaquina Dosificadora de Masa para Elaboracion de HumitasdenarNoch keine Bewertungen

- Tarea 1 - Maira MárquezDokument7 SeitenTarea 1 - Maira MárquezMaira MárquezNoch keine Bewertungen

- Reglamento de Evaluación Generales, Jefes y Oficiales Policía BolivianaDokument17 SeitenReglamento de Evaluación Generales, Jefes y Oficiales Policía BolivianaWilliam I.A. Llanos Torrico, MSc.50% (2)

- 1º - E.S.O - Tema 10 - HistoriaDokument3 Seiten1º - E.S.O - Tema 10 - HistoriaToni Martin NogalesNoch keine Bewertungen