Beruflich Dokumente

Kultur Dokumente

Mukherjee Part6

Hochgeladen von

Shahid QureshiCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Mukherjee Part6

Hochgeladen von

Shahid QureshiCopyright:

Verfügbare Formate

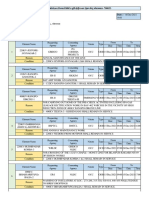

Fault models

Stuck-at-0

0

1

Stuck-at-1

Reset coupling 0 0 Set coupling 1

0

1 1

Inversion coupling 0 1 1

0

Transition /0 0 1 Transition /1

ADR

0 0 Inversion coupling 1 1

0

1

AND bridging 0 1

0 0

1 0 OR bridging 1 1

Neighborhood

pattern sensitive

faults (active)

0

1 0 1

1

0 1

Neighborhood

pattern sensitive

faults (passive)

1

1 1 0

0

0

Address decoder

faults

ADR ADR ADR ADR

Elements of march test

(w0)

x

x

x

x

x

x

x

x

7

6

5

4

3

2

1

0

0

(r1,w0)

1

1

1

1

1

1

1

1

(w1)

(r0,w1)

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0 1

0 1

0 1

0 1

0 1

0 1

0 1

0 1

1 0

1 0

1 0

1 0

1 0

1 0

1 0

1 0

C - algorithm

Number of steps: 10n

Fault coverage: AFs, SAFs, TFs, CFins , CFids

(w0)

(r1,w0)

1

1

1

1

1

1

1

1

(r0,w1)

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0 1

0 1

0 1

0 1

0 1

0 1

0 1

0 1

1 0

1 0

1 0

1 0

1 0

1 0

1 0

1 0

(r0,w1)

0

0

0

0

0

0

0

0

1 0

1 0

1 0

1 0

1 0

1 0

1 0

1 0

(r1,w0)

1

1

1

1

1

1

1

1

0 1

0 1

0 1

0 1

0 1

0 1

0 1

0 1

(r0)

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Checkerboard test and data retention

Designed to test refresh

operations of DRAMs

Maximizes leakage current

and detects leakage faults

Used as data retention test

To be effective it must

consider address

scrambling and layout

1 0 1 0

0 1 0 1

0 1 0 1

1 0 1 0

Data backgrounds for word memories

Multiple data backgrounds to detect coupling and

bridging faults between cells of the same word

For every pair of cells all four combinations are

checked

2 (log

2

w + 1) backgrounds

16 backgrounds for

128-bit wide memory

Normal and inverse

D0 D1 D2 D3 D4 D5 D6 D7

0 0 0 0 0 0 0 0

1 1 1 1 1 1 1 1

0 0 0 0 1 1 1 1

1 1 1 1 0 0 0 0

0 0 1 1 0 0 1 1

1 1 0 0 1 1 0 0

0 1 0 1 0 1 0 1

1 0 1 0 1 0 1 0

Data in word-oriented memory

(w0) (r1,w0) (r0,w1) (r0,w1)

Parallel memory BIST

BIST

mode

Clock

System logic

Address generator

F

S

M

Data generator

Control generator

Start

Hold

Done

Fail

Memory

Serial memory BIST

System logic

Data output

Serial output

Serial input

Address M

0 0 0 0

r0 0 0 0 0

w1 1 0 0 0

r0 1 0 0 0

w1 1 1 0 0

r0 1 1 0 0

w1 1 1 1 0

r0 1 1 1 0

w1 1 1 1 1

r1 1 1 1 1

Minimal logic and routing

Longer test time

Memory

Serial-parallel data interface trade-offs

Memory

Memory Memory

Memory

Memory BIST collar

+

Memory BIST

controller

To / From

TAP controller

Embedded memory BIST collar

mux address / control bus and data lines

local comparator with single pass/fail

local data generator to reduce routing

area and timing problems

local address validation

Memory controller at the top level

TAP controller as test engine

Memory

array

Functional logic

Shared controller and parallel test

Insert collars

Connect them

through memory

test bus

to memory BIST

controller

to TAP

+

Memory BIST

controller

To / From

TAP controller

Memory

array

+

Memory

array

Functional logic

Parallel memory BIST collar

Memory array

Data in Address Data out Ctrl

MBIST mode

Sin

Sout

Clock

= ?

Functional address

BIST address

Functional data

BIST data

Pass / Fail

B

I

S

T

c

o

n

t

r

o

l

F

u

n

c

t

i

o

n

a

l

c

o

n

t

r

o

l

Full-Speed test application

Runs at system clock speeds with single cycle

read/write operations

Uncovers speed-related defects

Reduce test application time.

Addr/Cntrl/

Data

Clock

Memory

Output

Compare

Circuitry

Circuit

Output

Write

Clock

Cycle 1

Clock

Cycle 2

Clock

Cycle 3

Clock

Cycle 4

Clock

Cycle 5

Setup

Read 1

Setup

Write 1

Setup

Read 2

Setup

Read 3

Setup

Write 2

Compare

Read 1

Write 1

Read 2 Read 3

Compare

Read 2

Pass/Fail

Read 2

Pass/Fail

Read 1

Compare

Read 3

Read 1

Diagnostics

Detect failing location/data during test

Should diagnose speed related defects

Two types - Hold and resume, Hold and restart

How it works?

BIST controller stops after 1 (or 2) failures

Fail data is scanned out

BIST session resumes from where it stops (Hold and

resume)

BIST session restarts after fail data is scanned out

(Hold and restart)

Full-speed diagnostics

+

Memory

array

MBIST

controller

ATE

Restart

Diagnostic monitor

Yield improvement with memory redundancy

Memory percentage, defect rate, and redundancy

amount affect yield

Source: Zorian, Rodgers, DATE 2002

Redundancy Yield Improvement

0

10

20

30

40

50

60

70

80

90

100

0 10 20 30 40 50 60 70 80 90 100

Chip Memory Percentage

M

e

m

o

r

y

Y

i

e

l

d

Optimal

Level 3

Redundancy

Level 2

Redundancy

Level 1

Redundancy

No Redundancy

+

Memory BIST

controller

Memory

Array

Redundancy and repair

Extra columns, rows, or rows

and columns

At the end of test - good,

repairable, or non-repairable

Repair data scanned out at

the end of test

Full-Chip memory BIST integration

Assign memories to

controller

(BIST Scheduling)

Memory BIST Generation

(Generate Controller/Collars)

BIST GENERATION

Read in SOC netlist

Identify memories

Insert controllers in the design

Stitch controllers to top-level

BIST INSERTION

Full Chip Memory BIST Control

Block

BIST Block

BIST Block

BIST

Controller

Memory 1

Memory 2

SOC

TDO

MBIST Data

Register

TDI

CLK

TM S

TCK

TRST

TAP Controller

rst_l

test_h

test_done

fail_h

Boundary Scan Register

Programmable algorithms

Selection of algorithms

March1, March2, March3, Unique Address, Checkerboard,

address jumping

Synthesizable algorithms

user defined prior to synthesis

simple language

number of sequences, backgrounds, sequence elements etc.,

Programmable algorithms

defect mechanisms may not be known before fabrication

memory BIST controller implements a class of algorithms

field programmable parameters define active elements of test

sequences

Summary

Key components of a BIST controller

algorithm controller

data background generator

address generator

comparator

Very high quality test of embedded arrays

BIST controller shared across a number of memory

arrays to reduce area

BIST diagnostics helps in gathering failure

information

Built-in repair results in yield improvement

Das könnte Ihnen auch gefallen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- DDR3Dokument52 SeitenDDR3Shahid QureshiNoch keine Bewertungen

- Shahid Qureshi MSEEDokument1 SeiteShahid Qureshi MSEEShahid QureshiNoch keine Bewertungen

- How To Engineer A ResumeDokument2 SeitenHow To Engineer A ResumeShahid QureshiNoch keine Bewertungen

- Homework Problem 1Dokument1 SeiteHomework Problem 1Shahid QureshiNoch keine Bewertungen

- Verilog HDL QUICK Reference Card: EvisionDokument2 SeitenVerilog HDL QUICK Reference Card: EvisionaflapdoodleNoch keine Bewertungen

- A Brief Tour of The Simple Network Management Protocol: CERT® Coordination CenterDokument4 SeitenA Brief Tour of The Simple Network Management Protocol: CERT® Coordination CenterpurushothamkamathNoch keine Bewertungen

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- 5 - Handbook On TCAS - An Indigenous ATP System - April 2021Dokument150 Seiten5 - Handbook On TCAS - An Indigenous ATP System - April 2021AliveluNoch keine Bewertungen

- EmpowermentDokument2 SeitenEmpowermentAndrew C. BrazaNoch keine Bewertungen

- Error Probability For L-Branch Coherent BPSK EqualDokument6 SeitenError Probability For L-Branch Coherent BPSK EqualabhilashNoch keine Bewertungen

- C2-RS232-RS422-RS485-phan 3Dokument25 SeitenC2-RS232-RS422-RS485-phan 3Duc Tri Bui100% (2)

- Iphone 4s Case Design GuidelinesDokument16 SeitenIphone 4s Case Design GuidelinesJayoshomeNoch keine Bewertungen

- Without: Fassi and Innovation: Fassi'S Genetic Code The Key Word Is Flexibility Her Majesty THE F1950Dokument44 SeitenWithout: Fassi and Innovation: Fassi'S Genetic Code The Key Word Is Flexibility Her Majesty THE F1950Leon WongNoch keine Bewertungen

- Library Managemnt Information SystemDokument8 SeitenLibrary Managemnt Information SystemHạnh Nguyễn NgọcNoch keine Bewertungen

- Er Shutdown For 15.12.21 Rev1Dokument8 SeitenEr Shutdown For 15.12.21 Rev1Gitesh PatelNoch keine Bewertungen

- Mid Term Paper Maintenance EngineeringDokument1 SeiteMid Term Paper Maintenance EngineeringKhadeejaNoch keine Bewertungen

- ABC Functional Requirements Doc SampleDokument57 SeitenABC Functional Requirements Doc SampleSharang Bhasin100% (1)

- Aruba AP-300 Series and AP-207: Ellie Huang, Sr. Product Marketing ManagerDokument11 SeitenAruba AP-300 Series and AP-207: Ellie Huang, Sr. Product Marketing Managerarelyta8123Noch keine Bewertungen

- CH09 Maneuver Support (FY22) 12 Oct21Dokument114 SeitenCH09 Maneuver Support (FY22) 12 Oct21geraldwolford1100% (1)

- CH 10Dokument83 SeitenCH 10이잉Noch keine Bewertungen

- 1-CC-Link IE TSN Na EngDokument71 Seiten1-CC-Link IE TSN Na EngThanh Kieu Nguyen ThiNoch keine Bewertungen

- How To Build Your Own Blog With Next - Js and MDXDokument5 SeitenHow To Build Your Own Blog With Next - Js and MDXVinh Quang NguyễnNoch keine Bewertungen

- Crafting Wearables - Blending Technology With Fashion (PDFDrive)Dokument229 SeitenCrafting Wearables - Blending Technology With Fashion (PDFDrive)gopika100% (2)

- Etax - End - User - Manual - TaxpayerDokument33 SeitenEtax - End - User - Manual - TaxpayerAdedeji OluwatobilobaNoch keine Bewertungen

- Manual VsDokument44 SeitenManual VsMax WilsonNoch keine Bewertungen

- 31 SDMS 12Dokument31 Seiten31 SDMS 12Jalizco RuedaNoch keine Bewertungen

- Downloaded From Manuals Search Engine: NOKIA 6820Dokument121 SeitenDownloaded From Manuals Search Engine: NOKIA 6820okamiotokoNoch keine Bewertungen

- 35312aa Command Station PC Spec SheetDokument2 Seiten35312aa Command Station PC Spec SheetProduccion TAMNoch keine Bewertungen

- Advantages: Safety Isolating TransformerDokument2 SeitenAdvantages: Safety Isolating TransformerAnonymous EDt70JASWNoch keine Bewertungen

- Sean DeCraneDokument59 SeitenSean DeCraneMujeeb Ur Rehman KhalilNoch keine Bewertungen

- The Motherboard NotesDokument5 SeitenThe Motherboard NotesPritima RamalinggamNoch keine Bewertungen

- DynaLift 3 6 User Guide A4Dokument53 SeitenDynaLift 3 6 User Guide A4Quy HoangNoch keine Bewertungen

- Listening Test 25% Intento 1Dokument11 SeitenListening Test 25% Intento 1Adriana LoaizaNoch keine Bewertungen

- Yong Yi Lim Updated ResumeDokument1 SeiteYong Yi Lim Updated Resumeapi-481960507Noch keine Bewertungen

- A3-PageWide F2F Deck 2 28 17 final-ENDokument129 SeitenA3-PageWide F2F Deck 2 28 17 final-ENkadirNoch keine Bewertungen

- Pap2t Alarm Installation&ProvisioningguideDokument12 SeitenPap2t Alarm Installation&ProvisioningguideDavid WormstoneNoch keine Bewertungen

- Unit 3 Inside The SystemDokument2 SeitenUnit 3 Inside The SystemMartín CrespoNoch keine Bewertungen