Beruflich Dokumente

Kultur Dokumente

Sistemas Embebidos: Comunicacion Serial Sincrona SPI (Serial Peripherical Interface)

Hochgeladen von

RubensaiD0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

1K Ansichten20 SeitenCopyright

© Attribution Non-Commercial (BY-NC)

Verfügbare Formate

PPTX, PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Attribution Non-Commercial (BY-NC)

Verfügbare Formate

Als PPTX, PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

1K Ansichten20 SeitenSistemas Embebidos: Comunicacion Serial Sincrona SPI (Serial Peripherical Interface)

Hochgeladen von

RubensaiDCopyright:

Attribution Non-Commercial (BY-NC)

Verfügbare Formate

Als PPTX, PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 20

SISTEMAS EMBEBIDOS

COMUNICACIÓN SERIAL SINCRONA

SPI

(Serial Peripherical Interface)

PENSADO PARA COMUNICACIÓN CON

OTROS MICROCONTROLADORES O

PERIFÉRICOS COMO:

EEPROM serie (almacenamiento de

datos no volátiles)

Registros de Desplazamiento

(expansión de entradas y/o salidas)

Drivers de Displays (reducción de

conexiones)

Conversores A/D (digitalización

externa de señales)

Etc.

INTERFACE SPI EN EL MÓDULO SSP

Permite la transmisión y recepción

síncrona simultánea de datos de 8

bits.

Para la comunicación debe existir un

dispositivo Maestro (genera la señal

de reloj) y uno ó varios esclavos

(reciben la señal de reloj).

PINES DEL MICROCONTROLADOR

PIC ASOCIADOS A COMUNICACIÓN

SPI

Salida Serie de Datos (SDO) Serial Data Output ->

RC5

Entrada Serie de Datos (SDI) Serial Data Input ->

RC4

Reloj de comunicación Serie (SCK) Serial Clock->

RC3

De manera adicional, hay un 4º pin que se

puede utilizar cuando el microcontrolador se

configura como dispositivo Esclavo:

Selección de Esclavo (SS) Slave Select -> RA5

La inicialización del Interface SPI se realiza

mediante la configuración de los bits

DIAGRAMA DE BLOQUES DEL MÓDULO SSP EN MODO

SPI

SSPSR Y SSPBUF

FLAGS EN MODO SPI

SSPIF = PIR1<3> (Completada transmisión)

Lectura/escritura

Indica que se ha completado un envío/recepción en SSPSR

Se debe poner a 0 por software, puede generar interrupción

BF = SSPSTAT<0> (Buffer de recepción lleno) Sólo

lectura

Se pone a 1 cuando se ha completado la recepción de un dato

se pone a 0 por hardware cuando se lee el registro SSPBUF

Se empleará normalmente únicamente en modo de recepción

WCOL = SSPCON<7> (Colisión de Escritura)

Lectura/escritura

Indica que se ha intentado escribir en SSPBUF mientras se está

transmitiendo un dato previo. Si se da tal situación, se debe

poner

a 0 por software

SSPOV = SSPCON<6> (Desbordamiento en Recepción)

ESPECIFICACIÓN DEL MODO SPI EN LA

INICIALIZACIÓN

Modo de funcionamiento:

Maestro (SCK salida) o Esclavo (SCK entrada)

Polaridad del Reloj:

Estado Inactivo del Reloj (SCK) a “1” ó a “0”

Flancos activos del Reloj:

Salida de bits en flancos de subida o bajada en SCK

Muestreo bits de datos:

Muestreo de entrada en el “centro” o al “final” del bit

Frecuencia de Reloj:

SÓLO SI ES MAESTRO, frecuencia en salida SCK

Modo de Selección:

SÓLO SI ES ESCLAVO

- Control externo de SDI y SDO con entrada SS

- Sin control externo con pin SS

EJEMPLO DE CONEXION

ENVIO DE DATOS

HABILITACIÓN DE LOS PINES DE

ENTRADA/SALIDA de SSP

Para habilitar el módulo SSP, es necesario que el bit SSPEN

se encuentre a 1. Si

se desea “resetear” el módulo SSP, se debe poner a 0 este

bit y luego volverlo a 1

Para que la funcionalidad de los pines SDI, SDO, SCK y /SS

sea la determinada por los bits de configuración, es

necesario además que los bits de dirección de datos

(en TRISA y en TRISC) tengan la dirección adecuada:

SDI (RC4) debe tener TRISC<4> = 1 para ser entrada de

datos

SDO (RC5) debe tener TRISC<5> = 0 para que sea salida

de datos

SCK (RC3)

debe tener TRISC<3> = 0 si el microcontrolador es

MAESTRO

y TRSC<3> = 1 si se define como ESCLAVO

/SS (RA5) debe ser TRISA<5> = 1 si es ESCLAVO y tiene

control externo

Das könnte Ihnen auch gefallen

- Pic16f877 MSSPDokument24 SeitenPic16f877 MSSPtopotopoNoch keine Bewertungen

- 04 SpiDokument30 Seiten04 SpiBRAYAN GABRIEL GIRON GARCIANoch keine Bewertungen

- Comunicación Serie Síncrona I2CDokument18 SeitenComunicación Serie Síncrona I2CEduardo LeonNoch keine Bewertungen

- PRÁCTICADokument10 SeitenPRÁCTICACesar RemNoch keine Bewertungen

- Ccs Protocolo SpiDokument29 SeitenCcs Protocolo SpiMario Andres Caceres Nocera0% (1)

- Capítulo 19. Módulo MSSPDokument13 SeitenCapítulo 19. Módulo MSSPAlfredo Flores VargasNoch keine Bewertungen

- Modulo MSSPDokument65 SeitenModulo MSSPEricson Cruz RiosNoch keine Bewertungen

- Comunicación SPI PIC 16F877A PDFDokument4 SeitenComunicación SPI PIC 16F877A PDFRichiAvilaIbañez100% (3)

- Comunicación SPI PIC 16F877A PDFDokument4 SeitenComunicación SPI PIC 16F877A PDFAlejandro Martin TorresNoch keine Bewertungen

- MSSP: Módulo Puerto Serial Sincrónico SPI y I2CDokument4 SeitenMSSP: Módulo Puerto Serial Sincrónico SPI y I2CLenin AlexanderNoch keine Bewertungen

- Laboratorio 5 Atmega Comunicación Serial SpiDokument9 SeitenLaboratorio 5 Atmega Comunicación Serial SpiArturo72Noch keine Bewertungen

- Módulo Puerto Serie Síncrono MaestroDokument7 SeitenMódulo Puerto Serie Síncrono MaestroAdhiel PérezNoch keine Bewertungen

- Configuración de Registros para La Comunicación I2CDokument6 SeitenConfiguración de Registros para La Comunicación I2CAlex ÑacataNoch keine Bewertungen

- S11 Mnmt1401-SpiDokument17 SeitenS11 Mnmt1401-SpiLuis Gutiérrez MagánNoch keine Bewertungen

- Módulos SPI e I2CDokument23 SeitenMódulos SPI e I2CClaudia LunaNoch keine Bewertungen

- Modulo I2C en Un Microcontrolador PIC16F877Dokument21 SeitenModulo I2C en Un Microcontrolador PIC16F877Juan AguileraNoch keine Bewertungen

- 05 I2cDokument34 Seiten05 I2cBRAYAN GABRIEL GIRON GARCIANoch keine Bewertungen

- MÓDULO SCI EN MODO SÍNCRONODokument24 SeitenMÓDULO SCI EN MODO SÍNCRONOpoisonbetNoch keine Bewertungen

- 09 UsartDokument46 Seiten09 UsartKevin René Alarcón CalderónNoch keine Bewertungen

- Comunicacion Serial UsartDokument2 SeitenComunicacion Serial UsartAlvio Valencia GonzaliaNoch keine Bewertungen

- Puertos de I/O Pic16f877Dokument30 SeitenPuertos de I/O Pic16f877anon_376202896Noch keine Bewertungen

- Protocolo PSIDokument10 SeitenProtocolo PSIJuanTorraBarraganNoch keine Bewertungen

- Sistema de Comunicación Entre Arduino y Matlab para Medir Temperatura Utilizando Comunicación SPIDokument4 SeitenSistema de Comunicación Entre Arduino y Matlab para Medir Temperatura Utilizando Comunicación SPIAndderson' Zurdo FuentesNoch keine Bewertungen

- Comunicaciones SPI PIC18Dokument19 SeitenComunicaciones SPI PIC18Sea Lo Quesea Pero ChevereNoch keine Bewertungen

- S04s1 - Arq - PDS - Manejo de Puertos in - Out - Matlab X-XC16Dokument41 SeitenS04s1 - Arq - PDS - Manejo de Puertos in - Out - Matlab X-XC16renatto2089Noch keine Bewertungen

- Práctica Comunicación I2CDokument7 SeitenPráctica Comunicación I2Cjhan carlos sarmientoNoch keine Bewertungen

- S02.s4 - Arquitectura Del PIC 18F4550 Parte 3Dokument10 SeitenS02.s4 - Arquitectura Del PIC 18F4550 Parte 3mavis lopezNoch keine Bewertungen

- PICDokument53 SeitenPICRosemberg Torres DominguezNoch keine Bewertungen

- Sistemas Embebidos I2CDokument13 SeitenSistemas Embebidos I2CRoly Angel Inga ValentinNoch keine Bewertungen

- 8 - Modulo MSSP y Otros MicrocontroladoresDokument52 Seiten8 - Modulo MSSP y Otros MicrocontroladoresAndres Castro VacaNoch keine Bewertungen

- P5 DlpsDokument26 SeitenP5 DlpsAlex CortezNoch keine Bewertungen

- Modulo UsartDokument37 SeitenModulo UsartEduardo GarciaNoch keine Bewertungen

- Comunicación I2C PDFDokument22 SeitenComunicación I2C PDFManuel Eduardo Estrella PolancoNoch keine Bewertungen

- Para Que Nuestro Pic Funcione FísicamenteDokument7 SeitenPara Que Nuestro Pic Funcione FísicamenteAna Suggey100% (1)

- Introducción al funcionamiento y arquitectura interna del microcontrolador ATmega328PDokument11 SeitenIntroducción al funcionamiento y arquitectura interna del microcontrolador ATmega328PJeremy Ruben Quiroz RamosNoch keine Bewertungen

- El Puerto Serial RS232 2022ADokument16 SeitenEl Puerto Serial RS232 2022AMonse MorenoNoch keine Bewertungen

- Módulo 5 Comunicacion Serial AsincronaDokument11 SeitenMódulo 5 Comunicacion Serial AsincronaMishell Sanchez GuevaraNoch keine Bewertungen

- Micro Lab1Dokument9 SeitenMicro Lab1Alex MercerNoch keine Bewertungen

- Clase SPI Master SlaveDokument13 SeitenClase SPI Master SlavewsanzfNoch keine Bewertungen

- Config GPIO LEDDokument15 SeitenConfig GPIO LEDQuino B. JeffryNoch keine Bewertungen

- Descripción PIC 16F887Dokument47 SeitenDescripción PIC 16F887mongongoNoch keine Bewertungen

- Protocolo SpiDokument23 SeitenProtocolo SpifredyNoch keine Bewertungen

- Configuración Del Módulo de Comunicación SerieDokument19 SeitenConfiguración Del Módulo de Comunicación SerieRonny TituanaNoch keine Bewertungen

- Spi PDFDokument24 SeitenSpi PDFJairo Josué SierraNoch keine Bewertungen

- Mcp2515 AvrDokument17 SeitenMcp2515 AvrTwsky_04100% (1)

- Sistema de Comunicación Entre Arduino y Matlab para Medir Temperatura Utilizando Comunicación SPIDokument4 SeitenSistema de Comunicación Entre Arduino y Matlab para Medir Temperatura Utilizando Comunicación SPIAndderson' Zurdo Fuentes100% (1)

- Conectar Dos Arduinos SPIDokument6 SeitenConectar Dos Arduinos SPIErnesto Lerner ViscarraNoch keine Bewertungen

- Comunicación PC-PIC DB9Dokument31 SeitenComunicación PC-PIC DB9Daniel Angelo Alfaro Rodriguez100% (2)

- PIC18 (Español)Dokument78 SeitenPIC18 (Español)pedsan69Noch keine Bewertungen

- Configuración Timer1 y ADC ATmega8535Dokument9 SeitenConfiguración Timer1 y ADC ATmega8535irving_asNoch keine Bewertungen

- Teoria CuantikDokument5 SeitenTeoria CuantikDiego SantillánNoch keine Bewertungen

- PIC16F877 Con MikroCDokument160 SeitenPIC16F877 Con MikroCLuis Alejandro De Jesús SuárezNoch keine Bewertungen

- Curso de Lenguaje C para Microcontroladores Pic-Dia 1Dokument160 SeitenCurso de Lenguaje C para Microcontroladores Pic-Dia 1Jorge DominguezNoch keine Bewertungen

- Use RS232Dokument6 SeitenUse RS232Gräce Mäggüiie PicöNoch keine Bewertungen

- BascomDokument51 SeitenBascomLizette RojasNoch keine Bewertungen

- Comunicación PIC-PC Vía RS232Dokument12 SeitenComunicación PIC-PC Vía RS232Emanuel Ortiz MarinNoch keine Bewertungen

- ArduinoplatformiovscodeDokument28 SeitenArduinoplatformiovscodeLucas FiordelisiNoch keine Bewertungen

- Comunicacion Serie EsteeeDokument31 SeitenComunicacion Serie EsteeeMonica MarconiNoch keine Bewertungen

- Introducción Al Psoc5Lp: Teoría y aplicaciones prácticaVon EverandIntroducción Al Psoc5Lp: Teoría y aplicaciones prácticaNoch keine Bewertungen

- Simulación de circuitos electrónicos con OrCAD® PSpice®Von EverandSimulación de circuitos electrónicos con OrCAD® PSpice®Noch keine Bewertungen

- Guía Salarial 2021 LATAMDokument103 SeitenGuía Salarial 2021 LATAMDavid Orjeda SincheNoch keine Bewertungen

- El Fundamento Matematico de La Escala Musical y Sus Raices PitagoriasDokument14 SeitenEl Fundamento Matematico de La Escala Musical y Sus Raices PitagoriasRubensaiDNoch keine Bewertungen

- Rendimiento Asociado A Los Depósitos CTSDokument5 SeitenRendimiento Asociado A Los Depósitos CTSRubensaiDNoch keine Bewertungen

- WEB AM - Estilos de Vida 2Dokument18 SeitenWEB AM - Estilos de Vida 2unijaviNoch keine Bewertungen

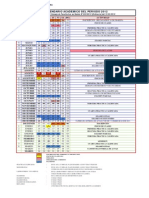

- Rol de Examenes Parcial y Final 2012-2 UNI FIMDokument5 SeitenRol de Examenes Parcial y Final 2012-2 UNI FIMRubensaiDNoch keine Bewertungen

- Plan de Estudios Ingeniería Mecánica Eléctrica UNI 2009Dokument3 SeitenPlan de Estudios Ingeniería Mecánica Eléctrica UNI 2009ermapNoch keine Bewertungen

- Rol de Practicas Calificada 2012-2 UNI FIMDokument4 SeitenRol de Practicas Calificada 2012-2 UNI FIMRubensaiDNoch keine Bewertungen

- Calendario Académico 2013 UNI FIMDokument1 SeiteCalendario Académico 2013 UNI FIMKevin MonroeNoch keine Bewertungen

- CTS - Triptico Serie 10Dokument2 SeitenCTS - Triptico Serie 10tsidkenu222Noch keine Bewertungen

- Plan Curricular - Ing. Mecatronica UNI FIMDokument3 SeitenPlan Curricular - Ing. Mecatronica UNI FIMRubensaiD100% (4)

- Rol de Practicas - UNI FIM 2012-1Dokument4 SeitenRol de Practicas - UNI FIM 2012-1RubensaiDNoch keine Bewertungen

- Cal End A RioDokument1 SeiteCal End A RioTanner EspinozaNoch keine Bewertungen

- Plan Curricular - Ing. Naval UNI FIMDokument3 SeitenPlan Curricular - Ing. Naval UNI FIMRubensaiDNoch keine Bewertungen

- Rol de Examenes Parcial y Final 2012-2 UNI FIMDokument5 SeitenRol de Examenes Parcial y Final 2012-2 UNI FIMRubensaiDNoch keine Bewertungen

- Plan Curricular - Ing. Mecanica UNI FIMDokument3 SeitenPlan Curricular - Ing. Mecanica UNI FIMRubensaiDNoch keine Bewertungen

- Pruebas para Determinar Los Parametros Del Circuito EquivalenteDokument17 SeitenPruebas para Determinar Los Parametros Del Circuito EquivalenteRubensaiDNoch keine Bewertungen

- Sistemas de Arranque para Motores AsíncronosDokument15 SeitenSistemas de Arranque para Motores Asíncronosquintan34100% (2)

- Catalogo de Productos 2012 - Aceros ArequipaDokument20 SeitenCatalogo de Productos 2012 - Aceros ArequipaRubensaiD100% (5)

- Manual: Caso 1. Presion A La Salida de Una Tuberia Version 1.1Dokument9 SeitenManual: Caso 1. Presion A La Salida de Una Tuberia Version 1.1RubensaiDNoch keine Bewertungen

- Fuerza Magnetomotriz en Bobinados de Corriente Alterna (AC)Dokument24 SeitenFuerza Magnetomotriz en Bobinados de Corriente Alterna (AC)RubensaiD100% (2)

- Numeración de Terminales en Las Máquinas Asíncronas o de Inducción TrifásicasDokument36 SeitenNumeración de Terminales en Las Máquinas Asíncronas o de Inducción TrifásicasRubensaiD100% (2)

- Propiedades Termicas de La MateriaDokument17 SeitenPropiedades Termicas de La MateriaRubensaiDNoch keine Bewertungen

- Bobinado Estatórico de La Máquina de Inducción o Asíncrona TrifásicaDokument46 SeitenBobinado Estatórico de La Máquina de Inducción o Asíncrona TrifásicaRubensaiD100% (3)

- Circuito Equivalente, Perdidas, Flujo de Potencia y Eficiencia de Las Máquinas Asíncronas o de Inducción TrifásicasDokument46 SeitenCircuito Equivalente, Perdidas, Flujo de Potencia y Eficiencia de Las Máquinas Asíncronas o de Inducción TrifásicasRubensaiD100% (1)

- Introducción A Las Máquinas Eléctricas RotativasDokument63 SeitenIntroducción A Las Máquinas Eléctricas RotativasRubensaiD67% (3)

- Estructura de Una Maquinas Asíncrona Trifasica o de InducciónDokument37 SeitenEstructura de Una Maquinas Asíncrona Trifasica o de InducciónRubensaiD100% (1)

- Principio de Funcionamiento de Las Máquinas Asíncronas o de Inducción TrifásicasDokument40 SeitenPrincipio de Funcionamiento de Las Máquinas Asíncronas o de Inducción TrifásicasRubensaiD80% (5)

- Tipos de Motores Asíncronos Trifasicos o de InducciónDokument36 SeitenTipos de Motores Asíncronos Trifasicos o de InducciónRubensaiD95% (37)

- Solucionario Fisica y Quimica - Admision UNI 2011-2 - TrilceDokument23 SeitenSolucionario Fisica y Quimica - Admision UNI 2011-2 - TrilceRubensaiD0% (2)

- Rol de Examenes Parcial y Final 2012-2 UNI FIMDokument5 SeitenRol de Examenes Parcial y Final 2012-2 UNI FIMRubensaiDNoch keine Bewertungen

- (Estadística)Dokument5 Seiten(Estadística)Chad PenningtonNoch keine Bewertungen

- Taller 1: "Estrategias para Una Comunicación Efectiva"Dokument2 SeitenTaller 1: "Estrategias para Una Comunicación Efectiva"andresNoch keine Bewertungen

- 15489-1 PresentacionDokument30 Seiten15489-1 PresentacionJorge Armando100% (1)

- Resumen A 5Dokument27 SeitenResumen A 5Sophie FriasNoch keine Bewertungen

- Portafolio (Entrega I)Dokument17 SeitenPortafolio (Entrega I)ernesto sanchezNoch keine Bewertungen

- Ejercicios POO en JavaDokument5 SeitenEjercicios POO en JavaMelodyCazachkoffNoch keine Bewertungen

- Manual Movemaster EspañolDokument33 SeitenManual Movemaster EspañolRuben Amaro MichelNoch keine Bewertungen

- 1413-Article Text-1636-1-10-20130523Dokument36 Seiten1413-Article Text-1636-1-10-20130523Bryan Del RioNoch keine Bewertungen

- PFC AuditpracticainformixDokument286 SeitenPFC AuditpracticainformixFer CebNoch keine Bewertungen

- Recursos de Una Empresa PresentacionDokument2 SeitenRecursos de Una Empresa PresentacionSergioRubenSanchezNoch keine Bewertungen

- BanescOnline GuiaDokument2 SeitenBanescOnline GuiaCarlos Coleito ParraNoch keine Bewertungen

- Taller 2 Punto 4cDokument6 SeitenTaller 2 Punto 4cJuan Sebastian ArenasNoch keine Bewertungen

- Introducción a la programación en PHPDokument10 SeitenIntroducción a la programación en PHPKarla GallardoNoch keine Bewertungen

- Propuesta Proyecto de SeguridadDokument168 SeitenPropuesta Proyecto de SeguridadRoss MarínNoch keine Bewertungen

- Prueba Matematica 4° BásicoDokument4 SeitenPrueba Matematica 4° BásicoJimena VelásquezNoch keine Bewertungen

- Clasificación de Redes SocialesDokument1 SeiteClasificación de Redes SocialesDelia ContrerasNoch keine Bewertungen

- Unidad IV Visualización de InformaciónDokument28 SeitenUnidad IV Visualización de InformaciónHector FloresNoch keine Bewertungen

- Creando una ventana en SketchUp con comandos básicosDokument12 SeitenCreando una ventana en SketchUp con comandos básicosRicardo AguilarNoch keine Bewertungen

- Diseñar consulta filtrar clientes crédito vencido 90 díasDokument5 SeitenDiseñar consulta filtrar clientes crédito vencido 90 díascristianNoch keine Bewertungen

- Samba LdapDokument15 SeitenSamba LdapSlim LozaNoch keine Bewertungen

- Indicadores FinancierosDokument5 SeitenIndicadores FinancierosShirlys Suarez GNoch keine Bewertungen

- Sistemas Digitales 1: Lógica Combinatoria ModularDokument59 SeitenSistemas Digitales 1: Lógica Combinatoria ModularJorge Gianotti HidalgoNoch keine Bewertungen

- Juicio en Línea y Juicio Sumario en Materia FiscalDokument2 SeitenJuicio en Línea y Juicio Sumario en Materia FiscalMarco Ruben Zarate MadridNoch keine Bewertungen

- Directorio de Comunidades Campesinas... WEB - Compressed PDFDokument422 SeitenDirectorio de Comunidades Campesinas... WEB - Compressed PDFAnonymous orzQ9zAw83% (6)

- ISO 9001 CalidadDokument3 SeitenISO 9001 Calidadleydy100% (1)

- CAPITULO 4 Modelo Operacional N1 Telefonía 3 5 PDFDokument111 SeitenCAPITULO 4 Modelo Operacional N1 Telefonía 3 5 PDFkilikumetalNoch keine Bewertungen

- GCO 2014 BBta 01 Licenciamiento OnbaseDokument6 SeitenGCO 2014 BBta 01 Licenciamiento OnbaseAfrovides LedupNoch keine Bewertungen

- Procedimiento de Rendición de CuentasDokument3 SeitenProcedimiento de Rendición de Cuentaslibardo davilaNoch keine Bewertungen

- Tarea2 deDokument8 SeitenTarea2 deVALERIA NAYELI DUEÑAS VILLARREALNoch keine Bewertungen

- Análisis y Diseño Sísmico de Un Edificio Residencial en Sistema Aporticado Basados en La NSR-10 1511305229 PDFDokument80 SeitenAnálisis y Diseño Sísmico de Un Edificio Residencial en Sistema Aporticado Basados en La NSR-10 1511305229 PDFwalter camilo tovar coquiesNoch keine Bewertungen