Beruflich Dokumente

Kultur Dokumente

Chapter 2-Field-Effect Transistor (FET)

Hochgeladen von

Lucas0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

91 Ansichten37 SeitenFET descripcion

Originaltitel

Chapter 2-Field-effect Transistor (FET)

Copyright

© © All Rights Reserved

Verfügbare Formate

PPT, PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenFET descripcion

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PPT, PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

91 Ansichten37 SeitenChapter 2-Field-Effect Transistor (FET)

Hochgeladen von

LucasFET descripcion

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PPT, PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 37

Field-effect

transistors (FETs)

EBB424E

Dr. Sabar D. Hutagalung

School of Materials & Mineral Resources Engineering,

Universiti Sains Malaysia

The Field Effect Transistor (FET)

In 1945, Shockley had an idea for making a solid state

device out of semiconductors.

He reasoned that a strong electrical field could cause the

flow of electricity within a nearby semiconductor.

He tried to build one, but it didn't work.

Three years later, Brattain & Bardeen built the first working

transistor, the germanium point-contact transistor, which

was designed as the junction (sandwich) transistor.

In 1960 Bell scientist John Atalla developed a new design

based on Shockley's original field-effect theories.

By the late 1960s, manufacturers converted from junction

type integrated circuits to field effect devices.

The Field Effect Transistor (FET)

Field effect devices are those in which current is

controlled by the action of an electron field, rather

than carrier injection.

Field-effect transistors are so named because a

weak electrical signal coming in through one

electrode creates an electrical field through the rest

of the transistor.

The FET was known as a unipolar transistor.

The term refers to the fact that current is transported

by carriers of one polarity (majority), whereas in the

conventional bipolar transistor carriers of both

polarities (majority and minority) are involved.

The Field Effect Transistor (FET)

The family of FET devices may be divided into :

Junction FET

Depletion Mode MOSFET

Enhancement Mode MOSFET

Junction FETs (JFETs)

JFETs consists of a piece of high-resistivity

semiconductor material (usually Si) which

constitutes a channel for the majority carrier

flow.

Conducting semiconductor channel between two

ohmic contacts source & drain

Junction FETs (JFETs)

The magnitude of this current is controlled by a voltage

applied to a gate, which is a reverse-biased.

The fundamental difference between JFET and BJT

devices: when the JFET junction is reverse-biased the

gate current is practically zero, whereas the base current

of the BJT is always some value greater than zero.

Junction FETs

JFET is a high-input resistance device, while the BJT is

comparatively low.

If the channel is doped with a donor impurity, n-type

material is formed and the channel current will consist of

electrons.

If the channel is doped with an acceptor impurity, p-type

material will be formed and the channel current will consist

of holes.

N-channel devices have greater conductivity than p-channel

types, since electrons have higher mobility than do holes;

thus n-channel JFETs are approximately twice as efficient

conductors compared to their p-channel counterparts.

Basic structure of JFETs

In addition to the channel, a

JFET contains two ohmic

contacts: the source and

the drain.

The JFET will conduct

current equally well in either

direction and the source

and drain leads are usually

interchangeable.

G a te G

p + G

B a s ic s tru c tu re C irc u it s y m b o l

fo r n -c h a n n e l F E T

S D

S o u rc e D ra in

S n n -ch a n n e l D S G D

p+ M e ta l e le c tro d e

p+

In s u la tio n

D e p le tio n D e p le tio n n (S iO 2 )

re g io n re g io n s

C ro s s s e c tio n p+ G

n -c h a n n e l p

n n

S n -c h a n n e l D

(b )

C hannel

th ic k n e s s p+

(a )

N-channel JFET

This transistor is made by

forming a channel of N-type

material in a P-type

substrate.

Three wires are then

connected to the device.

One at each end of the

channel.

One connected to the

substrate.

In a sense, the device is a

bit like a PN-junction diode,

except that there are two

wires connected to the N-

type side.

How JFET Function

The gate is connected to the

source.

Since the pn junction is reverse-

biased, little current will flow in

the gate connection.

The potential gradient

established will form a depletion

layer, where almost all the

electrons present in the n-type

channel will be swept away.

The most depleted portion is in

the high field between the G and

the D, and the least-depleted

area is between the G and the S.

How JFET Function

Because the flow of current

along the channel from the

(+ve) drain to the (-ve) source

is really a flow of free electrons

from S to D in the n-type Si, the

magnitude of this current will

fall as more Si becomes

depleted of free electrons.

There is a limit to the drain

current (ID) which increased VDS

can drive through the channel.

This limiting current is known

as IDSS (Drain-to-Source current

with the gate shorted to the

source).

The output characteristics of an n-channel JFET

with the gate short-circuited to the source.

The initial rise in ID is related to the buildup of the

depletion layer as VDS increases.

The curve approaches the level of the limiting

current IDSS when ID begins to be pinched off.

The physical meaning of this term leads to one

definition of pinch-off voltage, VP , which is the value

of VDS at which the maximum IDSS flows.

With a steady gate-source voltage of

1 V there is always 1 V across the

wall of the channel at the source

end.

A drain-source voltage of 1 V means

that there will be 2 V across the wall

at the drain end. (The drain is up 1V

from the source potential and the

gate is 1V down, hence the total

difference is 2V.)

The higher voltage difference at the

drain end means that the electron

channel is squeezed down a bit more

at this end.

When the drain-source voltage is

increased to 10V the voltage

across the channel walls at the

drain end increases to 11V, but

remains just 1V at the source end.

The field across the walls near the

drain end is now a lot larger than at

the source end.

As a result the channel near the

drain is squeezed down quite a lot.

Increasing the source-drain voltage

to 20V squeezes down this end of

the channel still more.

As we increase this voltage we

increase the electric field which

drives electrons along the open

part of the channel.

However, also squeezes down the

channel near the drain end.

This reduction in the open channel

width makes it harder for electrons

to pass.

As a result the drain-source current

tends to remain constant when we

increase the drain-source voltage.

Increasing VDS increases the widths of depletion layers,

which penetrate more into channel and hence result in

more channel narrowing toward the drain.

The resistance of the n-channel, RAB therefore increases

with VDS.

The drain current: IDS = VDS/RAB

ID versus VDS exhibits a sublinear behavior, see figure for

VDS < 5V.

The pinch-off voltage, VP is the magnitude of reverse bias

needed across the p+n junction to make them just touch at

the drain end.

Since actual bias voltage across p+n junction at drain end

is VGD, the pinch-off occur whenever: VGD = -VP.

Beyond VDS = VP, there is a

short pinch-off channel of

length, po.

As VDS increases, most of

additional voltage simply

drops across po as this

region is depleted of carriers

and hence highly resistive.

Voltage drop across channel

length, Lch remain as VP.

Beyond pinch-off then ID =

VP/RAP (VDS>VP).

What happen when

negative voltage, says

VGS = -2V, is applied to

gate with respect to

source (with VDS=0).

The p+n junction are

now reverse biased

from the start, the

channel is narrower,

and channel resistance

is now larger than in

the VGS = 0 case.

The drain current that flows when a small VDS

applied (Fig b) is now smaller than in VGS= 0 case.

Applied VDS= 3 V to pinch-off the channel (Fig c).

When VDS= 3V, VGD across p+n junction at drain end

is -5V, which is VP, so channel becomes pinch-off.

Beyond pinch-off, ID is nearly saturated just as in the

VGS=0 case.

Pinch-off occurs at VDS= VDS(sat), VDS(sat)= VP+VGS,

where VGS is ve voltage (reducing VP).

For VDS>VDS(sat), ID becomes nearly saturated at value

as IDS.

Beyond pinch-of, with ve VGS, IDS is

Where RAP(VGS) is the effective resistance of the

conducting n-channel from A to P, which depends on

channel thickness and hence VGS.

When VGS= -VP= -5V with VDS= 0, the two depletion

layers touch over the entire channel length and the

whole channel is closed.

The channel said to be off.

There is a convenient relationship between I DS and

VGS.

2

Beyond pinch-off VGS

I DS I DSS 1

VGS ( off )

Where IDSS is drain current when VGS= 0 and VGS(off) is

defined as VP, that is gate-source voltage that just

pinches off the channel.

The pinch off voltage VP here is a +ve quantity

because it was introduced through V DS(sat).

VGS(off) however is negative, -VP.

I-V characteristics

I-V characteristics

JFET: I-V characteristics

The transconductance curve

The process for plotting

transconductance curve for a given

JFET:

Plot a point that corresponds to value of

VGS(off).

Plot a poit that corresponds to value of

IDSS.

Select 3 or more values of VGS between

0 V and VGS(off). For value of VGS,

determine the corresponding value of ID

from

Plot the point from (3) and connect all

the plotted point with a smooth curve.

JFET Biasing Circuits

Example: Plot the dc bias line for the voltage-

drivers biasing circuit

Das könnte Ihnen auch gefallen

- EDC Unit-2Dokument22 SeitenEDC Unit-2giribabukandeNoch keine Bewertungen

- Multiple Choice Questions in Electronics and Electrical EngineeringVon EverandMultiple Choice Questions in Electronics and Electrical EngineeringBewertung: 4 von 5 Sternen4/5 (1)

- Chapter 5Dokument69 SeitenChapter 5Udai SinghNoch keine Bewertungen

- EEE 205 / ECE 202 Electronic Devices and Circuits I Spring 2012Dokument26 SeitenEEE 205 / ECE 202 Electronic Devices and Circuits I Spring 2012nehal hasnain refathNoch keine Bewertungen

- Lecture-12: P-N JunctionDokument24 SeitenLecture-12: P-N Junctionksooryakrishna1Noch keine Bewertungen

- Mosfet PDFDokument5 SeitenMosfet PDFChandru BadachiNoch keine Bewertungen

- Capacitance of Forward Biased DiodeDokument46 SeitenCapacitance of Forward Biased DiodeSushma S MurthyNoch keine Bewertungen

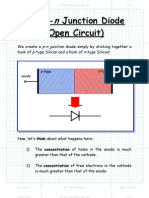

- P-N Junction Diode & Diode CharacteristicsDokument13 SeitenP-N Junction Diode & Diode Characteristicsapi-19822723Noch keine Bewertungen

- Field Effect TransistorsDokument140 SeitenField Effect Transistorswednesday08100% (2)

- P-N Junction (Diode) : Lecture-2Dokument45 SeitenP-N Junction (Diode) : Lecture-2Habib ShinwariNoch keine Bewertungen

- Semiconductor Devices-Module-4 PDFDokument36 SeitenSemiconductor Devices-Module-4 PDFNishant KumarNoch keine Bewertungen

- DC Characteristics of A MOS Transistor (MOSFET) : Created in COMSOL Multiphysics 5.3Dokument20 SeitenDC Characteristics of A MOS Transistor (MOSFET) : Created in COMSOL Multiphysics 5.3Anika TabassumNoch keine Bewertungen

- Unit-2: Junction Diode Characteristics: Review of SemiDokument55 SeitenUnit-2: Junction Diode Characteristics: Review of SemiSanthosh DheerajNoch keine Bewertungen

- Semiconductor Slides (Part II)Dokument22 SeitenSemiconductor Slides (Part II)Nishant MehlaNoch keine Bewertungen

- P-N Juntion Under Bias: Class 7Dokument14 SeitenP-N Juntion Under Bias: Class 7sudha mallikNoch keine Bewertungen

- Sambungan P-N Dan Dioda Sambungan P-NDokument27 SeitenSambungan P-N Dan Dioda Sambungan P-NUlfie Kusuma Wardhani100% (1)

- Filters 10Dokument32 SeitenFilters 10Leo CaiNoch keine Bewertungen

- (13b) Diode Sambungan P-NDokument27 Seiten(13b) Diode Sambungan P-NUlfie Kusuma WardhaniNoch keine Bewertungen

- CHAPTER III Latest Edited Oct11Dokument6 SeitenCHAPTER III Latest Edited Oct11J Christian B CallejoNoch keine Bewertungen

- Electrical Sciences EEE F111Dokument64 SeitenElectrical Sciences EEE F111Kriti TambareNoch keine Bewertungen

- Chapter 1 DiodesDokument109 SeitenChapter 1 Diodesshubhankar palNoch keine Bewertungen

- P-N Junction TransistorsDokument25 SeitenP-N Junction TransistorsFrancisNoch keine Bewertungen

- Open - MIT3 - 024S13 - 2012lec18Dokument16 SeitenOpen - MIT3 - 024S13 - 2012lec18j2yshjzzsxNoch keine Bewertungen

- Unit 1 - Electronic Devices & Circuits - WWW - Rgpvnotes.inDokument28 SeitenUnit 1 - Electronic Devices & Circuits - WWW - Rgpvnotes.inAfreen AliNoch keine Bewertungen

- Installing Media ProceduresDokument5 SeitenInstalling Media ProceduresDoozywoahNoch keine Bewertungen

- Avalanche Transit-Time Devices: Read DiodeDokument6 SeitenAvalanche Transit-Time Devices: Read DiodeRutuja BagavNoch keine Bewertungen

- Electrical Sciences EEE F111Dokument64 SeitenElectrical Sciences EEE F111KAUSTUBHNoch keine Bewertungen

- Electrical Sciences EEE F111Dokument64 SeitenElectrical Sciences EEE F111Kriti TambareNoch keine Bewertungen

- Edc PPT - 0Dokument198 SeitenEdc PPT - 0selaroth168Noch keine Bewertungen

- 1 PN Junction DIodeDokument34 Seiten1 PN Junction DIodesakthikothandapaniNoch keine Bewertungen

- Power Mosfets: Introduction To Fet'SDokument21 SeitenPower Mosfets: Introduction To Fet'SSharth KumarNoch keine Bewertungen

- Capacitance of Forward Biased DiodeDokument46 SeitenCapacitance of Forward Biased Diodez3r0r35Noch keine Bewertungen

- RF CMOS Background: July 2011Dokument17 SeitenRF CMOS Background: July 2011Srijeet TripathyNoch keine Bewertungen

- Note 1438399156 PDFDokument31 SeitenNote 1438399156 PDFpooja shutradharNoch keine Bewertungen

- 03 FET Field Effect TransistorsDokument69 Seiten03 FET Field Effect TransistorscacadsNoch keine Bewertungen

- Chapter 12 - P-N JunctionDokument69 SeitenChapter 12 - P-N JunctionShelly RismawatiNoch keine Bewertungen

- Semiconductor Devices A Brief Review: Dr. K. FobeletsDokument98 SeitenSemiconductor Devices A Brief Review: Dr. K. Fobeletsjit_72Noch keine Bewertungen

- The PN Junction DiodeDokument12 SeitenThe PN Junction DiodeSunny MayankNoch keine Bewertungen

- PN Junction and Semiconductor PDFDokument143 SeitenPN Junction and Semiconductor PDFMajak MarialNoch keine Bewertungen

- Elrectronic DevicesDokument198 SeitenElrectronic DevicesAndreea Telegdi MoodyNoch keine Bewertungen

- PN Junction at Equilibrium.: Diffusion DriftDokument4 SeitenPN Junction at Equilibrium.: Diffusion DriftanushafiNoch keine Bewertungen

- Tunnel Diode DefinitionDokument7 SeitenTunnel Diode Definitiongulzar ahmadNoch keine Bewertungen

- ENG325 Semiconductor Devices: Dr. TOH Eng-HuatDokument62 SeitenENG325 Semiconductor Devices: Dr. TOH Eng-HuatAndrea MorenoNoch keine Bewertungen

- Unit IV-Medical Imaging Modalities and AnalysisDokument19 SeitenUnit IV-Medical Imaging Modalities and AnalysisBarani DharanNoch keine Bewertungen

- CH 18 Fundamentals of ElectronicsDokument4 SeitenCH 18 Fundamentals of Electronicsasif_makNoch keine Bewertungen

- MSC Phy 62Dokument6 SeitenMSC Phy 62Krishna BoreddyNoch keine Bewertungen

- Exp5 2K20CO153Dokument7 SeitenExp5 2K20CO153divye guptaNoch keine Bewertungen

- P N Junction DiodeDokument19 SeitenP N Junction DiodeThomas AlemayehuNoch keine Bewertungen

- Donors and Acceptors in SemiconductorsDokument28 SeitenDonors and Acceptors in SemiconductorsMohammad Gulam AhamadNoch keine Bewertungen

- UofT CSC258 Computer Organization Lecture 1 Transistors Slides PDFDokument40 SeitenUofT CSC258 Computer Organization Lecture 1 Transistors Slides PDFGrey PointNoch keine Bewertungen

- SD 3rd Module MOSFETDokument8 SeitenSD 3rd Module MOSFETPranathi GNoch keine Bewertungen

- Task3 - Common Soure FET AmplifierDokument24 SeitenTask3 - Common Soure FET AmplifierAman Kumar TrivediNoch keine Bewertungen

- Experiment 1 P-N Junction Diode Characteristics: ObjectiveDokument5 SeitenExperiment 1 P-N Junction Diode Characteristics: ObjectiveBeat FluteNoch keine Bewertungen

- SemiconductorDokument69 SeitenSemiconductorSatheshNoch keine Bewertungen

- Basic Electronics (ES-112)Dokument45 SeitenBasic Electronics (ES-112)Bharat LalNoch keine Bewertungen

- Current and ConductorsDokument23 SeitenCurrent and ConductorsKybs nyhuNoch keine Bewertungen

- Sample Investigatory ProjectDokument22 SeitenSample Investigatory ProjectShubham PatelNoch keine Bewertungen

- 2014 0920 CMOS Fundamentals PDFDokument34 Seiten2014 0920 CMOS Fundamentals PDFĐại Ma ĐầuNoch keine Bewertungen

- PN DiodeDokument44 SeitenPN DiodeTAMIL VANANNoch keine Bewertungen

- Ds 23001Dokument3 SeitenDs 23001Mos CraciunNoch keine Bewertungen

- Sensorbox SRBC-CA3-YR90-MW-22A-1W-C2P20: Data SheetDokument2 SeitenSensorbox SRBC-CA3-YR90-MW-22A-1W-C2P20: Data SheetWelisson Anjos EmerichNoch keine Bewertungen

- RONGHE Microelectronics RH6015C C78180.zh-CN - enDokument11 SeitenRONGHE Microelectronics RH6015C C78180.zh-CN - enGustavo MoraesNoch keine Bewertungen

- Sélection Guide NXPDokument101 SeitenSélection Guide NXPAlain GoudeauNoch keine Bewertungen

- WireDokument583 SeitenWireLoc TruongNoch keine Bewertungen

- Linear Induction Motors: Y. LalithaDokument19 SeitenLinear Induction Motors: Y. LalithaNIkhil Raj BNoch keine Bewertungen

- CD43Dokument1 SeiteCD43netnereaNoch keine Bewertungen

- Ile All 2Dokument429 SeitenIle All 2Eyob HaylemariamNoch keine Bewertungen

- Tattoo Machine TroubleshootingDokument2 SeitenTattoo Machine TroubleshootingMirjana Lukic100% (1)

- VRF Schematic LayoutDokument1 SeiteVRF Schematic LayoutAbdullah.N FAAliNoch keine Bewertungen

- Price List 20 Oct 2015Dokument114 SeitenPrice List 20 Oct 2015Anonymous 7XE94xNoch keine Bewertungen

- Dioda ZenerDokument2 SeitenDioda ZenerGeorge TimpauNoch keine Bewertungen

- Ed01 (EN) PDFDokument40 SeitenEd01 (EN) PDFsebastian50% (2)

- Trafoindo Catalogue Oil Immersed Transformers PDFDokument2 SeitenTrafoindo Catalogue Oil Immersed Transformers PDFarie611Noch keine Bewertungen

- 3000W True Sine Wave DC-AC Inverter: SeriesDokument2 Seiten3000W True Sine Wave DC-AC Inverter: Serieshassoun01Noch keine Bewertungen

- Company Profile PT LSA Cable Indonesia - 211214 - 182836Dokument6 SeitenCompany Profile PT LSA Cable Indonesia - 211214 - 182836ikhsan firdausNoch keine Bewertungen

- Isuzu NPR NQR 2001 Electrical TroubeshootingDokument20 SeitenIsuzu NPR NQR 2001 Electrical Troubeshootinglawrence100% (44)

- Eq HHDokument1 SeiteEq HHSKYhabiaNoch keine Bewertungen

- Ap2114h-2 5TRG1Dokument28 SeitenAp2114h-2 5TRG1HauQuyen G530HNoch keine Bewertungen

- ONAN Troubleshooting For RV'sDokument17 SeitenONAN Troubleshooting For RV'sEdward Tillman100% (3)

- E560 - Subrack FSR02Dokument7 SeitenE560 - Subrack FSR02LeoKing16Noch keine Bewertungen

- Ee6604 Design of Electrical MachineDokument1 SeiteEe6604 Design of Electrical MachinevigneshcjNoch keine Bewertungen

- IECEx INE 10.0007X 000Dokument6 SeitenIECEx INE 10.0007X 000Marcos SiqueiraNoch keine Bewertungen

- Himel International Catalogue 2023Dokument454 SeitenHimel International Catalogue 2023Jason SonidoNoch keine Bewertungen

- MASTER HPI-T Plus 250W/645 E40 1SLDokument3 SeitenMASTER HPI-T Plus 250W/645 E40 1SLstrejtbreNoch keine Bewertungen

- D.C. Machines and Transformers LabDokument41 SeitenD.C. Machines and Transformers Labsrinivas gangishettiNoch keine Bewertungen

- Feeder Protection-1Dokument81 SeitenFeeder Protection-1COULIBALYNoch keine Bewertungen

- NEXGEN 20 Tech Guide ChlorkIng 02.03.2014Dokument100 SeitenNEXGEN 20 Tech Guide ChlorkIng 02.03.2014Andrés YepesNoch keine Bewertungen

- CPC 100 Testrano 600 Appnote Dynamic Oltc Scan 2019 EnuDokument21 SeitenCPC 100 Testrano 600 Appnote Dynamic Oltc Scan 2019 EnudanielsampermNoch keine Bewertungen

- Electronic Products & Components in PUNEDokument4 SeitenElectronic Products & Components in PUNESenthil Kumar MuraliNoch keine Bewertungen