Beruflich Dokumente

Kultur Dokumente

Chapter Six: The 80x86 Instruction Set

Hochgeladen von

Abdifitah0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

48 Ansichten44 Seitenchapter six

Originaltitel

Chapter Six 2

Copyright

© © All Rights Reserved

Verfügbare Formate

PPTX, PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenchapter six

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PPTX, PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

48 Ansichten44 SeitenChapter Six: The 80x86 Instruction Set

Hochgeladen von

Abdifitahchapter six

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PPTX, PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 44

Chapter Six

The 80x86 Instruction Set

Chapter Overview

• This chapter discusses the 80x86 real mode

instruction set.

• Like any programming language, there are

going to be several instructions you use all the

time, some you use occasionally, and some

you will rarely, if ever, use.

• If you learn only these instructions, you will

probably be able to write any assembly

language program you want.

• There are many additional instructions,

especially on the 80386 and later processors.

• These additional instructions make assembly

language programming easier, but you do not

need to know them to begin writing programs.

• 80x86 instructions can be (roughly) divided into

eight different classes:

• 1) Data movement instructions

• • mov, lea, les , push, pop, pushf, popf

• 2) Conversions

• • cbw, cwd, xlat

• 3) Arithmetic instructions

• • add, inc sub, dec, cmp, neg, mul, imul, div, idiv

• 4) Logical, shift, rotate, and bit instructions

• • and, or, xor, not, shl, shr, rcl, rcr

• 5) I/O instructions

• • in, out

• 6) String instructions

• • movs, stos, lods

• 7) Program flow control instructions

• • jmp, call, ret, conditional jumps

• 8) Miscellaneous instructions.

• • clc, stc, cmc

6.1 The Processor Status Register

(Flags)

• The flags register maintains the current

operating mode of the CPU and some

instruction state information.

• Figure 6.1 shows the layout of the flags

register.

• The carry, parity, zero, sign, and overflow flags

are special because you can test their

• status (zero or one) with the setcc and

conditional jump instructions

• The 80x86 uses these bits, the condition codes,

to make decisions during program execution.

• RFLAGS indicate the condition of the

microprocessor and control its operation.

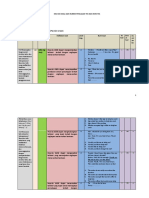

• Figure below shows the flag registers of all

versions of the microprocessor.

• Flags are upward-compatible from the 8086/8088

through Core2 .

• The rightmost five and the overflow flag are

changed by most arithmetic and logic operations.

– although data transfers do not affect them

Figure The EFLAG and FLAG register counts for the entire 8086 and Pentium microprocessor

family.

• Flags never change for any data transfer or

program control operation.

• Some of the flags are also used to control

features found in the microprocessor.

• Flag bits, with a brief description of function.

• C (carry) holds the carry after addition or borrow

after subtraction.

– also indicates error conditions

• P (parity) is the count of ones in a number

expressed as even or odd. Logic 0 for odd parity;

logic 1 for even parity.

– if a number contains three binary one bits, it has odd

parity

– if a number contains no one bits, it has even parity

List of Each Flag bit, with a brief

description of function.

• C (carry) holds the carry after addition or borrow

after subtraction.

– also indicates error conditions

• P (parity) is the count of ones in a number

expressed as even or odd. Logic 0 for odd parity;

logic 1 for even parity.

– if a number contains three binary one bits, it has odd

parity; If a number contains no one bits, it

has even parity

• A (auxiliary carry) holds the carry (half-carry)

after addition or the borrow after subtraction

between bit positions 3 and 4 of the result.

• Z (zero) shows that the result of an arithmetic or

logic operation is zero.

• S (sign) flag holds the arithmetic sign of the result

after an arithmetic or logic instruction executes.

• T (trap) The trap flag enables trapping through an

on-chip debugging feature.

• I (interrupt) controls operation of the INTR

(interrupt request) input pin.

• D (direction) selects increment or decrement

mode for the DI and/or SI registers.

• O (overflow) occurs when signed numbers are

added or subtracted.

– an overflow indicates the result has exceeded

the capacity of the machine

• IOPL used in protected mode operation

to select the privilege level for I/O devices.

• NT (nested task) flag indicates the current task

is nested within another task in protected mode

operation.

• RF (resume) used with debugging to control

resumption of execution after the next instruction.

• VM (virtual mode) flag bit selects virtual mode

operation in a protected mode system.

• AC, (alignment check) flag bit activates if a word

or doubleword is addressed on a non-word or non-

doubleword boundary.

• VIF is a copy of the interrupt flag bit available to

the Pentium 4–(virtual interrupt)

• VIP (virtual) provides information about a virtual

mode interrupt for (interrupt pending) Pentium.

– used in multitasking environments to provide virtual

interrupt flags

• ID (identification) flag indicates that the

Pentium microprocessors support the CPUID

instruction.

– CPUID instruction provides the system with

information about the Pentium microprocessor

6.2 Instruction Encodings

• The 80x86 uses a binary encoding for each

machine operation.

• While it is important to have a general

understanding of how the 80x86 encodes

instructions, it is not important that you

memorize the encodings for all the instructions

in the instruction set.

• Chapter Three and Chapter Four provided a

detailed look at instruction encodings for

various instructions (80x86 and x86); such a

discussion was important because you do need

to understand how the CPU encodes and

executes instructions.

6.3 Data Movement Instructions

• The data movement instructions copy values

from one location to another.

• These instructions include mov, xchg, lds, lea,

les, lfs, lgs, lss, push, pusha (push all), pushad,

pushf, pushfd, pop, popa, popad, popf, popfd,

lahf, and sahf.

6.3.1 The MOV Instruction

• The mov instruction takes several different forms:

• mov reg, reg1

• Mov mem, reg

• mov reg, mem

• mov mem, immediate data

• mov reg, immediate data

• mov ax/al, mem

• mov mem, ax/al

• Mov segreg, mem16

• Mov segreg, reg16

• mov mem16, segreg

• mov reg16, segreg

• For example, the following two instruction

sequence loads the es register with the value

40h:

»mov ax, 40h

»mov es, ax

6.3.2 The XCHG Instruction

• The xchg (exchange) instruction swaps two

values. The general form is

»xchg operand1, operand2

• There are four specific forms of this instruction

on the 80x86:

» xchg reg, mem

» xchg reg, reg

» xchg ax, reg16

» xchg eax, reg32 (3)

• (3) Available only on 80386 and later processors

6.3.4 The LEA Instruction

• The lea (Load Effective Address) instruction is

another instruction used to prepare pointer

values.

• The lea instruction takes the form:

• lea dest, source

• The specific forms on the 80x86 are

• lea reg16, mem

• lea reg32, mem

• It loads the specified 16 or 32 bit general purpose

register with the effective address of the specified

memory location.

• Consider the following lea instructions:

• lea ax, [bx]

• lea bx, [3+bx]

• lea ax, [3+bx]

• lea bx, [4+bp+si]

• lea ax, [-123+di]

6.3.5 The PUSH and POP Instructions

• The 80x86 push and pop instructions

manipulate data on the 80x86’s hardware

stack.

• There are 19 varieties of the push and pop

instructions, they are:

• push reg16

• pop reg16

• push reg32 (3)

• pop reg32 (3)

• push segreg

• pop segreg (except CS)

• push memory

• pop memory

• push immediate_data (2)

• pusha

• popa

• pushad

• popad

• pushf

• popf

• pushfd

• popfd

• enter imm, imm

• leave

• Enter and leave push/pop the bp register and

allocate storage for local variables on the

stack.

6.3.6 The LAHF and SAHF Instructions

• The lahf (load ah from flags) and sahf (store ah

into flags) instructions are archaic instructions

included in the 80x86’s instruction set to help

improve compatibility with Intel’s older 8080

P chip.

• These instructions do not require any

operands and you use them in the following

manner:

» sahf

» lahf

6.4 Conversions

• The 80x86 instruction set provides several

conversion instructions.

• They include movzx, movsx, cbw, cwd, cwde,

cdq, bswap, and xlat. Most of these

instructions sign or zero extend values, the

last two convert between storage formats and

translate values via a lookup table.

• These instructions take the general form:

• movzx dest, src ;Dest must be twice the size of src.

• movsx dest, src ;Dest must be twice the size of src.

• cbw

• cwd

• cwde

• cdq

• bswap reg32

• xlat

6.4.1 The MOVZX, MOVSX, CBW,

CWD, CWDE, and CDQ Instructions

• These instructions zero and sign extend

values.

• The cbw and cwd instructions are available on

all 80x86 processors.

• The movzx, movsx, cwde, and cdq instructions

are available only on 80386 and later

processors.

• The cbw (convert byte to word) instruction sign

extends the eight bit value in al to ax.

• That is, it copies bit seven of AL throughout bits

8-15 of ax.

• This instruction is especially important before

executing an eight bit division (as you’ll see in the

section “Arithmetic Instructions” on page 255).

• This instruction requires no operands and you

use it as follows:

cbw

• The cwd (convert word to double word)

instruction sign extends the 16 bit value in ax

to 32 bits and places the result in dx:ax.

• It copies bit 15 of ax throughout the bits in dx.

• Like the cbw instruction, this instruction is

very important for division operations.

• Cwd requires no operands and you use it as

follows

cwd

• The cwde instruction sign extends the 16 bit

value in ax to 32 bits and places the result in

eax by copying bit 15 of ax throughout bits

16..31 of eax.

• As with cbw and cwd the instruction has no

operands and you use it as follows:

cwde

• The cdq instruction sign extends the 32 bit

value in eax to 64 bits and places the result in

edx:eax by copying bit 31 of eax throughout

bits 0..31 of edx.

• As with cbw, cwd, and cwde the instruction

has no operands and you use it as follows:

cdq

• The movsx instruction is a generalized form of

the cbw, cwd, and cwde instructions.

• It will sign extend an eight bit value to a

sixteen or thirty-two bits, or sign extend a

sixteen bit value to a thirty-two bits

• This instruction uses a mod-reg-r/m byte to

specify the two

• operands. The allowable forms for this instruction

are

• movsx reg16, mem8

• movsx reg16, reg8

• movsx reg32, mem8

• movsx reg32, reg8

• movsx reg32, mem16

• movsx reg32, reg16

• Note that anything you can do with the cbw

and cwde instructions, you can do with a

• movsx instruction:

• movsx ax, al ;CBW

• movsx eax, ax ;CWDE

• movsx eax, al ;CBW followed by CWDE

• However, the cbw and cwde instructions are

shorter and sometimes faster.

6.4.2 The BSWAP Instruction

• The bswap instruction, available only on 80486

(yes, 486) and later processors, converts between

32 bit little endian and big endian values.

• This instruction accepts only a single

• 32 bit register operand. It swaps the first byte

with the fourth and the second byte with

• the third.

• The syntax for the instruction is

• bswap reg32

6.4.3 The XLAT Instruction

• The xlat instruction translates the value in the

al register based on a lookup table in

• memory. It does the following:

• temp := al+bx

• al := ds:[temp]

• that is, bx points at a table in the current data

segment. Xlat replaces the value in al with the

byte at the offset originally in al.

• The xlat instruction takes the form:

• xlat

• Typically it has no operand. You can specify

one but the assembler virtually ignores it.

6.5 Arithmetic Instructions

Das könnte Ihnen auch gefallen

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationVon EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNoch keine Bewertungen

- Assembly LanguageDokument26 SeitenAssembly LanguageAlistar AndreeaNoch keine Bewertungen

- Advanced Compiler Design and Implementation: Run-Time SupportDokument27 SeitenAdvanced Compiler Design and Implementation: Run-Time SupportvadriangmailNoch keine Bewertungen

- Unit IDokument131 SeitenUnit Iuradekaruna1972Noch keine Bewertungen

- 8086 16-bit Microprocessor HistoryDokument20 Seiten8086 16-bit Microprocessor HistorySanjaykumar GowreNoch keine Bewertungen

- Avr 2022Dokument17 SeitenAvr 2022Soumya Ranjan PandaNoch keine Bewertungen

- Emu8086 en Ingles11Dokument49 SeitenEmu8086 en Ingles11Sandy Solis De LopezNoch keine Bewertungen

- Lecture 2Dokument27 SeitenLecture 2Muhammad WasayNoch keine Bewertungen

- Pic16f FeaturesDokument40 SeitenPic16f Featuresveeramaniks408Noch keine Bewertungen

- CH 4. Data Transfers, Addressing, and ArithmeticDokument58 SeitenCH 4. Data Transfers, Addressing, and ArithmeticAlex MartinNoch keine Bewertungen

- Lecture#2 Fut Microprocessor PDFDokument81 SeitenLecture#2 Fut Microprocessor PDFAhmedGamalNoch keine Bewertungen

- 08 IsaDokument49 Seiten08 IsadarpanNoch keine Bewertungen

- MPS Lecture 3 - The Microprocessor and Its ArchitectureDokument26 SeitenMPS Lecture 3 - The Microprocessor and Its ArchitectureShehroze TalatNoch keine Bewertungen

- 8086 MicroprocessorDokument32 Seiten8086 MicroprocessorMohamedNoch keine Bewertungen

- The Acorn RISC Machine (ARM)Dokument12 SeitenThe Acorn RISC Machine (ARM)Vikas SinghNoch keine Bewertungen

- ISA - CISC VS RISC - Intro To MIPSDokument59 SeitenISA - CISC VS RISC - Intro To MIPSAffan GhazaliNoch keine Bewertungen

- M-4 CODokument61 SeitenM-4 COrohitrajww4Noch keine Bewertungen

- Delayed Branch Logic: Texas Instruments TMS320 Is A Blanket Name For A Series ofDokument13 SeitenDelayed Branch Logic: Texas Instruments TMS320 Is A Blanket Name For A Series ofnomadcindrellaNoch keine Bewertungen

- Cse2006 - Microprocessor & InterfacingDokument53 SeitenCse2006 - Microprocessor & InterfacingPREETI SAI THANDAVAN 20BCE1740Noch keine Bewertungen

- MPS Lecture 10 - Arithmetic OperationsDokument29 SeitenMPS Lecture 10 - Arithmetic OperationsShehroze TalatNoch keine Bewertungen

- MCS-51 Instruction Set SummaryDokument50 SeitenMCS-51 Instruction Set SummaryAli ShanNoch keine Bewertungen

- Chapter-5: Assembly Language Programming Using 8086 (16 Marks)Dokument55 SeitenChapter-5: Assembly Language Programming Using 8086 (16 Marks)PRABHAKAR MORENoch keine Bewertungen

- Tutorial EMU8086Dokument92 SeitenTutorial EMU8086franco saul francoNoch keine Bewertungen

- CoprocessorDokument23 SeitenCoprocessorsarthakNoch keine Bewertungen

- Data Movement InstructionsDokument22 SeitenData Movement InstructionsMarc Ryan SajaNoch keine Bewertungen

- MPS Lecture 4 - Addressing ModesDokument44 SeitenMPS Lecture 4 - Addressing ModesShehroze TalatNoch keine Bewertungen

- Microprocessor Addressing Modes GuideDokument63 SeitenMicroprocessor Addressing Modes GuideỐt Xì ÀNoch keine Bewertungen

- Chapter 4Dokument58 SeitenChapter 4farjadNoch keine Bewertungen

- ch4 HandoutsDokument72 Seitench4 HandoutsMarah IrshedatNoch keine Bewertungen

- COAL Lab 3 - Registers, I/O and StringsDokument13 SeitenCOAL Lab 3 - Registers, I/O and StringsAyaan ShahNoch keine Bewertungen

- Basic Features of MICROCOMPUTER: Julius BancudDokument17 SeitenBasic Features of MICROCOMPUTER: Julius BancudRed StreakNoch keine Bewertungen

- Introduction to 8086/8088 Microprocessor ArchitectureDokument39 SeitenIntroduction to 8086/8088 Microprocessor ArchitectureSahilYadavNoch keine Bewertungen

- Assembly Programming BasicsDokument46 SeitenAssembly Programming BasicsHarsh KaushalyaNoch keine Bewertungen

- System Software and Machine Architecture OverviewDokument78 SeitenSystem Software and Machine Architecture OverviewNithiBoazNoch keine Bewertungen

- MSP 430 (Mixed Signal Processor)Dokument64 SeitenMSP 430 (Mixed Signal Processor)Pradeepdarshan PradeepNoch keine Bewertungen

- 8086Dokument68 Seiten8086debasish beheraNoch keine Bewertungen

- Module-2: Microcontroller and Embedded SystemsDokument74 SeitenModule-2: Microcontroller and Embedded Systemsswethaashok28Noch keine Bewertungen

- 8085 Microprocessor - Functional Units: AccumulatorDokument20 Seiten8085 Microprocessor - Functional Units: AccumulatorCarlnagum 123456789Noch keine Bewertungen

- 4 22 01 ISA Part II AnnotatedDokument69 Seiten4 22 01 ISA Part II Annotatedwraith324Noch keine Bewertungen

- 8051 MicrocontrolllerDokument296 Seiten8051 MicrocontrolllerAniket BabutaNoch keine Bewertungen

- Instructions Assembler DirectivespptDokument22 SeitenInstructions Assembler DirectivespptAntra Gurain100% (1)

- Microprocessor Interfacing TechniquesDokument27 SeitenMicroprocessor Interfacing TechniquesAbdul Rehman KhanNoch keine Bewertungen

- 8087 Instruction Set and ExampleDokument27 Seiten8087 Instruction Set and ExampleAnonymous Ces8jpqNoch keine Bewertungen

- RISC Instruction Set:: I) Data Manipulation InstructionsDokument8 SeitenRISC Instruction Set:: I) Data Manipulation InstructionsSwarup BharNoch keine Bewertungen

- CS401 - Short Notes Chapter 17Dokument4 SeitenCS401 - Short Notes Chapter 17malikNoch keine Bewertungen

- Case Study 8086 MicroprocessorDokument4 SeitenCase Study 8086 MicroprocessorVitesh ShengaleNoch keine Bewertungen

- System Software FundamentalsDokument77 SeitenSystem Software FundamentalsJASPER WESSLYNoch keine Bewertungen

- Instruction Set Architecture (ISA)Dokument41 SeitenInstruction Set Architecture (ISA)StarqueenNoch keine Bewertungen

- Important Bits and Answers For CSCDokument31 SeitenImportant Bits and Answers For CSCbaapekNoch keine Bewertungen

- 04 8051 Instruction SetDokument76 Seiten04 8051 Instruction SetharinkhedetNoch keine Bewertungen

- Microprocessor Fundamentals and 8086 ArchitectureDokument8 SeitenMicroprocessor Fundamentals and 8086 ArchitectureMerin JesurajNoch keine Bewertungen

- SPKR DemoDokument3 SeitenSPKR DemoAyan KhanNoch keine Bewertungen

- Architecture of c5xDokument19 SeitenArchitecture of c5xB11 Aswathy SureshNoch keine Bewertungen

- Lecture #3 Addressing Modes PDFDokument77 SeitenLecture #3 Addressing Modes PDFAhmedGamalNoch keine Bewertungen

- CSE2006 LabDokument33 SeitenCSE2006 LabBharath BunnyNoch keine Bewertungen

- MI Chapter 3Dokument26 SeitenMI Chapter 3DANIEL ABERANoch keine Bewertungen

- Experiment 04 EEE 3210Dokument8 SeitenExperiment 04 EEE 3210191110.eeeNoch keine Bewertungen

- Internal Organization of A PC: MemoryDokument33 SeitenInternal Organization of A PC: MemoryPrasath SanthanamNoch keine Bewertungen

- Assembly-Language Additional ResourcesDokument18 SeitenAssembly-Language Additional ResourcesMC JERID C. BATUNGBAKALNoch keine Bewertungen

- Constant propagation and foldingDokument16 SeitenConstant propagation and foldingF e e l i n g s অ নু ভূ তিNoch keine Bewertungen

- Assignment 1Dokument1 SeiteAssignment 1AbdifitahNoch keine Bewertungen

- Liga AleDokument5 SeitenLiga AleAbdifitahNoch keine Bewertungen

- LegalDokument4 SeitenLegalAbdifitahNoch keine Bewertungen

- Design of An Intelligent Room Light Controller With Bidirectional Counters For Energy Efficiency ApplicationsDokument101 SeitenDesign of An Intelligent Room Light Controller With Bidirectional Counters For Energy Efficiency ApplicationsAbdifitahNoch keine Bewertungen

- Ijictrdv1i4005 PDFDokument6 SeitenIjictrdv1i4005 PDFAbdifitahNoch keine Bewertungen

- Automatic Room Light Controller PDFDokument43 SeitenAutomatic Room Light Controller PDFSamuel Bhukya67% (3)

- Kisi-Kisi Soal - KD 3.1 - KD 4.1 - Kls XiiDokument14 SeitenKisi-Kisi Soal - KD 3.1 - KD 4.1 - Kls Xiisinyo201060% (5)

- Language Interrupted Signs of Non Native Acquisition in Standard Language Grammars PDFDokument332 SeitenLanguage Interrupted Signs of Non Native Acquisition in Standard Language Grammars PDFjuramentatdo00Noch keine Bewertungen

- LicenceDokument3 SeitenLicenceAndika GlinNoch keine Bewertungen

- Create Allocate & Transact Move Orders Using APIDokument2 SeitenCreate Allocate & Transact Move Orders Using APIAnonymous NnVgCXDwNoch keine Bewertungen

- 24AA512/24LC512/24FC512: 512K I C Serial EEPROMDokument36 Seiten24AA512/24LC512/24FC512: 512K I C Serial EEPROMJoseNoch keine Bewertungen

- Activity in Module 17Dokument2 SeitenActivity in Module 17Minnie WagsinganNoch keine Bewertungen

- How To Write A Comic Book - Explorer Junior Library How To WriteDokument28 SeitenHow To Write A Comic Book - Explorer Junior Library How To WriteLongNguyen100% (4)

- Form 3 Ar2 Speaking Exam PaperDokument5 SeitenForm 3 Ar2 Speaking Exam PaperGrace WongNoch keine Bewertungen

- UntitledDokument9 SeitenUntitledLaith MahmoudNoch keine Bewertungen

- OpenText Documentum Content Server 7.3 Administration and Configuration GuideDokument580 SeitenOpenText Documentum Content Server 7.3 Administration and Configuration Guidedoaa faroukNoch keine Bewertungen

- Starter Architecture For Flutter & Firebase Apps Using RiverpodDokument28 SeitenStarter Architecture For Flutter & Firebase Apps Using RiverpodYochay RofeNoch keine Bewertungen

- Focus3 2E Grammar Quiz Unit8 2 GroupBDokument1 SeiteFocus3 2E Grammar Quiz Unit8 2 GroupBIvannaNoch keine Bewertungen

- Translationand CensorshipDokument30 SeitenTranslationand CensorshipmozaroliveiraNoch keine Bewertungen

- 8086 Masm ManualDokument44 Seiten8086 Masm ManualradhikaNoch keine Bewertungen

- Cambridge Primary ProgressionTests - Past Papers PDFDokument3 SeitenCambridge Primary ProgressionTests - Past Papers PDFPinky Dey8% (13)

- Run Odoo in HTTPS using Nginx & CertbotDokument4 SeitenRun Odoo in HTTPS using Nginx & CertbotCoko Mirindi MusazaNoch keine Bewertungen

- Daily Routine Reading - Third Person SingularDokument2 SeitenDaily Routine Reading - Third Person SingularHELEN MICHEL PÉREZ GONZÁLEZNoch keine Bewertungen

- Eustace Mullins: The Secret HolocaustDokument28 SeitenEustace Mullins: The Secret Holocaustkingofswords50% (2)

- Timeline of The Philippine Revolution FRDokument2 SeitenTimeline of The Philippine Revolution FRGheoxel Kate CaldeNoch keine Bewertungen

- Módulo+12+B1++Dokument17 SeitenMódulo+12+B1++Brayan Alexander Gil SandovalNoch keine Bewertungen

- Prayers (Dua), Mannat and NazarDokument41 SeitenPrayers (Dua), Mannat and NazarIbrahima SakhoNoch keine Bewertungen

- Sobelino, James Carl A. Activity 2Dokument8 SeitenSobelino, James Carl A. Activity 2JamesNoch keine Bewertungen

- 215 - Ar-4 - Lights Retention ScaleDokument6 Seiten215 - Ar-4 - Lights Retention ScaleDenise StephensNoch keine Bewertungen

- About Nonverbal CommunicationsDokument21 SeitenAbout Nonverbal CommunicationsKurnia WanNoch keine Bewertungen

- Canteen Project ReportDokument119 SeitenCanteen Project ReportAbody 7337Noch keine Bewertungen

- Trysil enDokument58 SeitenTrysil enManoel Pedro G De M JuniorNoch keine Bewertungen

- Buying Train TicketDokument2 SeitenBuying Train Ticketbeloved28021985Noch keine Bewertungen

- SMA IPIEMS SURABAYA - Modul Ajar Bhs Inggris TK LanjutDokument8 SeitenSMA IPIEMS SURABAYA - Modul Ajar Bhs Inggris TK LanjutI Gde Rama Putra YudaNoch keine Bewertungen

- Midterm Exam in Assessment of LearningDokument5 SeitenMidterm Exam in Assessment of LearningNaci John TranceNoch keine Bewertungen

- Markaziy Osiyo Xalqlari EtnologiyasiDokument9 SeitenMarkaziy Osiyo Xalqlari EtnologiyasiSapa KurbanklichevNoch keine Bewertungen