Beruflich Dokumente

Kultur Dokumente

2016 Ch2-MOS Transistors

Hochgeladen von

ជើងកាង ភូមិCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

2016 Ch2-MOS Transistors

Hochgeladen von

ជើងកាង ភូមិCopyright:

Verfügbare Formate

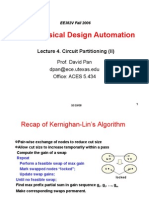

Chapter 2:

MOS

Transistor

Theory

1. MOS transistor operation

2. I-V characteristics

3. C-V characteristics

4. DC transfer characteristics

2: MOS Transistor Theory 1

1. MOS Transistor Operation

So far, we have treated transistors as ideal switches

An ON transistor passes a finite amount of current

– Depends on terminal voltages

– Derive current-voltage (I-V) relationships

Transistor gate, source, drain all have capacitance

– I = C (DV/Dt) -> Dt = (C/I) DV

– Capacitance and current determine speed

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 2

MOS Capacitor

Gate and body form MOS

capacitor polysilicon gate

Operating modes

V <0 g

silicon dioxide insulator

+

- p-type body

– Accumulation

– Depletion (a)

– Inversion 0<V <V g t

depletion region

+

-

(b)

Vg > Vt

inversion region

+

- depletion region

(c)

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 3

Terminal Voltages

Mode of operation depends on Vg, Vd, Vs Vg

– Vgs = Vg – Vs Vgs

+ +

Vgd

– Vgd = Vg – Vd - -

– Vds = Vd – Vs = Vgs - Vgd Vs

-

Vds +

Vd

Source and drain are symmetric diffusion terminals

– By convention, source is terminal at lower voltage

– Hence Vds 0

nMOS body is grounded. First assume source is 0 too.

Three regions of operation

– Cutoff

– Linear

– Saturation

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 4

nMOS Cutoff

No channel

Ids ≈ 0

Vgs = 0 Vgd

+ g +

- -

s d

n+ n+

p-type body

b

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 5

nMOS Linear

Channel forms

Current flows from d to s

V > Vt

– e from s to d Vgd = Vgs

gs

- + g +

- -

Ids increases with Vds s d

Vds = 0

n+ n+

Similar to linear resistor p-type body

b

Vgs > Vt

Vgs > Vgd > Vt

+ g +

- - Ids

s d

n+ n+

0 < Vds < Vgs-Vt

p-type body

b

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 6

nMOS Saturation

Channel pinches off

Ids independent of Vds

We say current saturates

Similar to current source

Vgs > Vt

g Vgd < Vt

+ +

- -

s d Ids

n+ n+

Vds > Vgs-Vt

p-type body

b

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 7

2. I-V Characteristics

In Linear region, Ids depends on

– How much charge is in the channel?

– How fast is the charge moving?

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 8

Channel Charge

MOS structure looks like parallel plate capacitor

while operating in inversions

– Gate – oxide – channel

Qchannel = CV

C = Cg = eoxWL/tox = CoxWL Cox = eox / tox

V = Vgc – Vt = (Vgs – Vds/2) – Vt

gate

Vg

polysilicon + +

gate source Vgs Cg Vgd drain

W

Vs - - Vd

tox

channel

n+ - + n+

SiO2 gate oxide

Vds

L

n+ n+ (good insulator, eox = 3.9) p-type body

p-type body

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 9

Channel Charge

MOS structure looks like parallel

plate capacitor while operating in

inversion:

Gate – oxide – channel

Qchannel = CV

C = Cg = eoxWL/tox = coxWL

V = Vgc – Vt = (Vgs – Vds/2) – Vt

cox = eox / tox

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 10

Carrier velocity

Charge is carried by e-

Electrons are propelled by the lateral electric field

between source and drain

– E = Vds/L

Carrier velocity v proportional to lateral E-field

– v = mE m called mobility

Time for carrier to cross channel:

– t=L/v

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 11

nMOS Linear I-V

Now we know

– How much charge Qchannel is in the channel

– How much time t each carrier takes to cross

Qchannel

I ds

t

mCox

W V V Vds V

gs ds

2

t

L

W

Vgs Vt ds Vds

V = mCox

2 L

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 12

nMOS Saturation I-V

If Vgd < Vt, channel pinches off near drain

– When Vds > Vdsat = Vgs – Vt

Now drain voltage no longer increases current

I ds Vgs Vt

Vdsat V

dsat

2

Vt

2

V gs

2

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 13

nMOS I-V Summary

Shockley 1st order transistor models

0 Vgs Vt cutoff

Vds V V V

I ds Vgs Vt ds linear

2

ds dsat

Vgs Vt

2

Vds Vdsat saturation

2

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 14

Example

We will be using a 0.6 mm process for your project

– From AMI Semiconductor

– tox = 100 Å 2.5

V =5

– m = 350 cm /V*s

gs

2

2

– Vt = 0.7 V 1.5 V =4

Ids (mA)

gs

Plot Ids vs. Vds 1

– Vgs = 0, 1, 2, 3, 4, 5 0.5

V =3 gs

– Use W/L = 4/2 l

V =2 gs

V =1 gs

0

0 1 2 3 4 5

W 3.9 8.85 1014 W W Vds

mCox 350 8 120 μA/V2

L 100 10 L L

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 15

pMOS I-V

All dopings and voltages are inverted for pMOS

– Source is the more positive terminal

Mobility mp is determined by holes

– Typically 2-3x lower than that of electrons mn

– 120 cm2/V•s in AMI 0.6 mm process

0

Thus pMOS must be wider to

Vgs = -1

Vgs = -2

-0.2

provide same current Vgs = -3

– In this class, assume

Ids (mA)

-0.4

Vgs = -4

mn / mp = 2 -0.6

Vgs = -5

-0.8

-5 -4 -3 -2 -1 0

Vds

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 16

Assignment

Consider an nMOS transistor in a 0.6 mm process

with W/L = 4/2 l (i.e., 1.2/0.6 mm). In this process,

the gate oxide thickness is 100 Ao and the mobility of

electrons is 350 cm2/V· s. The threshold voltage is

0.7 V. Plot Ids vs. Vds for Vgs = 0, 1, 2, 3, 4, and 5 V.

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 17

3. C-V Characteristics

Any two conductors separated by an insulator have

capacitance

Gate to channel capacitor is very important

– Creates channel charge necessary for operation

Source and drain have capacitance to body

– Across reverse-biased diodes

– Called diffusion capacitance because it is

associated with source/drain diffusion

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 18

Gate Capacitance

Approximate channel as connected to source

Cg = CoxWL = CpermicronW

Cpermicron = CoxL = eoxL/tox

Cpermicron is typically about 2 fF/mm

polysilicon

gate

W

tox

L SiO2 gate oxide

n+ n+ (good insulator, eox = 3.9e0)

p-type body

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 19

Gate Capacitance

When the transistor is off, the channel is not inverted

Cg = Cgb = eoxWL/tox = CoxWL

Let’s call CoxWL = C0

When the transistor is on, the channel extends from the source

to the drain (if the transistor is unsaturated, or to the pinchoff

point otherwise)

Cg = Cgb + Cgs + Cgd

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 20

Gate Capacitance

In reality the gate overlaps source and drain.

Thus, the gate capacitance should include not

only the intrinsic capacitance but also parasitic

overlap capacitances:

Cgs(overlap) = Cox W LD

Cgs(overlap) = Cox W LD

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 21

Detailed Gate Capacitance

Capacitance Cutoff Linear Saturation

Cgb (total) C0 0 0

Cgd (total) CoxWLD C0/2 + CoxWLD CoxWLD

Cgs (total) CoxWLD C0/2 + CoxWLD 2/3 C0+ CoxWLD

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 22

Diffusion Capacitance

Csb, Cdb

Undesirable, called parasitic capacitance

Capacitance depends on area and perimeter

– Use small diffusion nodes

– Comparable to Cg

for contacted diff

– ½ Cg for uncontacted

– Varies with process

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 23

Lumped representation of the MOSFET capacitances

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 24

Review

1. Which factors affect to switching speed of MOS

transistors?

2. What are three operation modes of MOS

transistors?

3. When is a MOS transistor OFF?

4. When does a MOS transistor operate in saturation

region?

5. What does the drain-source current Ids depend on?

6. What does the gate capacitance Cg depend on?

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 25

4. DC Transfer Characteristics

Assuming the input changes slowly enough that

capacitances have plenty of time to charge or

discharge.

Specific ranges of input and output voltages are

defined as valid 0 and 1 logic levels

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 26

DC Response

DC Response: Vout vs. Vin for a gate

Ex: Inverter

– When Vin = 0 -> Vout = VDD

– When Vin = VDD -> Vout = 0

VDD

– In between, Vout depends on

transistor size and current Idsp

Vin Vout

– By KCL, must settle such that Idsn

Idsn = |Idsp|

– We could solve equations

– But graphical solution gives more insight

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 27

Transistor Operation

Current depends on region of transistor behavior

For what Vin and Vout are nMOS and pMOS in

– Cutoff?

– Linear?

– Saturation?

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 28

nMOS Operation

Cutoff Linear Saturated

Vgsn < Vtn Vgsn > Vtn Vgsn > Vtn

Vin < Vtn Vin > Vtn Vin > Vtn

Vdsn < Vgsn – Vtn Vdsn > Vgsn – Vtn

Vout < Vin - Vtn Vout > Vin - Vtn

VDD

Vgsn = Vin Idsp

Vin Vout

Vdsn = Vout Idsn

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 29

pMOS Operation

Cutoff Linear Saturated

Vgsp > Vtp Vgsp < Vtp Vgsp < Vtp

Vin > VDD + Vtp Vin < VDD + Vtp Vin < VDD + Vtp

Vdsp > Vgsp – Vtp Vdsp < Vgsp – Vtp

Vout > Vin - Vtp Vout < Vin - Vtp

VDD

Vgsp = Vin - VDD Vtp < 0 Idsp

Vin Vout

Vdsp = Vout - VDD Idsn

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 30

I-V Characteristics

Make pMOS is wider than nMOS such that n = p

Vgsn5

Idsn Vgsn4

-Vdsp Vgsn3

-VDD Vgsn2

Vgsp1 Vgsn1

Vgsp2 0 VDD

Vgsp3 Vdsn

Vgsp4 -Idsp

Vgsp5

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 31

Current vs. Vout, Vin

Vin0 Vin5

Vin1 Vin4

Idsn, |Idsp|

Vin2 Vin3

Vin3 Vin2

Vin4 Vin1

VDD

Vout

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 32

Load Line Analysis

For a given Vin:

– Plot Idsn, Idsp vs. Vout

– Vout must be where |currents| are equal in

Vin0 Vin5

Vin1 Vin4

Idsn, |Idsp|

VDD

Vin2 Vin3

Idsp

Vin3 Vin2 Vin Vout

Vin4 Vin1 Idsn

VDD

Vout

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 33

Load Line Analysis

Vin = 0V

0.4V

0.6V

0.8V

.2V

DD DD

DD

Vin0 Vin5

in5

Vin1 Vin4

dsn, |Idsp

Idsn dsp

|

Vin2 Vin3

Vin3 Vin2

Vin4 Vin1

in0

VDD

Vout

out

DD

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 34

DC Transfer Curve

Transcribe points onto Vin vs. Vout plot

Vin0 Vin1

VDD Vin2

Vin0 Vin5

A B

Vout

Vin1 Vin4

C

Vin2 Vin3

Vin3

Vin3 Vin2 D Vin4 Vin5

Vin4 Vin1 E

0 Vtn VDD/2 VDD+Vtp

VDD VDD

Vout Vin

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 35

Operating Regions

Revisit transistor operating regions VDD

Vin Vout

Region nMOS pMOS

A Cutoff Linear

VDD

B Saturation Linear A B

C Saturation Saturation Vout

C

D Linear Saturation

E Linear Cutoff

D

E

0 Vtn VDD/2 VDD+Vtp

VDD

Vin

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 36

Beta Ratio

If p / n 1, switching point will move from VDD/2

Called skewed gate

Other gates: collapse into equivalent inverter

VDD

p

10

n

Vout 2

1

0.5

p

0.1

n

0

VDD

Vin

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 37

Noise Margins

How much noise can a gate input see before it does

not recognize the input?

Output Characteristics Input Characteristics

VDD

Logical High

Output Range VOH Logical High

Input Range

NMH

VIH

Indeterminate

VIL Region

NML

Logical Low

Logical Low VOL Input Range

Output Range

GND

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 38

Logic Levels

To maximize noise margins, select logic levels at

– unity gain point of DC transfer characteristic

Vout

Unity Gain Points

VDD

Slope = -1

VOH

p/ n > 1

Vin Vout

VOL

Vin

0

Vtn VIL VIH VDD- VDD

|Vtp|

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 39

Transient Response

DC analysis tells us Vout if Vin is constant

Transient analysis tells us Vout(t) if Vin(t) changes

– Requires solving differential equations

Input is usually considered to be a step or ramp

– From 0 to VDD or vice versa

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 40

Inverter Step Response

Ex: find step response of inverter driving load cap

Vin (t ) u(t t0 )VDD

Vin(t)

Vout (t t0 ) VDD Vout(t)

Cload

dVout (t ) I dsn (t )

Idsn(t)

dt Cload

Vin(t)

0 t t0

I dsn (t )

Vout VDD Vt

2

2 V DD V Vout(t)

t

VDD Vt out 2 V (t ) V V V

V (t )

out t0

out DD t

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 41

Pass Transistors

We have assumed source is grounded

What if source > 0?

VDD

– e.g. pass transistor passing VDD

VDD

Vg = VDD

– If Vs > VDD-Vt, Vgs < Vt

– Hence transistor would turn itself off

nMOS pass transistors pull no higher than VDD-Vtn

– Called a degraded “1”

– Approach degraded value slowly (low Ids)

pMOS pass transistors pull no lower than Vtp

Transmission gates are needed to pass both 0 and 1

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 42

Pass Transistor Ckts

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 43

Pass Transistor Ckts

VDD VDD VDD

VDD VDD

VDD

Vs = VDD-Vtn VDD-Vtn

VDD-Vtn VDD-Vtn

VDD

VDD-Vtn

Vs = |Vtp|

VDD VDD-2Vtn

VSS

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 44

Transmission Gates

Pass transistors produce degraded outputs

Transmission gates pass both 0 and 1 well

CMOS VLSI Design 4th Ed.

Transmission gate ON resistance

CMOS VLSI Design 4th Ed.

Review

1. What are conditions for Vgs when the nMOS is in cutoff, linear,

and saturated modes?

2. What is noise margin?

3. What is transmission gate and its applications?

4. What are Vtp and Vtn ?

5. Give expressions for the output voltage.

2: MOS Transistor Theory CMOS VLSI Design 4th Ed. 47

Das könnte Ihnen auch gefallen

- Vittoz Weak Inversion in Analog and Digital Circuits PDFDokument33 SeitenVittoz Weak Inversion in Analog and Digital Circuits PDFRavinder KumarNoch keine Bewertungen

- Fully Differential CMOS Voltage AmplifierDokument16 SeitenFully Differential CMOS Voltage AmplifierAjit Narwal0% (1)

- Level Shifter PDFDokument6 SeitenLevel Shifter PDFKAMARUDHEEN KPNoch keine Bewertungen

- LamdaDokument23 SeitenLamdaparrotpanduNoch keine Bewertungen

- VLSI Full Custom Mask LayoutDokument18 SeitenVLSI Full Custom Mask LayoutRamanaButterflyNoch keine Bewertungen

- Contactless Tachomete R: Group Members: Moruboyina Alekhya Kodi Padmasree D.Hima VarshaDokument11 SeitenContactless Tachomete R: Group Members: Moruboyina Alekhya Kodi Padmasree D.Hima VarshaAswin Harippad100% (1)

- IC Design 3 - Basic MOS Device PhysicsDokument59 SeitenIC Design 3 - Basic MOS Device PhysicsNana Sarkodie KwakyeNoch keine Bewertungen

- Lecture18 GRDokument36 SeitenLecture18 GRapi-3834272Noch keine Bewertungen

- Lecture 7 - CMOS DC - Transient ResponseDokument40 SeitenLecture 7 - CMOS DC - Transient Responsesadia santaNoch keine Bewertungen

- Lecture8 Floorplan2Dokument34 SeitenLecture8 Floorplan2api-3834272Noch keine Bewertungen

- VLSI UNIT 1 Part - III PDFDokument35 SeitenVLSI UNIT 1 Part - III PDFKARTHIKAYEN ANoch keine Bewertungen

- Lecture 2 - CMOS FabricationDokument39 SeitenLecture 2 - CMOS Fabricationsadia santaNoch keine Bewertungen

- SEL 4283 Analog CMOS IC Design Single Stage Amplifiers: Small Signal Model 1Dokument52 SeitenSEL 4283 Analog CMOS IC Design Single Stage Amplifiers: Small Signal Model 1jitendraNoch keine Bewertungen

- Zipper Cmos Logic CircuitDokument15 SeitenZipper Cmos Logic CircuitShreerama Samartha G BhattaNoch keine Bewertungen

- Tutorial On Layout of Mixed-Signal CircuitsDokument29 SeitenTutorial On Layout of Mixed-Signal CircuitsPetru NistorNoch keine Bewertungen

- Lecture 5Dokument47 SeitenLecture 5Ershad ShaikNoch keine Bewertungen

- Principles of Semiconductor Devices-L32Dokument25 SeitenPrinciples of Semiconductor Devices-L32LIAKMANNoch keine Bewertungen

- Chip IO Circuit Design - IO Buffers Design in IC CommunicationsDokument84 SeitenChip IO Circuit Design - IO Buffers Design in IC CommunicationsVăn CôngNoch keine Bewertungen

- Enee359a Sizing PDFDokument47 SeitenEnee359a Sizing PDFRakesh SahuNoch keine Bewertungen

- Lecture12 Placement 3Dokument51 SeitenLecture12 Placement 3api-3834272Noch keine Bewertungen

- Mod1VLSI TECHNOLOGY1Dokument65 SeitenMod1VLSI TECHNOLOGY1Jomon VargheseNoch keine Bewertungen

- Lecture3 PartitionDokument24 SeitenLecture3 Partitionapi-3834272Noch keine Bewertungen

- Two Stage Op-AmpDokument4 SeitenTwo Stage Op-AmpShreerama Samartha G BhattaNoch keine Bewertungen

- CMOS CM & Biasing CircuitsDokument50 SeitenCMOS CM & Biasing Circuitsabhi_jNoch keine Bewertungen

- Random Offset CMOS IC Design CU Lecture Art Zirger PDFDokument46 SeitenRandom Offset CMOS IC Design CU Lecture Art Zirger PDFgr8minds4allNoch keine Bewertungen

- Lecture21 dr1Dokument31 SeitenLecture21 dr1api-3834272Noch keine Bewertungen

- CT Delta Sigma ADC TutorialDokument77 SeitenCT Delta Sigma ADC TutorialhomaNoch keine Bewertungen

- Cadence SpectreRF Periodic AnalysisDokument37 SeitenCadence SpectreRF Periodic Analysisreader_188Noch keine Bewertungen

- Ese570 Mos Theory p206Dokument41 SeitenEse570 Mos Theory p206premkumar8719Noch keine Bewertungen

- Charge Redistribution AdcDokument74 SeitenCharge Redistribution AdcAnonymous eWMnRr70qNoch keine Bewertungen

- Dynamic Logic Circuits: Kang and Leblebicic, Chapter 9Dokument34 SeitenDynamic Logic Circuits: Kang and Leblebicic, Chapter 9Lovey SalujaNoch keine Bewertungen

- Body EffectDokument2 SeitenBody EffectAtharva Lele100% (1)

- Preventing Latch Up - NationalDokument2 SeitenPreventing Latch Up - Nationalkvpk_vlsiNoch keine Bewertungen

- PCIRF 3 1 LayoutDokument61 SeitenPCIRF 3 1 LayoutMarius FerdyNoch keine Bewertungen

- Lecture23 dr3Dokument37 SeitenLecture23 dr3api-3834272Noch keine Bewertungen

- MOSFET Current and Voltage CharacteristicsDokument5 SeitenMOSFET Current and Voltage Characteristicssri karthik kadapaNoch keine Bewertungen

- Lecture4 Partition2Dokument51 SeitenLecture4 Partition2api-3834272Noch keine Bewertungen

- ECE 410: VLSI Design Course Lecture Notes: (Uyemura Textbook)Dokument54 SeitenECE 410: VLSI Design Course Lecture Notes: (Uyemura Textbook)BHANU PRAKASH0% (1)

- Two-Stage CMOS Op-Amp Circuit Design - Jianfeng SunDokument17 SeitenTwo-Stage CMOS Op-Amp Circuit Design - Jianfeng Sunjianfeng sun100% (2)

- CMOS BasicsDokument41 SeitenCMOS BasicsYeshoda MallikarjunaNoch keine Bewertungen

- Digital Integrated Circuits: A Design PerspectiveDokument84 SeitenDigital Integrated Circuits: A Design PerspectivedurraizaliNoch keine Bewertungen

- Cmos Vlsi Basic Circuit Design Concepts Unit 4 (5th Sem)Dokument82 SeitenCmos Vlsi Basic Circuit Design Concepts Unit 4 (5th Sem)Sameer Panchal100% (2)

- PROJECT1 S 2013 v2 PDFDokument4 SeitenPROJECT1 S 2013 v2 PDFHarshal SinghNoch keine Bewertungen

- Stick Diagram BasicsDokument26 SeitenStick Diagram Basicssanju012100% (1)

- Digital Integrated Circuits: A Design PerspectiveDokument113 SeitenDigital Integrated Circuits: A Design Perspectiveapi-127299018Noch keine Bewertungen

- Chapter3 Rabaey MOS Capacitances OnlyDokument19 SeitenChapter3 Rabaey MOS Capacitances OnlyRaheetha AhmedNoch keine Bewertungen

- Body Effect: What Do You Need To Know To Understand This Topic?Dokument4 SeitenBody Effect: What Do You Need To Know To Understand This Topic?Rohith RajNoch keine Bewertungen

- Lecture17 RoutingDokument51 SeitenLecture17 Routingapi-3834272Noch keine Bewertungen

- CMOS Process FlowDokument35 SeitenCMOS Process Flowag21937570Noch keine Bewertungen

- 9085 CMOS Analog Design Chapter 5Dokument25 Seiten9085 CMOS Analog Design Chapter 5istlyyNoch keine Bewertungen

- VLSI Questions Answers r3Dokument79 SeitenVLSI Questions Answers r3Gowtham HariNoch keine Bewertungen

- CMOS Power Dissipation and Trends: R. AmirtharajahDokument60 SeitenCMOS Power Dissipation and Trends: R. AmirtharajahmarshaldvtNoch keine Bewertungen

- Layout of CMOS Analog CircuitsDokument0 SeitenLayout of CMOS Analog CircuitsarammartNoch keine Bewertungen

- Design Rules: Bridges Between Technology Capability and Design ConsiderationsDokument7 SeitenDesign Rules: Bridges Between Technology Capability and Design ConsiderationsutpalwxyzNoch keine Bewertungen

- Delay Time Estimation in Digital DesignDokument12 SeitenDelay Time Estimation in Digital DesignSandeep PaulNoch keine Bewertungen

- Lecture1 IntroDokument35 SeitenLecture1 Introapi-3834272Noch keine Bewertungen

- Cmos Design Rules Layout PDFDokument33 SeitenCmos Design Rules Layout PDFkrishnaavNoch keine Bewertungen

- MOS Integrated Circuit DesignVon EverandMOS Integrated Circuit DesignE. WolfendaleNoch keine Bewertungen

- 3109-SIP18H: SANYO Electric Co.,Ltd. Semiconductor Bussiness HeadquartersDokument9 Seiten3109-SIP18H: SANYO Electric Co.,Ltd. Semiconductor Bussiness Headquartersជើងកាង ភូមិNoch keine Bewertungen

- Advanced Technologies To Accelerate Mixed Signal Simulation: Pieter J. MostermanDokument21 SeitenAdvanced Technologies To Accelerate Mixed Signal Simulation: Pieter J. Mostermanជើងកាង ភូមិNoch keine Bewertungen

- HVAC Cooling Load Procedure Guideline Lo0Dokument62 SeitenHVAC Cooling Load Procedure Guideline Lo0api-385802594% (36)

- 2IN35 - VLSI Programming - Lab Work: Assignment 1: Hardware Design Using VerilogDokument13 Seiten2IN35 - VLSI Programming - Lab Work: Assignment 1: Hardware Design Using Verilogជើងកាង ភូមិNoch keine Bewertungen

- LA4705Dokument8 SeitenLA4705ជើងកាង ភូមិNoch keine Bewertungen

- Answers GPPS1Dokument4 SeitenAnswers GPPS1ជើងកាង ភូមិNoch keine Bewertungen

- RTDSP c10 Digital Audio ApplicationsDokument37 SeitenRTDSP c10 Digital Audio Applicationsជើងកាង ភូមិNoch keine Bewertungen

- La 4440Dokument13 SeitenLa 4440Yonatan AgustianusNoch keine Bewertungen

- 17-W, 2-Channel BTL AF High-Efficiency Power Amplifier For Car Stereo SystemsDokument10 Seiten17-W, 2-Channel BTL AF High-Efficiency Power Amplifier For Car Stereo Systemsជើងកាង ភូមិNoch keine Bewertungen

- RTDSP c3 ArchitectureDSPDokument75 SeitenRTDSP c3 ArchitectureDSPជើងកាង ភូមិNoch keine Bewertungen

- Analog and Digital Filter: Fall 2018Dokument5 SeitenAnalog and Digital Filter: Fall 2018ជើងកាង ភូមិNoch keine Bewertungen

- PID - Control & Ziegler-NicholsDokument36 SeitenPID - Control & Ziegler-NicholsHachemi BheNoch keine Bewertungen

- 17-W, 2-Channel BTL AF High-Efficiency Power Amplifier For Car Audio SystemsDokument10 Seiten17-W, 2-Channel BTL AF High-Efficiency Power Amplifier For Car Audio Systemsជើងកាង ភូមិNoch keine Bewertungen

- RTDSP c4 Discrete Time SystemDokument22 SeitenRTDSP c4 Discrete Time Systemជើងកាង ភូមិNoch keine Bewertungen

- Circuits Design For Low Power: Advance Digital Integrated Circuit DesignDokument53 SeitenCircuits Design For Low Power: Advance Digital Integrated Circuit Designជើងកាង ភូមិNoch keine Bewertungen

- Thesis ThuNgaDokument159 SeitenThesis ThuNgaជើងកាង ភូមិNoch keine Bewertungen

- RTDSP c10 Digital Audio ApplicationsDokument37 SeitenRTDSP c10 Digital Audio Applicationsជើងកាង ភូមិNoch keine Bewertungen

- 2016 Ch1-Intro PDFDokument16 Seiten2016 Ch1-Intro PDFTrần Anh TânNoch keine Bewertungen

- VLSI Ch4 DelayDokument27 SeitenVLSI Ch4 Delayជើងកាង ភូមិNoch keine Bewertungen

- Electronic Workbench Multisim Tutorial (Basic)Dokument25 SeitenElectronic Workbench Multisim Tutorial (Basic)ជើងកាង ភូមិNoch keine Bewertungen

- Circuit Layout EulerDokument72 SeitenCircuit Layout Eulerជើងកាង ភូមិNoch keine Bewertungen

- Circuit Layout EulerDokument72 SeitenCircuit Layout Eulerជើងកាង ភូមិNoch keine Bewertungen

- Power and Energy Basics: Hieu M. NguyenDokument46 SeitenPower and Energy Basics: Hieu M. Nguyenជើងកាង ភូមិNoch keine Bewertungen

- MultiSim User Manual PDFDokument814 SeitenMultiSim User Manual PDFObed MaldonadoNoch keine Bewertungen

- 5989 9978enDokument38 Seiten5989 9978enជើងកាង ភូមិNoch keine Bewertungen

- Lect7 PowerDokument29 SeitenLect7 PowerAshok ObuliNoch keine Bewertungen

- 2016 Ch4-DelayDokument31 Seiten2016 Ch4-Delayជើងកាង ភូមិNoch keine Bewertungen

- 2016 Ch1-Intro PDFDokument16 Seiten2016 Ch1-Intro PDFTrần Anh TânNoch keine Bewertungen

- 2016 ch3-CMOS Technology PDFDokument31 Seiten2016 ch3-CMOS Technology PDFTrần Anh TânNoch keine Bewertungen

- HVDC Substation Technology - QTTDokument42 SeitenHVDC Substation Technology - QTT'Θκ'βύτ-Ίισνέγσύ.Noch keine Bewertungen

- AN127Dokument32 SeitenAN127piyushpandeyNoch keine Bewertungen

- Bosch Knock Sensors PiezoDokument2 SeitenBosch Knock Sensors Piezoschraeuble100% (1)

- VNQ660SP DatasheetDokument26 SeitenVNQ660SP Datasheetroberto caiadoNoch keine Bewertungen

- Test PaperDokument72 SeitenTest PaperarsenalmctNoch keine Bewertungen

- Stamford DM110 Voltage RegulatorDokument71 SeitenStamford DM110 Voltage RegulatorThomas Pendergrass100% (2)

- An-9052 Design Guide For Selection of Bootstrap ComponentsDokument4 SeitenAn-9052 Design Guide For Selection of Bootstrap Componentsディエゴ水上Noch keine Bewertungen

- Ir 2153Dokument8 SeitenIr 2153oasdopdasNoch keine Bewertungen

- BSS100Dokument7 SeitenBSS100JHNoch keine Bewertungen

- Impulse Generator: Instructed byDokument5 SeitenImpulse Generator: Instructed bysaandoNoch keine Bewertungen

- Low-Jitter Process-Independent DLL and PLL Based On Self-Biased Techniques (John G. Maneatis)Dokument10 SeitenLow-Jitter Process-Independent DLL and PLL Based On Self-Biased Techniques (John G. Maneatis)Aram ShishmanyanNoch keine Bewertungen

- Computer MemoryDokument19 SeitenComputer MemoryUdara R Weerasinghe67% (6)

- DS1220AB/AD 16k Nonvolatile SRAM: Features Pin AssignmentDokument9 SeitenDS1220AB/AD 16k Nonvolatile SRAM: Features Pin AssignmentJoel PalzaNoch keine Bewertungen

- Datasensor S6 1A6Dokument4 SeitenDatasensor S6 1A6Juan M MesaNoch keine Bewertungen

- Vlsi Lesson PlanDokument3 SeitenVlsi Lesson Planeshwar_worldNoch keine Bewertungen

- PRX Series Input Board Parts ListDokument2 SeitenPRX Series Input Board Parts ListJames MontalvoNoch keine Bewertungen

- DICA - Bits - Without Ans - docxQFWGDokument9 SeitenDICA - Bits - Without Ans - docxQFWGkirankumarperamNoch keine Bewertungen

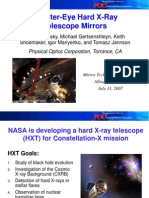

- Lobster Eye Hard X-Ray MirrorsDokument36 SeitenLobster Eye Hard X-Ray MirrorsmcanaliNoch keine Bewertungen

- VACC VibrationInResearchSettingsDokument1 SeiteVACC VibrationInResearchSettingsrernitmcNoch keine Bewertungen

- 8-Bit Gray Code Converter: by Martin Serena, Dang Ly, Khoa LyDokument58 Seiten8-Bit Gray Code Converter: by Martin Serena, Dang Ly, Khoa LyAndreSantosNoch keine Bewertungen

- 2he PDFDokument188 Seiten2he PDFnbr67sceNoch keine Bewertungen

- KATS Universal ProgrammerDokument6 SeitenKATS Universal ProgrammerdorudNoch keine Bewertungen

- Isc 2SD998: Silicon NPN Power TransistorDokument2 SeitenIsc 2SD998: Silicon NPN Power TransistorDjoNoch keine Bewertungen

- 19 Speed PDFDokument8 Seiten19 Speed PDFNur Muhammad DzikriNoch keine Bewertungen

- Illustrated Assembly Manual k4003 Rev1 PDFDokument12 SeitenIllustrated Assembly Manual k4003 Rev1 PDFMilan MilosavljevićNoch keine Bewertungen

- Password Based Circuit Breaker Control To Ensure Electric Line Mans Safety and Load Sharing IJERTCONV5IS13135Dokument4 SeitenPassword Based Circuit Breaker Control To Ensure Electric Line Mans Safety and Load Sharing IJERTCONV5IS13135Pratiksha SankapalNoch keine Bewertungen

- Topic 5 3 Formative-2Dokument3 SeitenTopic 5 3 Formative-2api-296446683Noch keine Bewertungen

- Specification No.: Ministry of Electricity Planning and Studies Office Baghdad - IraqDokument10 SeitenSpecification No.: Ministry of Electricity Planning and Studies Office Baghdad - IraqyildirimonlineNoch keine Bewertungen

- Sboa 290 CSHXGHDCXCFXDDCGDokument6 SeitenSboa 290 CSHXGHDCXCFXDDCGKarthik SuryaNoch keine Bewertungen