Beruflich Dokumente

Kultur Dokumente

PCIe Express Overview

Hochgeladen von

Shantanu Mishra0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

84 Ansichten8 SeitenPCIe is a point-to-point, scalable bus standard that uses a layered stack including transaction, data link and physical layers. It uses a fixed addressing scheme for device configuration space and base address registers to map memory or I/O resources. Devices communicate interrupts via message-signaled interrupts by performing memory writes instead of asserting physical lines. A PCIe driver enables the device, requests resources, sets DMA sizes, accesses configuration space, registers interrupt handlers and enables processing.

Originalbeschreibung:

PCIe

Originaltitel

PCIe

Copyright

© © All Rights Reserved

Verfügbare Formate

PPTX, PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenPCIe is a point-to-point, scalable bus standard that uses a layered stack including transaction, data link and physical layers. It uses a fixed addressing scheme for device configuration space and base address registers to map memory or I/O resources. Devices communicate interrupts via message-signaled interrupts by performing memory writes instead of asserting physical lines. A PCIe driver enables the device, requests resources, sets DMA sizes, accesses configuration space, registers interrupt handlers and enables processing.

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PPTX, PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

84 Ansichten8 SeitenPCIe Express Overview

Hochgeladen von

Shantanu MishraPCIe is a point-to-point, scalable bus standard that uses a layered stack including transaction, data link and physical layers. It uses a fixed addressing scheme for device configuration space and base address registers to map memory or I/O resources. Devices communicate interrupts via message-signaled interrupts by performing memory writes instead of asserting physical lines. A PCIe driver enables the device, requests resources, sets DMA sizes, accesses configuration space, registers interrupt handlers and enables processing.

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PPTX, PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 8

PCIe

Peripheral Component Interconnect - Express

Features

• little endian

• point-to-point topology

• 4KB of config registers

• burst oriented (deals data in transactions)

• scalable (lane aggregation)

PCIe stack

• Transaction layer

• Data link layer

• Physical layer

PCIe Bus

• Bus Enumeration

• vendor ID and device ID

• Bus <- Dev <- Function

• Bus Master

• Bus Contention

• Bus Arbitration

Config Space

• uses a fixed addressing scheme

• can request up to six areas of memory

space or I/O port space via its

configuration space registers

• access through CF8h and CFCh 32-bit IO

location

Base Address Registers

• point to the location in the system address space

• can be IO space or Memory space mapped

• each bar is 32-bit

• Concat two BARS for 64-bit addressing

• Bit 0 - Mem or IO

• Mem: BAR[x] & FFFFFFF0h

• IO: BAR[x] & FFFFFFFCh

• Get BAR address size

• Send FFFFFFFF to the BAR[x]

• 0's returned in don't care bits

• ~(BAR[x]) is the size

Interrupts

• four interrupt lines

• are not wired in parallel

• interrupt lines are level-triggered

• message-signaled interrupts

• performs a memory write, instead of asserting a dedicated line.

• alleviates the problem of scarcity of interrupt lines.

• PCIe does not have physical interrupt lines and uses MSI exclusively

• has same latency as mem R/W

PCIe driver

• Enable the device

• Request MMIO/IOP resources

• Set the DMA mask size

• Access device configuration space (if needed)

• Register IRQ handler

• Enable DMA/processing engines

Das könnte Ihnen auch gefallen

- Verification of Dual Port RAM Using System Verilog and UVM: A ReviewDokument6 SeitenVerification of Dual Port RAM Using System Verilog and UVM: A ReviewIJRASETPublicationsNoch keine Bewertungen

- PCI Express: The Evolution of Computer Interface TechnologiesDokument93 SeitenPCI Express: The Evolution of Computer Interface TechnologiesKonica Sarker100% (3)

- MindShare PCIe Replay Buffer SizingDokument12 SeitenMindShare PCIe Replay Buffer Sizingskta100% (1)

- PCIe BasicsDokument34 SeitenPCIe Basicshemanth_scribdNoch keine Bewertungen

- HyperTransport 3.1 Interconnect Technology PDFDokument30 SeitenHyperTransport 3.1 Interconnect Technology PDFmapf5566100% (1)

- Register This Experiences Applying UVM RegistersDokument9 SeitenRegister This Experiences Applying UVM RegistersthecoreNoch keine Bewertungen

- 04 14 LTSSM Implementation at 5GTs and Beyond PDFDokument18 Seiten04 14 LTSSM Implementation at 5GTs and Beyond PDFHardik TrivediNoch keine Bewertungen

- USB in A NutShellDokument33 SeitenUSB in A NutShellNaveed AhmedNoch keine Bewertungen

- MindShare x86 ISADokument1.567 SeitenMindShare x86 ISArrs_1988100% (3)

- How To Verify SOCDokument5 SeitenHow To Verify SOCMohammad Javad GhasemiNoch keine Bewertungen

- MindShare Intro To USB 3.0Dokument20 SeitenMindShare Intro To USB 3.0alexchuahNoch keine Bewertungen

- Introduction To The Packet-Based ProtocolDokument50 SeitenIntroduction To The Packet-Based ProtocolAbhishekNoch keine Bewertungen

- ApbDokument7 SeitenApbdebashispaul_cnNoch keine Bewertungen

- Design and Verification of AMBA APB ProtocolDokument8 SeitenDesign and Verification of AMBA APB ProtocolsiruNoch keine Bewertungen

- WHKETaz Wa FPFT XBXDokument281 SeitenWHKETaz Wa FPFT XBXVenkat MurariNoch keine Bewertungen

- USB3SS_VERIFICATIONDokument34 SeitenUSB3SS_VERIFICATIONSachin Kumar JainNoch keine Bewertungen

- MindShare Intro To PIPE SpecDokument15 SeitenMindShare Intro To PIPE SpecAditya K. PatroNoch keine Bewertungen

- PHY Interface For The PCIe SATA USB32 DisplayPort USB4 Architectures Rev6p1Dokument174 SeitenPHY Interface For The PCIe SATA USB32 DisplayPort USB4 Architectures Rev6p1Baris MetinNoch keine Bewertungen

- Axi DmaDokument62 SeitenAxi DmaSrinivas DangetiNoch keine Bewertungen

- PCI Express White PaperDokument8 SeitenPCI Express White PaperUday KumarNoch keine Bewertungen

- 2-3 SSUSB DevCon LinkLayer ViningDokument54 Seiten2-3 SSUSB DevCon LinkLayer ViningHardik TrivediNoch keine Bewertungen

- Amba 5 Ahb SpecDokument86 SeitenAmba 5 Ahb SpecBo LuNoch keine Bewertungen

- Presentation On Usb 3.0Dokument21 SeitenPresentation On Usb 3.0Anuj KumarNoch keine Bewertungen

- AXI vs AHB: Understanding the Differences Between the Two Popular ARM Bus ProtocolsDokument3 SeitenAXI vs AHB: Understanding the Differences Between the Two Popular ARM Bus ProtocolsPronadeep Bora100% (2)

- PCI Express Introduction: A Guide to the High-Performance I/O BusDokument18 SeitenPCI Express Introduction: A Guide to the High-Performance I/O BusharinisasNoch keine Bewertungen

- Mindshare Pcie Elastic BufferDokument16 SeitenMindshare Pcie Elastic BufferSreenath AkNoch keine Bewertungen

- YAPP Router SpecificationDokument2 SeitenYAPP Router SpecificationHeetashi Arora100% (1)

- White Paper: Pci Express TechnologyDokument11 SeitenWhite Paper: Pci Express Technologyallen3037100% (1)

- Phy Interface Pci Express Sata Usb30 ArchitecturesDokument81 SeitenPhy Interface Pci Express Sata Usb30 ArchitecturesHardik TrivediNoch keine Bewertungen

- Functional VerificationDokument7 SeitenFunctional VerificationDebabrato BanikNoch keine Bewertungen

- The University of New Hampshire Interoperability Laboratory Introduction To Pcie ExpressDokument20 SeitenThe University of New Hampshire Interoperability Laboratory Introduction To Pcie Expressshyamsundar100% (1)

- Overview of PCI ExpressDokument38 SeitenOverview of PCI Expressasic_master0% (1)

- Q T F SVA: Uick Utorial ORDokument60 SeitenQ T F SVA: Uick Utorial ORsubash100% (1)

- Pciec TutorialDokument305 SeitenPciec Tutorialshamshim2000Noch keine Bewertungen

- PCI Express BasicsDokument34 SeitenPCI Express Basicsteo2005100% (1)

- Asic Interview QuestionsDokument2 SeitenAsic Interview Questionspritam044Noch keine Bewertungen

- Synopsys DWDokument11 SeitenSynopsys DWRanjit YewaleNoch keine Bewertungen

- Jtag Boundary Scan PDFDokument64 SeitenJtag Boundary Scan PDFvinothsanNoch keine Bewertungen

- SystemVerilog For VerificationDokument212 SeitenSystemVerilog For VerificationMallikarjun Rb100% (1)

- MindShare ISA 3rd EbookDokument544 SeitenMindShare ISA 3rd Ebookcdrbc100% (1)

- 8B10B CodingDokument29 Seiten8B10B CodingRamakrishnaRao SoogooriNoch keine Bewertungen

- MindShare PCIe30 Ebook v1.0Dokument1.057 SeitenMindShare PCIe30 Ebook v1.0Sasikala Kesava100% (1)

- Introduction To SoCDokument50 SeitenIntroduction To SoCTan Chee YeongNoch keine Bewertungen

- Verification Approach For ASIC Generic IP Functional VerificationDokument3 SeitenVerification Approach For ASIC Generic IP Functional VerificationMohammad Seemab AslamNoch keine Bewertungen

- Xtensalx Overview HandbookDokument260 SeitenXtensalx Overview HandbookRafael AndradeNoch keine Bewertungen

- Pci Bus End Point BlockDokument178 SeitenPci Bus End Point Blockbkrishna_8888460% (1)

- Ethernet ProtocolDokument18 SeitenEthernet ProtocolMohammed Publications100% (1)

- Introducing VCS Basic capabilities and limitationsDokument6 SeitenIntroducing VCS Basic capabilities and limitations7835201010% (1)

- DUI0534B Amba 4 Axi4 Protocol Assertions UgDokument42 SeitenDUI0534B Amba 4 Axi4 Protocol Assertions UgSuman LokondaNoch keine Bewertungen

- Serial Peripheral InterfaceDokument5 SeitenSerial Peripheral InterfaceabhinavbitNoch keine Bewertungen

- Virtual classes, methods, and interfaces in SystemVerilogDokument37 SeitenVirtual classes, methods, and interfaces in SystemVerilogComposerNoch keine Bewertungen

- AxiDokument47 SeitenAxidk13071987100% (4)

- PCIe Interface Development for High Speed Data TransmissionDokument5 SeitenPCIe Interface Development for High Speed Data TransmissionvijithacvijayanNoch keine Bewertungen

- Block Diagram of Intel Atom ProcessorDokument23 SeitenBlock Diagram of Intel Atom Processorfestio94Noch keine Bewertungen

- pg055 Axi Bridge Pcie PDFDokument117 Seitenpg055 Axi Bridge Pcie PDFattilismNoch keine Bewertungen

- Digital Circuit Testing: A Guide to DFT and Other TechniquesVon EverandDigital Circuit Testing: A Guide to DFT and Other TechniquesNoch keine Bewertungen

- System-on-Chip Test Architectures: Nanometer Design for TestabilityVon EverandSystem-on-Chip Test Architectures: Nanometer Design for TestabilityNoch keine Bewertungen

- Bus Comparisons: Bus Type Bus Width Bus Speed MB/se CDokument13 SeitenBus Comparisons: Bus Type Bus Width Bus Speed MB/se CShashank M ChanmalNoch keine Bewertungen

- A Crypto-Watermarking MethodDokument11 SeitenA Crypto-Watermarking Methodmycatalysts100% (1)

- Cryptography Based Digital Image Watermarking Algorithm To Increase Security of Watermark DataDokument4 SeitenCryptography Based Digital Image Watermarking Algorithm To Increase Security of Watermark DataShantanu MishraNoch keine Bewertungen

- BITS Pilani Hyderabad ECE F314 Electromagnetic FieldsDokument3 SeitenBITS Pilani Hyderabad ECE F314 Electromagnetic FieldsShantanu MishraNoch keine Bewertungen

- Course No. Course Title Instructor-in-Charge Instructors TeamDokument2 SeitenCourse No. Course Title Instructor-in-Charge Instructors TeamShantanu MishraNoch keine Bewertungen

- Lenovo w770 Wireless Headset UgDokument13 SeitenLenovo w770 Wireless Headset UgShantanu MishraNoch keine Bewertungen

- Math F231Dokument4 SeitenMath F231Shantanu MishraNoch keine Bewertungen

- Ece F311Dokument4 SeitenEce F311Shantanu MishraNoch keine Bewertungen

- Lec 12-03-2018Dokument12 SeitenLec 12-03-2018Shantanu MishraNoch keine Bewertungen

- Ece F311Dokument4 SeitenEce F311Shantanu MishraNoch keine Bewertungen

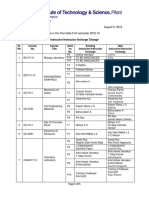

- Timetable 5Dokument5 SeitenTimetable 5Shantanu MishraNoch keine Bewertungen

- HandoutDokument3 SeitenHandoutShantanu MishraNoch keine Bewertungen

- Course No Course Title Instructor-In-ChargeDokument3 SeitenCourse No Course Title Instructor-In-ChargeShantanu MishraNoch keine Bewertungen

- Timetable I Sem 2017-18Dokument99 SeitenTimetable I Sem 2017-18Shantanu MishraNoch keine Bewertungen

- AITS 2018 ScheduleDokument2 SeitenAITS 2018 SchedulewefWE50% (2)

- BTech Academic Regulations PDFDokument4 SeitenBTech Academic Regulations PDFShantanu MishraNoch keine Bewertungen

- Jet Engine HistoryDokument15 SeitenJet Engine HistoryShantanu MishraNoch keine Bewertungen

- Joint Entrance Examination (Main) - 2018: Information BulletinDokument58 SeitenJoint Entrance Examination (Main) - 2018: Information Bulletinplayer9900Noch keine Bewertungen

- 2015A5PS0862HDokument20 Seiten2015A5PS0862HShantanu MishraNoch keine Bewertungen

- Math F311Dokument3 SeitenMath F311Shantanu MishraNoch keine Bewertungen

- Math F313Dokument2 SeitenMath F313Shantanu MishraNoch keine Bewertungen

- Announcement of PracticalsDokument1 SeiteAnnouncement of PracticalsShantanu MishraNoch keine Bewertungen

- Math F313Dokument6 SeitenMath F313Shantanu MishraNoch keine Bewertungen

- Math F312Dokument3 SeitenMath F312Shantanu MishraNoch keine Bewertungen

- 160603193950Dokument97 Seiten160603193950Shantanu MishraNoch keine Bewertungen

- Math F313Dokument2 SeitenMath F313Shantanu MishraNoch keine Bewertungen

- Answer Key T2 F 399 2017Dokument2 SeitenAnswer Key T2 F 399 2017Shantanu MishraNoch keine Bewertungen

- Math F312Dokument3 SeitenMath F312Shantanu MishraNoch keine Bewertungen

- Test I (Solution)Dokument1 SeiteTest I (Solution)Shantanu MishraNoch keine Bewertungen

- HandoutDokument3 SeitenHandoutShantanu MishraNoch keine Bewertungen