Beruflich Dokumente

Kultur Dokumente

Lect-2ARM Processors

Hochgeladen von

yayavaram0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

14 Ansichten16 SeitenCopyright

© © All Rights Reserved

Verfügbare Formate

PPTX, PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

© All Rights Reserved

Verfügbare Formate

Als PPTX, PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

14 Ansichten16 SeitenLect-2ARM Processors

Hochgeladen von

yayavaramCopyright:

© All Rights Reserved

Verfügbare Formate

Als PPTX, PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 16

ARM PROCESSORS ARCHITECTURE

ARM 7TDMI ARCHITECTURE

• The ARM7TDMI processor is a member of the

ARM family v4 of general-purpose 32-bit

microprocessors.

• The ARM family offers high performance for very

low-power consumption and gate count.

• The ARM7TDMI processor has a Von Neumann

architecture, with a single 32-bit data bus carrying

both instructions and data.

• Only load, store, and swap instructions can access

data from memory.

• The ARM7TDMI processor uses a three stage

pipeline to increase the speed of execution.

3 Stage Pipeline

• The three stage pipelined architecture of the

ARM7 processor is shown below.

contd

• The ARM 7 processor is based on Von Neumann

model with a single bus for both data and

instructions.(The ARM 9 uses Harvard model).

• Though this will decrease the performance of

ARM 7, it is overcome by the pipe line concept.

• Also ARM uses the Advanced Microcontroller Bus

Architecture (AMBA) bus architecture.

• This AMBA include two system buses: the AMBA

High-Speed Bus (AHB) or the Advanced System

Bus (ASB), and the Advanced Peripheral Bus

(APB).

contd

• The ARM processor consists of

i.Arithmetic Logic Unit (32-bit)

ii.One Booth multiplier(32-bit)

iii.One Barrel shifter

iv.One Control unit and a

v.Register file of 37 registers each of 32 bits.

• The barrel shifter is used for fast shift operations

and can perform the necessary processing of register

values before it enters the ALU.

• This helps the easy calculation of wider ranges of

expressions and addresses.

contd

• In addition to this the ARM also consists of a

Program status register of 32 bits and some special

registers like the instruction register, memory data

read and write register and memory address

register.

• A Priority encoder which is used in the multiple

load and store instruction to indicate which

register in the register file to be loaded or stored

and Multiplexers etc.

contd

• The block diagram of ARM7 is shown below.

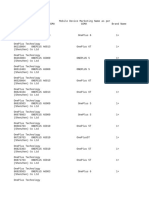

Register organization

• ARM has a total of 37 registers. In which - 31 are

general-purpose registers of 32-bits, and six

status registers .

• But all these registers are not seen at once. The

processor state and operating mode decide which

registers are available to the programmer.

• At any time, among the 31 general purpose

registers only 16 registers are available to the user.

• The remaining 15 registers are used to speed up

exception processing. there are two program status

registers: CPSR and SPSR (Current Program Status

Register & Saved Program Status Register

respectively).

contd

• In ARM state the registers r0 to r13 are orthogonal

it means an instruction that is applied r0 can be

equally applied to any other register.

• The main bank of 16 registers is used by all

unprivileged code.

• These are the User mode registers. User mode is different

from all other modes as it is unprivileged.

• In addition to this register bank, there is also one 32-bit

Current Program status Register(CPSR).

contd

contd

contd

contd

contd

Das könnte Ihnen auch gefallen

- Dma PDFDokument19 SeitenDma PDFTiffany Douglas0% (1)

- Microprocessor Architecture - IIIDokument8 SeitenMicroprocessor Architecture - IIIyayavaramNoch keine Bewertungen

- Microprocessor Architecture - IIDokument16 SeitenMicroprocessor Architecture - IIyayavaramNoch keine Bewertungen

- Challenges and Strategies in Post COVID Higher EducationDokument21 SeitenChallenges and Strategies in Post COVID Higher EducationyayavaramNoch keine Bewertungen

- Application Note Mw38 14nm v7Dokument26 SeitenApplication Note Mw38 14nm v7Apple CeaNoch keine Bewertungen

- ARM ProcessorsDokument16 SeitenARM ProcessorsyayavaramNoch keine Bewertungen

- 8085 Microprocessor ArchitectureDokument16 Seiten8085 Microprocessor ArchitectureyayavaramNoch keine Bewertungen

- Physical Studies of Cyclohexane Derivatives Polarizability and AnisotropyDokument8 SeitenPhysical Studies of Cyclohexane Derivatives Polarizability and AnisotropyyayavaramNoch keine Bewertungen

- Cathode Ray Oscilloscope - Class NotesDokument14 SeitenCathode Ray Oscilloscope - Class NotesyayavaramNoch keine Bewertungen

- PQ2 Mem Control WBT PDFDokument16 SeitenPQ2 Mem Control WBT PDFyayavaramNoch keine Bewertungen

- Study Microwind Tool and Lambda RulesDokument54 SeitenStudy Microwind Tool and Lambda RulesyayavaramNoch keine Bewertungen

- Instruction-Level Parallel Processing History Overview and Perspect PDFDokument57 SeitenInstruction-Level Parallel Processing History Overview and Perspect PDFyayavaramNoch keine Bewertungen

- Electronic Instrumentation 2nd Edition by P.P.L. RegtienDokument413 SeitenElectronic Instrumentation 2nd Edition by P.P.L. Regtiensandeepuae100% (7)

- ARM Processors' - ArchitectureDokument27 SeitenARM Processors' - ArchitectureyayavaramNoch keine Bewertungen

- Design of Analog CMOS Integrated Circuits, Solutions (McGraw) - RAZAVIDokument329 SeitenDesign of Analog CMOS Integrated Circuits, Solutions (McGraw) - RAZAVImtechsurendra12379% (33)

- Bishop BasicMicroprocessorsAndThe6800Dokument273 SeitenBishop BasicMicroprocessorsAndThe6800yayavaramNoch keine Bewertungen

- Instruction-Level Parallel Processing History Overview and Perspect PDFDokument57 SeitenInstruction-Level Parallel Processing History Overview and Perspect PDFyayavaramNoch keine Bewertungen

- Introduction To Image Processing-Class NotesDokument33 SeitenIntroduction To Image Processing-Class NotesyayavaramNoch keine Bewertungen

- DRAM Tutorial Isca2002Dokument146 SeitenDRAM Tutorial Isca2002yayavaramNoch keine Bewertungen

- Microcontrollers - UNIT IDokument45 SeitenMicrocontrollers - UNIT IyayavaramNoch keine Bewertungen

- ElectronicsDokument20 SeitenElectronicsneninthe420Noch keine Bewertungen

- Design of Analog CMOS Integrated Circuits, Solutions (McGraw) - RAZAVIDokument329 SeitenDesign of Analog CMOS Integrated Circuits, Solutions (McGraw) - RAZAVImtechsurendra12379% (33)

- UNIT-II CPLD & FPGA ArchitecturesDokument18 SeitenUNIT-II CPLD & FPGA ArchitecturesyayavaramNoch keine Bewertungen

- Embedded Systems NotesDokument33 SeitenEmbedded Systems Notesyayavaram100% (1)

- UNIT - I CPLD & FPGA ArchitecturesDokument22 SeitenUNIT - I CPLD & FPGA Architecturesyayavaram100% (2)

- Data Communications - NotesDokument26 SeitenData Communications - NotesNarasimha Murthy YayavaramNoch keine Bewertungen

- Introduction to PIC MicrocontrollersDokument69 SeitenIntroduction to PIC MicrocontrollersyayavaramNoch keine Bewertungen

- Crystal Structure & X-Ray Diffraction: Dr. Y. Narasimha MurthyDokument66 SeitenCrystal Structure & X-Ray Diffraction: Dr. Y. Narasimha MurthyyayavaramNoch keine Bewertungen

- Micro Controller Archtecture ProgrammingDokument94 SeitenMicro Controller Archtecture ProgrammingyayavaramNoch keine Bewertungen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5782)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (72)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (890)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (587)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (265)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (119)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- TNavigator Modules Available 2019 ENGDokument26 SeitenTNavigator Modules Available 2019 ENGVitor Azevedo Jr100% (1)

- DE10-Nano Development Kit: TerasicDokument4 SeitenDE10-Nano Development Kit: Terasicsfds fsdaaaNoch keine Bewertungen

- LPC1788 User ManualDokument1.035 SeitenLPC1788 User Manualamuzahid15Noch keine Bewertungen

- CamScanner Document ScansDokument144 SeitenCamScanner Document ScansLuisa PrestesNoch keine Bewertungen

- Dumpsys ANR WindowManagerDokument5.102 SeitenDumpsys ANR WindowManagerSantiago TorresNoch keine Bewertungen

- IP-XACT Standardized IP Interfaces For Rapid IP IntegrationDokument26 SeitenIP-XACT Standardized IP Interfaces For Rapid IP IntegrationAbdul ThoufiqNoch keine Bewertungen

- CamScanner Scanned DocumentDokument1.025 SeitenCamScanner Scanned DocumentAnna Jeilica Lanuza Destura100% (1)

- Apple Iphone 4s - Full Phone SpecificationsDokument2 SeitenApple Iphone 4s - Full Phone SpecificationstaknevNoch keine Bewertungen

- Run-Time Variables Monitoring and Visualization Tool For STM32 DevicesDokument5 SeitenRun-Time Variables Monitoring and Visualization Tool For STM32 DevicesLeandro CapitanelliNoch keine Bewertungen

- Stmicroelectronics: ™ Nucleo/Discovery/Eval Boards: St-Link/V2 andDokument24 SeitenStmicroelectronics: ™ Nucleo/Discovery/Eval Boards: St-Link/V2 andHyung Chan KimNoch keine Bewertungen

- LPC55S06 ManualDokument1.029 SeitenLPC55S06 ManualSATISHREDDYNoch keine Bewertungen

- Ebin - Pub o Algebrista Teoria e Exercicios de Fixaao e Revisao 5400 Exercicios 1300 Questoes Volume 1 1nbsped 8539910241 9788539910243Dokument694 SeitenEbin - Pub o Algebrista Teoria e Exercicios de Fixaao e Revisao 5400 Exercicios 1300 Questoes Volume 1 1nbsped 8539910241 9788539910243Paulo GerneNoch keine Bewertungen

- Analog & Imaging IC Logic LSI: Semiconductor & Storage ProductsDokument28 SeitenAnalog & Imaging IC Logic LSI: Semiconductor & Storage ProductsOlivier López ChNoch keine Bewertungen

- Baremetal On ARMDokument30 SeitenBaremetal On ARMsuchakraNoch keine Bewertungen

- Dumpsys ANR WindowManagerDokument2.376 SeitenDumpsys ANR WindowManagerkatia marmontelNoch keine Bewertungen

- Robotic Arm Edge With USB PC Interface User's ManualDokument53 SeitenRobotic Arm Edge With USB PC Interface User's ManualAndré SousaNoch keine Bewertungen

- 20-विजय के 7 फेरेDokument962 Seiten20-विजय के 7 फेरेvikash singh70% (37)

- MessageDokument3 SeitenMessageSokaina DadamouNoch keine Bewertungen

- Kim Kardashian Hollywood Cheats GeeratorDokument4 SeitenKim Kardashian Hollywood Cheats Geeratorapi-701716959Noch keine Bewertungen

- ELC Multiprocessor FPGA LinuxDokument99 SeitenELC Multiprocessor FPGA LinuxLê Đình TiếnNoch keine Bewertungen

- Gcc4.4.4 Multilib Toolchain Release NoteDokument12 SeitenGcc4.4.4 Multilib Toolchain Release NotepavanbellamNoch keine Bewertungen

- This 18,000mah Battery Has A Phone in ItDokument1 SeiteThis 18,000mah Battery Has A Phone in ItTeacherPaloma AlencarNoch keine Bewertungen

- Lyla B Das - Embedded Systems-Pearson Education (2013) PDFDokument784 SeitenLyla B Das - Embedded Systems-Pearson Education (2013) PDFSrilatha Kolli100% (2)

- Device Inches Resolutionpx Density or Acronym Dpi Resolutiondp AspectratiosDokument4 SeitenDevice Inches Resolutionpx Density or Acronym Dpi Resolutiondp AspectratiosMulugeta EneyewNoch keine Bewertungen

- Zigbee-Based Communication System For Data Transfer Within Future Micro Grids P.Ramakrishna, M.Tech, Kshatriya Engineering College (Kcea)Dokument6 SeitenZigbee-Based Communication System For Data Transfer Within Future Micro Grids P.Ramakrishna, M.Tech, Kshatriya Engineering College (Kcea)sanNoch keine Bewertungen

- DGCA Module 08 MARCH 2017 HANDWRITTEN SET 1 & 2 PDFDokument5 SeitenDGCA Module 08 MARCH 2017 HANDWRITTEN SET 1 & 2 PDFShiva JeevaNoch keine Bewertungen

- FreeRTOS V7.1.0 release notes with new ports and demosDokument32 SeitenFreeRTOS V7.1.0 release notes with new ports and demoslna_cooolmadina5742Noch keine Bewertungen

- Chegg Cracked Apk For AndroidDokument4 SeitenChegg Cracked Apk For AndroidMaria Angel Krystel Ilagan0% (1)

- Approved Tacs 030120Dokument566 SeitenApproved Tacs 030120SiteTester 1371Noch keine Bewertungen