Beruflich Dokumente

Kultur Dokumente

Chapter 6 Thermal Oxidation - I Bo Cui

Hochgeladen von

sbotacondOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Chapter 6 Thermal Oxidation - I Bo Cui

Hochgeladen von

sbotacondCopyright:

Verfügbare Formate

Chapter 6 Thermal oxidation and the Si/SiO2 interface Si(s) + O2(g) SiO2(s)

1. SiO2 properties and applications. 2. Thermal oxidation basics. 3. Manufacturing methods and equipment. 4. Measurement methods. 5. Deal-grove model (linear parabolic model). 6. Thin oxide growth, dependence on gas pressure and crystal orientation 7. Cl-containing gas, 2D growth, substrate doping effect . 8. Interface charges, dopant redistribution.

43: Microfabrication and thin film technology ctor: Bo Cui, ECE, University of Waterloo; http://ece.uwaterloo.ca/~bcui/ ook: Silicon VLSI Technology by Plummer, Deal and Griffin

Properties of thermally grown SiO2

It is amorphous. Stable, reproducible and conformal SiO2 growth Melting point: 1700C Density: 2.21 g/cm3 (almost the same as Si that is 2.33 g/cm3) Crystalline SiO2 [Quartz] = 2.65gm/cm3 Conform al growth Atomic density: 2.3 1022 molecules/cm3

(For Si, it is 5 1022 atoms/cm3)

Refractive index: n=1.46 Dielectric constant: =3.9 (why not =n2?) Excellent electrical insulator: resistivity > 1020 cm, energy gap Eg=8-9 eV. High breakdown electric field: >107 V/cm

The Si/SiO2 interface

Thermal oxide (amorphou s)

Si substrate (single crystal)

The perfect interface between Si and SiO2 is one major reason why Si is used for semiconductor devices (instead of Ge)

Application of SiO2 in IC industry

STI

STI: shallow trench isolation

Very good etching selectivity between Si and SiO2 using HF

SiO2 can provide a selective mask against diffusion at high temperatures. (DSiO2 << Dsi ) Oxides used for masking are 0.51m thick. (not good for Ga)

Diffusion mask for common dopants

Can also be used for mask against ion implantation

Mask thickness ( m)

Diffusion time (hr)

SiO2 masks for B and P 5

Use of oxide in MOSFET

Gate oxide, only 0.8nm thick!

insulation material between interconnection levels and adjacent devices

LOCOS: local oxidation isolation; STI: shallow trench isolation

6

Local Oxidation of Si (LOCOS)

Fully recessed process attempts to minimize birds peak.

For nanofabrication: oxidation sharpening for sharp AFM tips or field emitters for display

Si

SiO2

Field emission display (FED)

Ding, Silicon Field Emission Arrays With Atomically Sharp Tips: Turn-On Voltage and the Effect of Tip Radius Distribution, 2002.

Oxide Structure

Amorphous tetrahedral network Bridging oxygen Basic structure of silica: a silicon atom tetrahedrally bonds to four oxygen atoms Non-bridging

The structure of silicon-silicon dioxide interface: some silicon atoms have dangling bonds.

Oxide Structure

Single crystal (quartz) 2.65 g/cm3

Amouphous (thermal oxide). 2.21 g/cm3

10

Chapter 6 Thermal oxidation and the Si/SiO2 interface

1. SiO2 properties and applications. 2. Thermal oxidation basics. 3. Manufacturing methods and equipment. 4. Measurement methods. 5. Deal-grove model (linear parabolic model). 6. Thin oxide growth, dependence on gas pressure and crystal orientation 7. Cl-containing gas, 2D growth, substrate doping effect . 8. Interface charges, dopant redistribution.

343 Microfabrication and thin film technology tructor: Bo Cui, ECE, University of Waterloo tbook: Silicon VLSI Technology by Plummer, Deal and Griffin

11

Dry and wet oxidation

Dry oxidation: Si(s) + O2(g) SiO2(s); Wet/steam oxidation: Si(s) + 2H2O(g) Both typically 900-1200C, wet oxidation is about 10 faster than dry SiO2(s) + 2H2(g) oxidation. Dry oxide: thin 0.05-0.5 m, excellent insulator, for gate oxides; for very thin gate oxides, may add nitrogen to form oxynitrides. Wet oxide: thick <2.5 m, good insulator, for field oxides or masking. Quality suffers due to the diffusion of the hydrogen gas out of the film, which creates paths that electrons can follow. Room temperature Si in air creates native oxide: very thin 1-2nm, poor insulator, but can impede surface processing of Si. Volume expansion by 2.2 (=1/0.46), so SiO2 film has compressive stress.

Si wafer

Xox is final oxide thickness

= 0.46

Chapter 6 Thermal oxidation and the Si/SiO2 interface

1. SiO2 properties and applications. 2. Thermal oxidation basics. 3. Manufacturing methods and equipment. 4. Measurement methods. 5. Deal-grove model (linear parabolic model). 6. Thin oxide growth, dependence on gas pressure and crystal orientation 7. Cl-containing gas, 2D growth, substrate doping effect . 8. Interface charges, dopant redistribution.

343 Microfabrication and thin film technology tructor: Bo Cui, ECE, University of Waterloo tbook: Silicon VLSI Technology by Plummer, Deal and Griffin

13

Thermal silicon oxidation methods

A three-tube horizontal furnace with multi-zone temperature control

Wet oxidation using H2 and O2 is more popular (cleaner) than using

Vertical furnace (not popular)

14

Thermal oxidation equipment

The tubular reactor made of quartz or glass, heated by resistance. Oxygen or water vapor flows through the reactor and past the silicon wafers, with a typical velocity of order 1cm/s.

15

Thermal oxidation in practice

1. 2. 3. 4. Clean the wafers (RCA clean, very important) Put wafers in the boat Load the wafers in the furnace Ramp up the furnace to process temperature in N2 (prevents oxidation from occurring) 5. Stabilize 6. Process (wet or dry oxidation) 7. Anneal in N2. Again, nitrogen stops oxidation process. 8. Ramp down

1-

Chapter 6 Thermal oxidation and the Si/SiO2 interface

1. SiO2 properties and applications. 2. Thermal oxidation basics. 3. Manufacturing methods and equipment. 4. Measurement methods (mechanical, optical, electrical). 5. Deal-grove model (linear parabolic model). 6. Thin oxide growth, dependence on gas pressure and crystal orientation 7. Cl-containing gas, 2D growth, substrate doping effect . 8. Interface charges, dopant redistribution.

343 Microfabrication and thin film technology tructor: Bo Cui, ECE, University of Waterloo tbook: Silicon VLSI Technology by Plummer, Deal and Griffin

17

Surface profilometry (Dektak): mechanical thickness measurement Oxide etched away by HF

over part of the wafer and a mechanical stylus is dragged over the resulting step.

Stylus

Mirror image of stylus

stylus

M can also be used for thickness measurement. M: atomic force microscopy)

18

Thickness determination by looking the color

Relative illumination intensity

Film thickness (nm) Oxide thickness for constructive interference (viewed from above =0o) Xo=k /2n, n=1.46, k=1, 2, 3 Our eye can tell the color difference between two films having 10nm 1thickness difference.

Optical thickness measurement: ellipsometry

Lh ig t su e o rc Qa r u rte wv p te a e la

Very accurate (1nm accuracy)

F r ilte P la e o riz r Aa z r n ly e Dte to ecr

F b in ilm e g mau d e s re S btra u s te

After quarter wave plate, the linear polarized light becomes circular polarized, which is incident on the oxide covered wafer. The polarization of the reflected light, which depends on the thickness and refractive index (usually known) of the oxide layer, is determined and used to calculate the oxide thickness. Multiple wavelengths/incident angles can be used to measure thickness/refractive index of each film in a multi-film stack.

20

Electrical thickness measurement: C-V of MOSFET

Small AC voltage is applied on top of the DC voltage for capacitance measurement.

Substrate is N-type. Electron is majority carrier, hole is minority carrier. a.Accumulation: positive gate voltage attracts electrons to the interface. b.Depletion: negative gate bias pushes electrons away from interface. No charge at interface. Two capacitance in series. c.Inversion: further increase

21

Effect of frequency for AC capacitance measuremen

P-type substrate here (previous slide N-type) For low frequency, (minority) charge

At/after inversion:

generation at the interface can follow the AC field to balance the charge at the gate, so Cinv =Cox . For high frequency, the gate charge has to be balanced by the carrier deep below the interface, so Cinv -1 = Cox -1 + CSi -1 . Deep depletion: for high scanning speed (the DC voltage scan fast into large positive voltage), depletion depth Xd must increase to balance Parameter from C-V the gate charge.

measurement: Dielectric constant of Si & SiO2 Capacitor area Oxide thickness Impurity profile in Si Threshold voltage of MOS capacitor

22

https://ece.uwaterloo.ca/~bcui/NE_343.h Bo Cui

Das könnte Ihnen auch gefallen

- Chapter 6 Thermal OxDokument22 SeitenChapter 6 Thermal OxheNoch keine Bewertungen

- Lec 3 Thermal OxidationDokument21 SeitenLec 3 Thermal OxidationVikram MeenaNoch keine Bewertungen

- Q1) "There Is Aplenty of Room at The Bottom",by Feynman: Method 1Dokument7 SeitenQ1) "There Is Aplenty of Room at The Bottom",by Feynman: Method 1Gopinath ChakrabortyNoch keine Bewertungen

- Nmos and Cmos FabricationDokument33 SeitenNmos and Cmos FabricationmannsloveNoch keine Bewertungen

- 3 Thermal Oxidation PDFDokument37 Seiten3 Thermal Oxidation PDFGaurav SumanNoch keine Bewertungen

- EE2254 LIC 2marks 2013Dokument16 SeitenEE2254 LIC 2marks 2013sivagamiNoch keine Bewertungen

- MOS Fabrication Technology: Abstract This Chapter Is Concerned With The Fabrication of Metal-Oxide-SemiconductorDokument7 SeitenMOS Fabrication Technology: Abstract This Chapter Is Concerned With The Fabrication of Metal-Oxide-SemiconductorsammyNoch keine Bewertungen

- Chapter 9 Thin Film DepositionDokument42 SeitenChapter 9 Thin Film DepositionMayank MahajanNoch keine Bewertungen

- A Teacher-Student Conversation On "Cmos Fabrication Process Flow"Dokument70 SeitenA Teacher-Student Conversation On "Cmos Fabrication Process Flow"Calcutta University RPE 2020Noch keine Bewertungen

- EEE-489 L4T2 16eee Class-1Dokument16 SeitenEEE-489 L4T2 16eee Class-1Anurag OviNoch keine Bewertungen

- Course Title: VLSI Technology Course No.: EEE 489Dokument25 SeitenCourse Title: VLSI Technology Course No.: EEE 489Rubel RiadNoch keine Bewertungen

- Vlsi Design: Prepared Prepared Prepared Prepared by by by byDokument30 SeitenVlsi Design: Prepared Prepared Prepared Prepared by by by byVenkata SatishNoch keine Bewertungen

- C-1 CMOS Processing FlowDokument76 SeitenC-1 CMOS Processing FlowKu Ble YanNoch keine Bewertungen

- CM - MEMS - TWO MARKS Five UNITSDokument7 SeitenCM - MEMS - TWO MARKS Five UNITSSandhiyaNoch keine Bewertungen

- Unit - IDokument69 SeitenUnit - IsaravananNoch keine Bewertungen

- Ee2254 Lica QBDokument0 SeitenEe2254 Lica QBnjparNoch keine Bewertungen

- Bipolar IC ProcessDokument5 SeitenBipolar IC Processlachuns123Noch keine Bewertungen

- Ic FabricationDokument7 SeitenIc FabricationphooolNoch keine Bewertungen

- Eem413e Lecture-Week4Dokument47 SeitenEem413e Lecture-Week4Furkan AvcıoğluNoch keine Bewertungen

- Prospects For Sic Electronics and Sensors: N.G.Wright@Ncl - Ac.UkDokument6 SeitenProspects For Sic Electronics and Sensors: N.G.Wright@Ncl - Ac.UkDaniel MorenoNoch keine Bewertungen

- JSS 1 (2012) P90Dokument5 SeitenJSS 1 (2012) P90Chomsatin AmaliaNoch keine Bewertungen

- Vlsi FabDokument8 SeitenVlsi FabhaheNoch keine Bewertungen

- Chapter 6 Thermal Oxidation - IIIDokument26 SeitenChapter 6 Thermal Oxidation - IIIAniket SujayNoch keine Bewertungen

- Unit 1Dokument66 SeitenUnit 1srgperumalNoch keine Bewertungen

- Presentation 1 LicDokument28 SeitenPresentation 1 LicreporterrajiniNoch keine Bewertungen

- 05-ICT-ox PrintableDokument39 Seiten05-ICT-ox PrintableCyrille MagdiNoch keine Bewertungen

- EC1313 Two Marks Linear Integrated CircuitsDokument11 SeitenEC1313 Two Marks Linear Integrated Circuitsmoney_kandan2004Noch keine Bewertungen

- Final Report-1Dokument5 SeitenFinal Report-1ISANI VENKATESHWAR REDDY 210146265Noch keine Bewertungen

- Unit I Ic FabricationDokument23 SeitenUnit I Ic FabricationBhuvana VaradharajNoch keine Bewertungen

- Fabricating A Nano-Labyrinth On Silicon Wafer: Project ReportDokument15 SeitenFabricating A Nano-Labyrinth On Silicon Wafer: Project ReportEthan HuntNoch keine Bewertungen

- VLSI Unit 2 Technology - SDokument52 SeitenVLSI Unit 2 Technology - SIndrajeet GautamNoch keine Bewertungen

- M Group: Linear Integrated Circuits (Ec1313) IC FabricationDokument17 SeitenM Group: Linear Integrated Circuits (Ec1313) IC Fabricationscribdm100% (1)

- Fabrication of NMOS TransistorDokument11 SeitenFabrication of NMOS TransistorYogesh TiwariNoch keine Bewertungen

- Thin Dielectric Layers Characterization Using Corona-Oxide-Semiconductor Measurement TechniqueDokument54 SeitenThin Dielectric Layers Characterization Using Corona-Oxide-Semiconductor Measurement TechniqueTejpreet Singh BediNoch keine Bewertungen

- Television 13 FebDokument14 SeitenTelevision 13 FebriponkumarNoch keine Bewertungen

- Solar Cell Fabrication Lab: Final ReportDokument8 SeitenSolar Cell Fabrication Lab: Final ReportPrateek SinghNoch keine Bewertungen

- CMOS TechnologiesDokument27 SeitenCMOS TechnologiesDebela TesfayeNoch keine Bewertungen

- CMOS Processing Technology Silicon: A Semiconductor With Resistance Between That of Conductor and AnDokument18 SeitenCMOS Processing Technology Silicon: A Semiconductor With Resistance Between That of Conductor and AntmdmurthyNoch keine Bewertungen

- Lecture2 MicroFabTechniques PDFDokument10 SeitenLecture2 MicroFabTechniques PDFdiNoch keine Bewertungen

- Processing of DevicesDokument31 SeitenProcessing of DevicesBituNoch keine Bewertungen

- RF Sputtering: A Viable Tool For MEMS Fabrication: Sudhir Chandra, Vivekanand Bhatt and Ravindra SinghDokument14 SeitenRF Sputtering: A Viable Tool For MEMS Fabrication: Sudhir Chandra, Vivekanand Bhatt and Ravindra SinghPhạm Việt DũngNoch keine Bewertungen

- Quantum Dot Arrays in Silicon and GermaniumDokument9 SeitenQuantum Dot Arrays in Silicon and GermaniumAram ShojaeiNoch keine Bewertungen

- Pip 3244Dokument7 SeitenPip 3244Riski RamadaniNoch keine Bewertungen

- Characterization of SOI PMOSFET Using Silvaco TCAD ToolsDokument7 SeitenCharacterization of SOI PMOSFET Using Silvaco TCAD ToolseditorijaiemNoch keine Bewertungen

- EE432/EE532 Microelectronic Fabrication Techniques: Final Lab ReportDokument28 SeitenEE432/EE532 Microelectronic Fabrication Techniques: Final Lab Reportapi-546410997Noch keine Bewertungen

- ReportDokument8 SeitenReportROMANCE FantasNoch keine Bewertungen

- Transparent Conducting Zno:Al Films Via CCVD For Amorphous Silicon Solar CellsDokument4 SeitenTransparent Conducting Zno:Al Films Via CCVD For Amorphous Silicon Solar CellsEidelsayedNoch keine Bewertungen

- Semiconductor Device Fabrication (Chapter 9)Dokument13 SeitenSemiconductor Device Fabrication (Chapter 9)Hasi De RustafariNoch keine Bewertungen

- Notes NewDokument14 SeitenNotes NewPriya SirsatNoch keine Bewertungen

- Fabrication of Silicon Based Glass Fibres For Optical CommunicationDokument5 SeitenFabrication of Silicon Based Glass Fibres For Optical Communicationkhaled loteesNoch keine Bewertungen

- MPM144 13 SakharovDokument6 SeitenMPM144 13 SakharovВадим АрыковNoch keine Bewertungen

- Week 4 - EMIDokument10 SeitenWeek 4 - EMIMuhammad ShahzaibNoch keine Bewertungen

- InTech-Chasing High Efficiency DSSC by Nano Structural Surface Engineering at Low Processing Temperature For Titanium Dioxide ElectrodesDokument19 SeitenInTech-Chasing High Efficiency DSSC by Nano Structural Surface Engineering at Low Processing Temperature For Titanium Dioxide ElectrodesDeva RajNoch keine Bewertungen

- Reaction Analysis of Initial Oxidation of Silicon by Uv-Light-Excited Ozone and The Application To Rapid and Uniform Sio2 Film GrowthDokument8 SeitenReaction Analysis of Initial Oxidation of Silicon by Uv-Light-Excited Ozone and The Application To Rapid and Uniform Sio2 Film GrowthAmitNoch keine Bewertungen

- Integrated Circuit Fabrication ProcessDokument14 SeitenIntegrated Circuit Fabrication ProcessSanthosh DheerajNoch keine Bewertungen

- Thin Film DepositionDokument42 SeitenThin Film DepositionNguyên Đỗ DuyNoch keine Bewertungen

- Plasma Etching Processes for Interconnect Realization in VLSIVon EverandPlasma Etching Processes for Interconnect Realization in VLSINicolas PossemeNoch keine Bewertungen

- Tema Cls 6 B Pentru 19 Ian 2021Dokument2 SeitenTema Cls 6 B Pentru 19 Ian 2021sbotacondNoch keine Bewertungen

- Exercitii CapitaleDokument3 SeitenExercitii CapitalesbotacondNoch keine Bewertungen

- PETDokument5 SeitenPETAndreea AlexeNoch keine Bewertungen

- Art 2013 Anale UGAL TemporalDokument6 SeitenArt 2013 Anale UGAL TemporalsbotacondNoch keine Bewertungen

- PETDokument5 SeitenPETAndreea AlexeNoch keine Bewertungen

- Passive - Pag. 1Dokument1 SeitePassive - Pag. 1sbotacondNoch keine Bewertungen

- 4850866-Carol of The BellsDokument2 Seiten4850866-Carol of The BellssbotacondNoch keine Bewertungen

- Cinquain Poem Directions PlannerDokument3 SeitenCinquain Poem Directions PlannerMinetteNoch keine Bewertungen

- Introduction To Energy Dispersive X-Ray Spectrometry (EDS) : 1.1 Principles of The TechniqueDokument11 SeitenIntroduction To Energy Dispersive X-Ray Spectrometry (EDS) : 1.1 Principles of The TechniqueFitriani AhmadNoch keine Bewertungen

- Ice Measuring TutorialDokument115 SeitenIce Measuring TutorialsbotacondNoch keine Bewertungen

- Terra V Nationala 2014 SubiecteDokument1 SeiteTerra V Nationala 2014 SubiectesbotacondNoch keine Bewertungen

- Environmental Impacts of NanotechnologyDokument21 SeitenEnvironmental Impacts of NanotechnologysbotacondNoch keine Bewertungen

- Engineering Physics Sem - 1Dokument349 SeitenEngineering Physics Sem - 1Andrew NelsonNoch keine Bewertungen

- Colinde Craciun EnglezaDokument1 SeiteColinde Craciun Englezasbotacond100% (2)

- Articol PIGMENTI 5Dokument6 SeitenArticol PIGMENTI 5sbotacondNoch keine Bewertungen

- Colinde Craciun EnglezaDokument1 SeiteColinde Craciun Englezasbotacond100% (2)

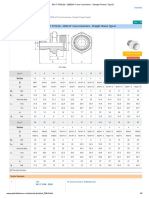

- GB - T 3733 (B) - 200824° Cone Connectors - Straight Thread, Type BDokument3 SeitenGB - T 3733 (B) - 200824° Cone Connectors - Straight Thread, Type BEr.Amritpal SinghNoch keine Bewertungen

- E8500 Manual PDFDokument45 SeitenE8500 Manual PDFAnggaraPerbawaPutraNoch keine Bewertungen

- Stepper Principle Prezentare Power PointDokument15 SeitenStepper Principle Prezentare Power PointPetrovai AlexandruNoch keine Bewertungen

- User manual-BMC-Highflow Series MachineDokument50 SeitenUser manual-BMC-Highflow Series MachineСергей Букша100% (1)

- "Smart Dustbin Using Arduino": Maharashtra State Board of Technical Education, MumbaiDokument22 Seiten"Smart Dustbin Using Arduino": Maharashtra State Board of Technical Education, MumbaiEr Dinesh TambeNoch keine Bewertungen

- Resistance Start Split Phase Induction MotorDokument32 SeitenResistance Start Split Phase Induction Motorrockingsandy100% (1)

- User's Manual of Haiwell Classic PLC C and T Series MPUDokument6 SeitenUser's Manual of Haiwell Classic PLC C and T Series MPUZubair AfzalNoch keine Bewertungen

- On The Spot Courier Services Business ReportDokument7 SeitenOn The Spot Courier Services Business Reportapi-253540656Noch keine Bewertungen

- 通訊原理Dokument303 Seiten通訊原理ZenPhiNoch keine Bewertungen

- Flexible Ac Transmission Systems (Facts) - Full Paper Presentation - Eeerulez - BlogspotDokument20 SeitenFlexible Ac Transmission Systems (Facts) - Full Paper Presentation - Eeerulez - Blogspotbhupathirakesh100% (11)

- Vibration Signal Analysis PDFDokument11 SeitenVibration Signal Analysis PDFmicky1389Noch keine Bewertungen

- Electrical Loading Estimation WorkstageDokument15 SeitenElectrical Loading Estimation WorkstageansonchongNoch keine Bewertungen

- ADG1406bruz 1407Dokument20 SeitenADG1406bruz 1407Sebastian BryceNoch keine Bewertungen

- LEvitonDokument2 SeitenLEvitonAndres Barbosa LargoNoch keine Bewertungen

- PRB Belt XRef PDFDokument283 SeitenPRB Belt XRef PDFBrian RichmondNoch keine Bewertungen

- Application Guidelines MEEPEDokument2 SeitenApplication Guidelines MEEPEavionicsnabinNoch keine Bewertungen

- Overlapping Contact 800t Td006 en PDokument8 SeitenOverlapping Contact 800t Td006 en PDony SaputraNoch keine Bewertungen

- Chauvin Arnoux 8350Dokument56 SeitenChauvin Arnoux 8350Marc PettyNoch keine Bewertungen

- Air Flow SensorDokument23 SeitenAir Flow SensorRinus ZoetebierNoch keine Bewertungen

- Camera Lock Catalog-MinDokument55 SeitenCamera Lock Catalog-MinAlex BrasfeltNoch keine Bewertungen

- VCB SpecificationDokument19 SeitenVCB SpecificationprashantNoch keine Bewertungen

- Pages From Washer Dryer MeralcoDokument1 SeitePages From Washer Dryer MeralcoLEON SOTNASNoch keine Bewertungen

- Ir155-4210-V004 D00377 D Xxen PDFDokument6 SeitenIr155-4210-V004 D00377 D Xxen PDFNuno Castro PereiraNoch keine Bewertungen

- Owner's Manual: The Tone Hammer Preamp/DiDokument4 SeitenOwner's Manual: The Tone Hammer Preamp/DiflexlopezNoch keine Bewertungen

- Plugin Interface For Flash and HTML5Dokument30 SeitenPlugin Interface For Flash and HTML5tatt2Noch keine Bewertungen

- Contain CeDokument4 SeitenContain CenageshNoch keine Bewertungen

- Signal Chain Design GuideDokument20 SeitenSignal Chain Design GuideLi OuyangNoch keine Bewertungen

- Solution Manual For Principles and AppliDokument64 SeitenSolution Manual For Principles and AppliWellin Sambo100% (1)

- Highly Efficient Design of Microwave Circuits: Brad Brim Applications Engineer, Ansoft CorpDokument44 SeitenHighly Efficient Design of Microwave Circuits: Brad Brim Applications Engineer, Ansoft CorpEnSon ChangNoch keine Bewertungen

- Windows Shell Command To Uninstall in Built Microsoft Store Apps PDFDokument7 SeitenWindows Shell Command To Uninstall in Built Microsoft Store Apps PDFenakta13Noch keine Bewertungen