Beruflich Dokumente

Kultur Dokumente

VHDL T-Bistabil

Hochgeladen von

leddannyOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

VHDL T-Bistabil

Hochgeladen von

leddannyCopyright:

Verfügbare Formate

--T bistabil s Q i Q' izlazima i mogucnoscu set-a library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.

ALL; entity auditorne is port( T,CP,SET:in std_logic; Q,Qn:out std_logic); end auditorne; architecture Behavioral of auditorne is type stanje is(S0,S1); signal sad_stanje,sljed_stanje:stanje; signal temp:std_logic; begin process(CP,SET) begin if(SET='1')then sad_stanje<=S1; elsif(CP'event and CP='1')then sad_stanje<=sljed_stanje; --ovo je s asinkronim set, ako bi htjeli sinkroni set, prvo bi r adili provjeru CP'event, a zatim, unutar nje bi radili provjeru SET='1'. --Shvatili? Da? Ne? end if; end process; process(sad_stanje,T) begin case sad_stanje is when S0=> temp<='0'; if(T='1')then sljed_stanje<=S1; end if; when S1=> temp<='1'; if(T='1')then sljed_stanje<=S0; end if; end case; end process; Q<=temp; Qn<=not temp; end Behavioral;

Das könnte Ihnen auch gefallen

- Automatisierungstechnik SkriptDokument92 SeitenAutomatisierungstechnik Skriptorinoco963Noch keine Bewertungen

- Modul 4Dokument16 SeitenModul 4Annisa AzzahraNoch keine Bewertungen

- Emd Reg 2013Dokument6 SeitenEmd Reg 2013chabaneoukaci58Noch keine Bewertungen

- 004627.00 Quick Guide LabSwift Aw DDokument2 Seiten004627.00 Quick Guide LabSwift Aw Dmoriz52Noch keine Bewertungen

- FDLC Prac7Dokument7 SeitenFDLC Prac7Ankit BhardwajNoch keine Bewertungen

- CNS PracDokument33 SeitenCNS PracBhavin ViraniNoch keine Bewertungen

- Ergebnisse DrosselklappöDokument2 SeitenErgebnisse DrosselklappömaunzyNoch keine Bewertungen

- Skript (Komplett)Dokument139 SeitenSkript (Komplett)Vu Thanh Hai PhamNoch keine Bewertungen

- Grundlagen Technischer Informatik Klausur Mit LoesungDokument15 SeitenGrundlagen Technischer Informatik Klausur Mit LoesungAnonymous gWTW7xsNoch keine Bewertungen

- 4 AxdrehDokument8 Seiten4 AxdrehMIguel Angel CorralesNoch keine Bewertungen

- Hisham M M Almadhoun 11160439: 1-Print ("Hello World!") Hello World!Dokument6 SeitenHisham M M Almadhoun 11160439: 1-Print ("Hello World!") Hello World!Hisham AlmadhounNoch keine Bewertungen

- Fse1 HackerrankDokument13 SeitenFse1 Hackerranklakshmi narayana reddyNoch keine Bewertungen

- KryptographieDokument4 SeitenKryptographieMNoch keine Bewertungen

- Robotik EinführungDokument39 SeitenRobotik Einführungxpedo007100% (1)

- BASCOM Tutorial 3Dokument5 SeitenBASCOM Tutorial 3alexNoch keine Bewertungen

- 4 Digits 7 Segment Display DEDokument16 Seiten4 Digits 7 Segment Display DEcmdiNoch keine Bewertungen

- ÜbungssammlungDokument5 SeitenÜbungssammlungDaniel HentzenNoch keine Bewertungen

- PID-Regler: Kompendium Simulation und Regelung technischer Prozesse, Teil 10Von EverandPID-Regler: Kompendium Simulation und Regelung technischer Prozesse, Teil 10Noch keine Bewertungen

- HC-SR04 Ultraschallmodul DEDokument14 SeitenHC-SR04 Ultraschallmodul DEtimtomtheoNoch keine Bewertungen

- 02 UebungDeadlocksDokument4 Seiten02 UebungDeadlocksVanelle leslie HappiNoch keine Bewertungen

- Rege Lungs Technik Skrip TDokument47 SeitenRege Lungs Technik Skrip Ttariq mahfoudNoch keine Bewertungen

- An 01 de Digitales Temperatur ZeitmodulDokument6 SeitenAn 01 de Digitales Temperatur Zeitmodulrommel9645Noch keine Bewertungen

- ANTENADokument8 SeitenANTENAluminance1Noch keine Bewertungen

- Grundlegende SchaltungenDokument23 SeitenGrundlegende Schaltungengoodsweater100% (1)

- Oliver Nelles - Regelungstechnik-Universität Siegen (2018) PDFDokument642 SeitenOliver Nelles - Regelungstechnik-Universität Siegen (2018) PDFberija1968Noch keine Bewertungen

- 4-Relais Modul - DEDokument10 Seiten4-Relais Modul - DEtimtomtheoNoch keine Bewertungen

- BASCOM Tutorial 2Dokument5 SeitenBASCOM Tutorial 2Sultan FikriNoch keine Bewertungen

- BS - Probeklausur - 2017Dokument5 SeitenBS - Probeklausur - 2017danik2002zNoch keine Bewertungen

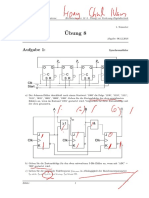

- U8 PDFDokument5 SeitenU8 PDFHong Chul NamNoch keine Bewertungen

- Arduino Interrupt Steuer Ung Teil 1Dokument16 SeitenArduino Interrupt Steuer Ung Teil 1Amar Amôur100% (2)

- Errores RSV 08Dokument119 SeitenErrores RSV 08Johan ZraghozNoch keine Bewertungen

- DrehschalterDokument8 SeitenDrehschaltertimtomtheoNoch keine Bewertungen

- TP 2-1Dokument3 SeitenTP 2-1Ahmed AmirNoch keine Bewertungen

- CSharp Powerworkshop BASTA Spring 2013 - Rainer Stropek PDFDokument76 SeitenCSharp Powerworkshop BASTA Spring 2013 - Rainer Stropek PDFAlexandre Rocha Lima e MarcondesNoch keine Bewertungen

- BA 3WL9111-0AT44-0AA0 Stand0511Dokument27 SeitenBA 3WL9111-0AT44-0AA0 Stand0511Ho Jun XianNoch keine Bewertungen

- KI Referat Evolutionäres LernenDokument3 SeitenKI Referat Evolutionäres Lernenbababa2aNoch keine Bewertungen

- Arbeitsverfahren MotorDokument16 SeitenArbeitsverfahren MotorMaximilian BojcumNoch keine Bewertungen

- BASCOM WatchdogDokument1 SeiteBASCOM WatchdogalexNoch keine Bewertungen

- Störk ST72-30.04Dokument14 SeitenStörk ST72-30.04Jörg WulffNoch keine Bewertungen

- Preciado, Paul Beatriz - Kontrasexuelles Manifest-KomprimiertDokument37 SeitenPreciado, Paul Beatriz - Kontrasexuelles Manifest-KomprimiertBen GrafNoch keine Bewertungen

- Easy AppDokument43 SeitenEasy AppLuisRubioLopezNoch keine Bewertungen

- DSPIC30f2010 C-Code SanjayDokument16 SeitenDSPIC30f2010 C-Code SanjayScribdTranslationsNoch keine Bewertungen

- Exercise Details (Dragged)Dokument3 SeitenExercise Details (Dragged)fnewiufnoiewNoch keine Bewertungen

- Manual Zelio AlemanDokument86 SeitenManual Zelio AlemanTimoty AvilaNoch keine Bewertungen

- KDG 1Dokument10 SeitenKDG 1Atef NazNoch keine Bewertungen

- Aktiver Tastkopf Mit OPA659Dokument72 SeitenAktiver Tastkopf Mit OPA659Jaroslav BiresNoch keine Bewertungen

- SPS Technik AnkreuzaufgabeDokument3 SeitenSPS Technik AnkreuzaufgabeAxel GroßmannNoch keine Bewertungen

- 2 VersuchDokument38 Seiten2 VersuchJuan Nicolas Pardo MartinNoch keine Bewertungen

- Sprachelemente Von C-SharpDokument34 SeitenSprachelemente Von C-SharpMaximilian KalachnikovNoch keine Bewertungen

- Router 1x3 REPORT1Dokument59 SeitenRouter 1x3 REPORT1Yashwanth SNoch keine Bewertungen

- Pulsar DeuDokument26 SeitenPulsar DeujweingrillNoch keine Bewertungen

- SDRT I Klausur F14 - MusterlösungDokument16 SeitenSDRT I Klausur F14 - MusterlösungdjhousecatNoch keine Bewertungen

- Digitale Regelung-AbtastzeitDokument26 SeitenDigitale Regelung-AbtastzeitMona ValikhaniNoch keine Bewertungen

- Prüfung Grundlagen Der Regelungstechnik WS 07/08: Name, Vorname: MatrikelnummerDokument17 SeitenPrüfung Grundlagen Der Regelungstechnik WS 07/08: Name, Vorname: MatrikelnummerSSdSSNoch keine Bewertungen

- Taschenrechner IndexDokument3 SeitenTaschenrechner IndexHadeel AzadNoch keine Bewertungen