100% fanden dieses Dokument nützlich (1 Abstimmung)

435 Ansichten8 SeitenFragenkatalog Mit Antworten

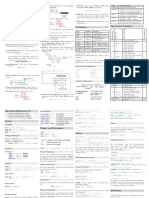

Das Dokument beschreibt grundlegende Konzepte von Computern wie RISC und CISC Architekturen, Compiler und Interpreter, die von Neumann Architektur sowie Caches und Speicherhierarchien. Es erklärt auch Konzepte wie Pipelining, Hazards und Verdrängungsstrategien für Caches.

Hochgeladen von

Anonymous LblPe92BvMCopyright

© © All Rights Reserved

Wir nehmen die Rechte an Inhalten ernst. Wenn Sie vermuten, dass dies Ihr Inhalt ist, beanspruchen Sie ihn hier.

Verfügbare Formate

Als ODT, PDF, TXT herunterladen oder online auf Scribd lesen

100% fanden dieses Dokument nützlich (1 Abstimmung)

435 Ansichten8 SeitenFragenkatalog Mit Antworten

Das Dokument beschreibt grundlegende Konzepte von Computern wie RISC und CISC Architekturen, Compiler und Interpreter, die von Neumann Architektur sowie Caches und Speicherhierarchien. Es erklärt auch Konzepte wie Pipelining, Hazards und Verdrängungsstrategien für Caches.

Hochgeladen von

Anonymous LblPe92BvMCopyright

© © All Rights Reserved

Wir nehmen die Rechte an Inhalten ernst. Wenn Sie vermuten, dass dies Ihr Inhalt ist, beanspruchen Sie ihn hier.

Verfügbare Formate

Als ODT, PDF, TXT herunterladen oder online auf Scribd lesen